NOR Gate S-R Latch

零件和材料

- 4001 四或非门(Radio Shack 目录号 #276-2401)

- 八位 DIP 开关(Radio Shack 目录编号 275-1301)

- 十段条形图 LED(Radio Shack 目录 # 276-081)

- 一节 6 伏电池

- 两个 10 kΩ 电阻器

- 两个 470 Ω 电阻器

- 两个 100 Ω 电阻器

注意! 4001 IC是CMOS,对静电很敏感!

交叉引用

电路课程 ,第 4 卷,第 3 章:“逻辑门”

电路课程 ,第 4 卷,第 10 章:“多谐振荡器”

学习目标

- 了解正反馈在数字电路中的作用

- 锁存电路的“无效”状态是什么意思

- 什么是竞争条件 在数字电路中

- 了解有效的“高”CMOS 信号电压电平的重要性

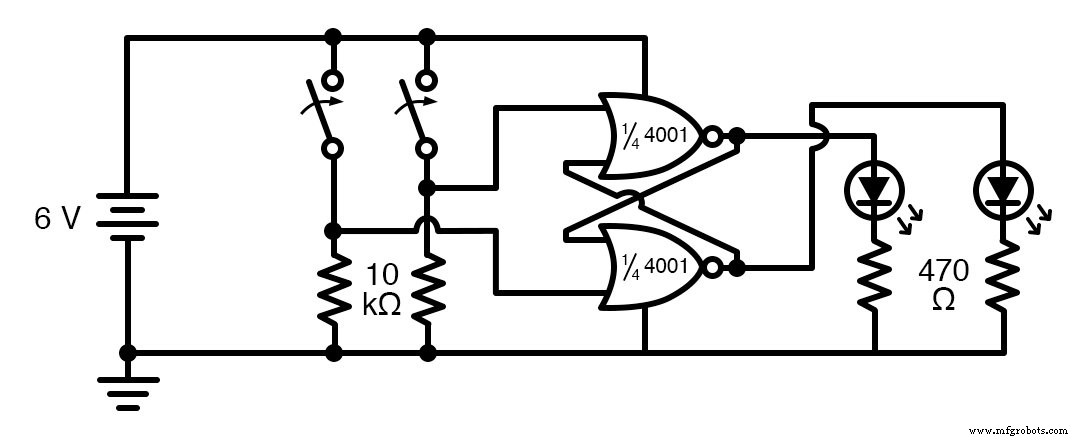

原理图

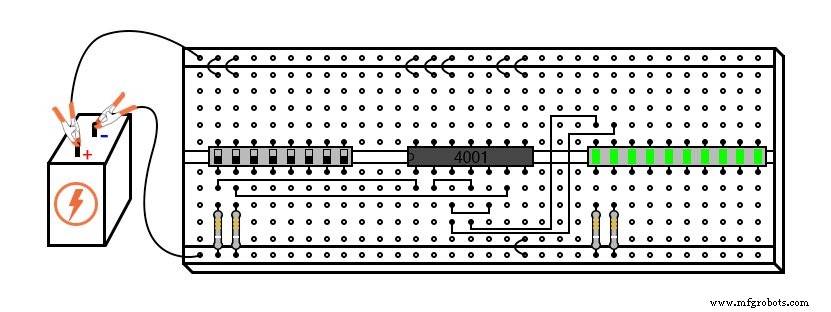

插图

说明

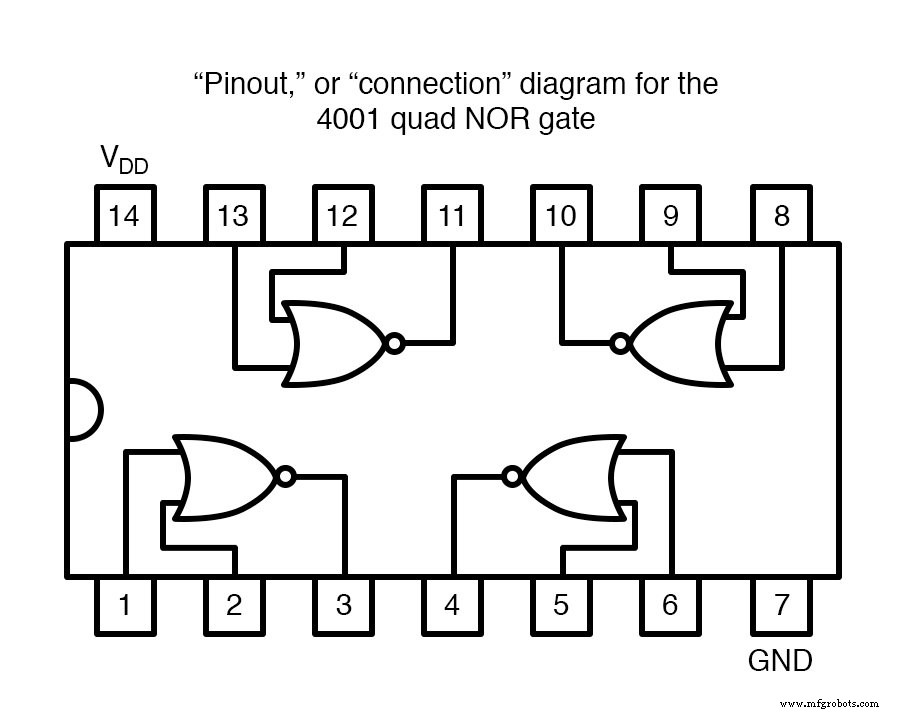

4001 集成电路是一个 CMOS 四与非门,在输入、输出和电源引脚分配方面与 4011 四与非门相同。它的“引脚排列”或“连接”图如下所示:

当两个或非门如图所示交叉连接时,从输出到输入会有正反馈。也就是说,输出信号倾向于将门保持在其最后的输出状态。就像在运算放大器电路中一样,正反馈会产生迟滞 .

电路保持在其最后输出状态的这种趋势给了它一种“记忆”。事实上,基于这样的电路的固态计算机内存技术是存在的!

如果我们将左侧开关指定为“Set”输入,右侧开关指定为“Reset”,则左侧 LED 将是“Q”输出,右侧 LED 将是“Q-not”输出。当设置输入为“高”(打开)和复位输入为“低”时,Q 将变为“高”,而 Q-not 将变为“低”。

这被称为 set 电路的状态。使复位输入“高”和设置输入“低”反转锁存电路的输出状态:Q“低”和 Q-非“高”。这被称为重置 电路的状态。如果两个输入都被置于“低”状态,电路的 Q 和 Q-not 输出将保持在最后的状态,“记住”它们之前的设置。这被称为闩锁 电路状态。

因为输出被指定为“Q”和“Q-not”,这意味着它们的状态将始终是互补的(相反)。因此,如果发生某些事情迫使两个输出相同 状态,我们倾向于称该电路模式为“无效”。

如果我们将置位和复位输入都设置为“高”,这正是会发生的情况:Q 和 Q-not 输出都将被强制为相同的“低”逻辑状态。这被称为无效 或非法 电路状态,不是因为出现问题,而是因为输出未能满足其标签确定的预期。

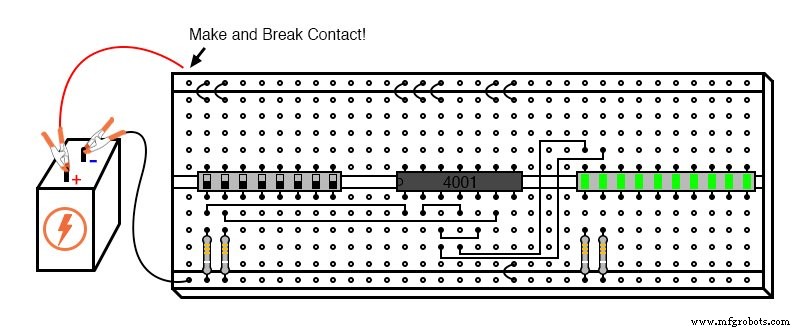

由于“锁定”状态是一种迟滞状态,其中最后的输出状态被“记住”,人们可能想知道如果电路以这种方式上电会发生什么,没有先前的状态可以保持 .要进行实验,请将两个开关置于关闭位置,将 Set 和 Reset 输入设为低电平,然后断开其中一根电池线与面包板的连接。

然后,快速建立和断开电池线与其在面包板上的正确连接点之间的接触,并在电路一次又一次通电时注意两个 LED 的状态:

当像这样的锁存电路通电进入“锁存”状态时,门会相互竞争以进行控制。给定“低”输入,两个门都尝试输出“高”信号。如果其中一个门在另一个之前达到其“高”输出状态,则该“高”状态将反馈到另一个门的输入以强制其输出为“低”,而较快的门将赢得比赛。

由于芯片中栅极之间的内部差异,和/或外部电阻和电容导致一个栅极的延迟时间大于另一个栅极,因此一个栅极总是会赢得竞赛。这通常意味着电路倾向于以相同的模式一遍又一遍地加电。但是,如果您坚持通电/断电周期,您应该至少看到几次锁存电路上电锁定在相反 正常状态。

竞争条件在任何类型的系统中都是不可取的,因为它们会导致不可预测的操作。正如本实验所示,由于它们产生的不可预测性,定位它们可能特别麻烦。想象一下,例如,由于芯片缺陷,两个或非门中的一个动作异常缓慢。

这个差点会导致另一个门每次都赢得加电比赛。换句话说,在两个输入“低”的情况下,该电路在上电时将是非常可预测的。但是,假设不寻常的芯片将被具有更均匀匹配的门的芯片替换,或者被具有其他 或非门始终较慢。

更换组件时正常电路行为不应该改变,但如果存在竞争条件,则更换组件很可能会发生这种情况。

由于 SR 锁存器的内在竞争趋势,人们不应该设计具有一致上电状态的电路,而应使用外部手段“强制”竞争,以便所需的门总是“获胜”。

在该电路中尝试进行的一项有趣修改是将 470 Ω LED“下降”电阻器中的一个替换为较低值的单元,例如 100 Ω。这种改变的明显效果将增加 LED 亮度,因为允许更多的电流通过。

也会产生不那么明显的效果,而正是这种效果具有很大的学习价值。尝试用 100 Ω 电阻器替换 470 Ω 电阻器之一,并通过所有四种可能的设置组合操作输入信号开关,注意电路的行为。

您应该注意,当输入开关都设置为“低”(“锁存”模式)时,电路拒绝锁存其一种状态(设置或复位),而只会锁存另一种状态。为什么是这样?拿一个电压表测量当两个输入都为“低”时输出“高”的门的输出电压。

注意这个电压指示,然后设置输入开关,使other 状态(复位或设置)被强制,并在其输出为“高”时测量另一个门的输出电压。请注意两个栅极输出电压电平之间的差异,一个栅极由具有 470 Ω 电阻的 LED 加载,另一个由具有 100 Ω 电阻的 LED 加载。

由“较重”负载(100 Ω 电阻器)加载的负载会小得多:比这个电压低得多的电压不会被另一个 NOR 门的输入解释为“高”信号,因为它被反馈了!所有逻辑门都有允许的“高”和“低”输入信号电压范围,如果数字信号的电压超出这个允许范围,接收门可能无法正确解释。

在像这样的锁存电路中,它依赖于从一个门的输出反馈到另一个门的输入的稳定“高”信号,“弱”信号将无法保持保持正反馈所需的正反馈电路锁存于其中一种状态。

这就是我喜欢使用电压表作为确定数字信号电平的逻辑“探头”,而不是具有“高”和“低”灯的实际逻辑探头的原因之一。逻辑探头可能不会指示“弱”信号的存在,而电压表肯定会通过其定量指示。

这种类型的问题在混合不同“系列”集成电路(例如 TTL 和 CMOS)的电路中很常见,只有通过提供信号电平定量测量的测试设备才能发现。

工业技术