TTL NOR 和 OR 门

TTL电路分析

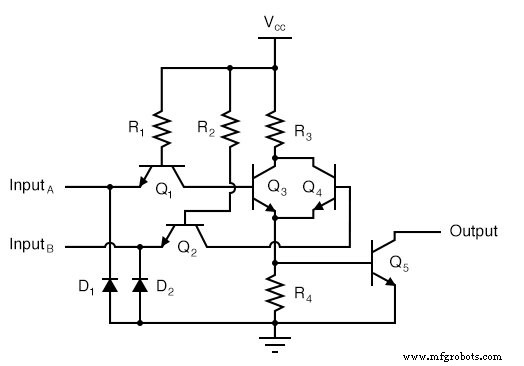

让我们检查以下 TTL 电路并分析其操作:

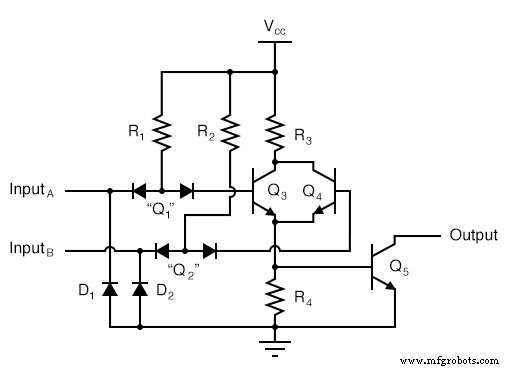

晶体管 Q1 和 Q2 的排列方式与我们在所有其他 TTL 电路中看到的晶体管 Q1 的排列方式相同。 Q1 和 Q2 都用作双二极管“控制”网络,而不是用作放大器。我们可以用二极管组替换 Q1 和 Q2 以帮助说明:

如果输入 A 悬空(或连接到 Vcc),电流将通过晶体管 Q3 的基极,使其饱和。如果输入 A 接地,则该电流通过“Q1”的左转向二极管从 Q3 的基极转移,从而迫使 Q3 截止。输入 B 和晶体管 Q4 也可以这样说:输入 B 的逻辑电平决定 Q4 的导通:饱和或截止。

请注意晶体管 Q3 和 Q4 如何在其集电极和发射极端子上并联。本质上,这两个晶体管充当并联开关,根据输入 A 和 B 的逻辑电平允许电流通过电阻器 R3 和 R4。如果 any 输入处于“高” (1) 电平,那么两个晶体管(Q3 和/或 Q4)中的至少一个将饱和,允许电流通过电阻器 R3 和 R4,并打开最终输出晶体管 Q5 以“低” (0) 逻辑电平输出。该电路的输出可以呈现“高”(1) 状态的唯一方法是如果两者 Q3 和 Q4 被切断,这意味着两者 输入必须接地,或“低”(0)。

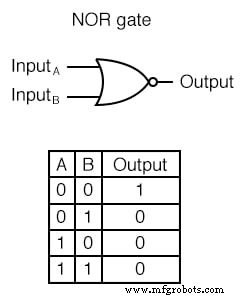

或非门真值表

那么,这个电路的真值表就等价于或非门的真值表:

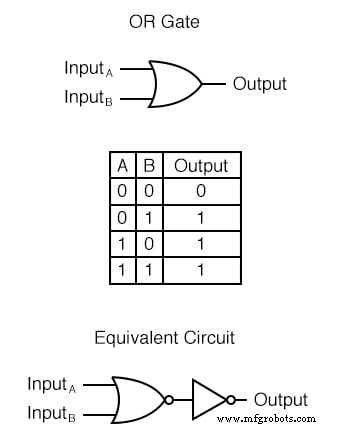

将或非门TTL电路转换为或门

为了将这个 NOR 门电路变成 OR 门,我们必须用另一个晶体管级反转输出逻辑电平,就像我们在 NAND-to-AND 门示例中所做的那样:

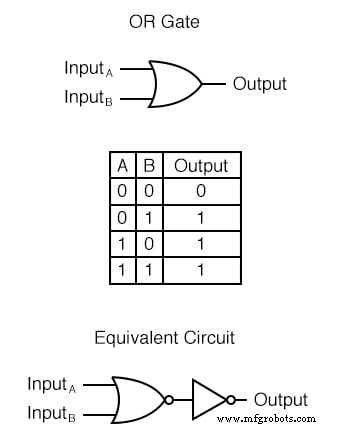

或门真值表

真值表和等效门电路(反相输出或非门)如下所示:

当然,在NOR和OR TTL逻辑电路中也可以使用图腾柱输出级。

评论:

- 可以通过向或非门电路的输出添加一个反相器级来创建或门。

工业技术