谐振电路的 Q 因数和带宽

谐振电路的 Q 或质量因数是对谐振电路“好坏”或质量的衡量。该品质因数的较高值对应于更窄的带宽,这在许多应用中是可取的。更正式地说,Q 分别是电路电抗和电阻中存储的功率与耗散的功率之比:

Q =Pstored/Pdissipated =I 2 X/I 2 R Q =X/R 其中: X =谐振时的容抗或感抗 R =串联电阻。

该公式适用于串联谐振电路,也适用于电阻与电感串联的并联谐振电路。在实际应用中就是这种情况,因为我们最关心的是限制 Q 的电感器的电阻。

注意: 一些文本可能会显示 X 和 R 在并联谐振电路的“Q”公式中互换。这对于与 C 和 L 并联的大 R 值是正确的。我们的公式对于与 L 串联的小 R 是正确的。

“Q”的实际应用是串联谐振电路中 L 或 C 两端的电压是总施加电压的 Q 倍。在并联谐振电路中,通过 L 或 C 的电流是总施加电流的 Q 倍。

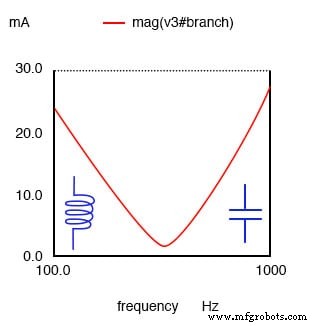

串联谐振电路

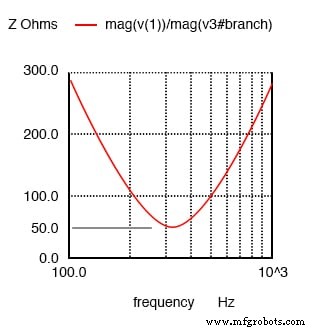

串联谐振电路在谐振频率下看起来像一个电阻。由于谐振的定义是XL=XC,电抗分量抵消,只留下电阻对阻抗有贡献。

阻抗在谐振时也处于最小值。在谐振频率以下,串联谐振电路看起来是电容性的,因为电容器的阻抗增加到大于减小的感抗的值,留下净电容值。

高于谐振时,感抗增加,容抗减小,留下净感性分量。

注意:

在谐振时,串联谐振电路表现为纯电阻。在谐振以下,它看起来是电容性的。在共振之上,它看起来是电感性的。 谐振时电流最大,阻抗最小。电流由电阻值设定。高于或低于谐振,阻抗增加。

串联谐振电路中谐振时的阻抗最小。

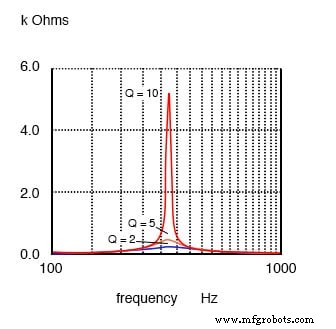

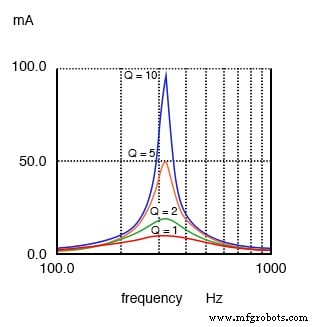

可以通过改变串联电阻来改变谐振电流峰值,从而改变 Q。这也会影响曲线的宽度。与高电阻、低 Q 电路相比,低电阻、高 Q 电路具有较窄的带宽。

Q 和谐振频率方面的带宽:

BW =fc/Q 其中 fc =谐振频率 Q =品质因数

与低 Q 相比,高 Q 谐振电路的带宽较窄

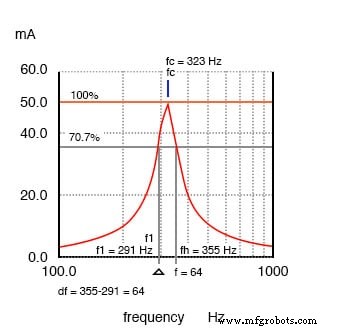

带宽是在 0.707 个电流幅度点之间测量的。由于 P =I 2 ,0.707 个电流点对应于半功率点 R, (0.707) 2 =(0.5)。

带宽,Δf 在串联谐振电路的 70.7% 幅度点之间测量。

BW =Δf =fh-fl =fc/Q 其中: fh =高频带边缘 fl =低频带边缘 fl =fc - Δf/2 fh =fc + Δf/2 其中 fc =中心频率(谐振频率)

在上图中,100% 电流点为 50 mA。 70.7% 电平为 .707(50 mA)=35.4 mA。从曲线中读取的上下频带边缘分别为 291 Hz 和 fh 355 Hz。带宽为64Hz,半功率点为中心谐振频率的±32Hz:

BW =Δf =fh-fl =355-291 =64 fl =fc - Δf/2 =323-32 =291 fh =fc + Δf/2 =323+32 =355

由于 BW =fc/Q:

Q =fc/BW =(323 Hz)/(64 Hz) =5

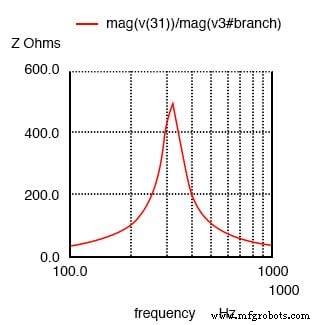

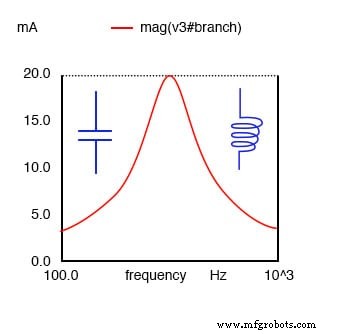

并联谐振电路

并联谐振电路的阻抗在谐振频率处最大。在谐振频率以下,并联谐振电路看起来是感性的,因为电感的阻抗较低,吸收的电流比例较大。

高于谐振时,容抗减小,吸收较大的电流,从而呈现容性特性。

并联谐振电路在谐振时为电阻,谐振以下为电感,谐振上方为电容。

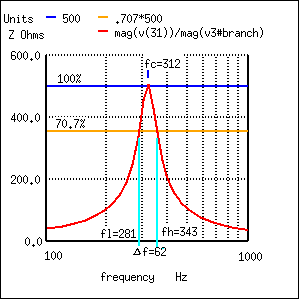

阻抗在并联谐振电路中的谐振处最大,但在谐振上方或下方减小。由于电压与阻抗成正比 (E=IZ),因此电压在谐振处达到峰值。

并联谐振电路:谐振时的阻抗峰值。

由于与电感器串联的高电阻导致的低 Q 在并联谐振电路的宽响应曲线上产生低峰值。高 Q 值是由于与电感器串联的电阻低。这会在较窄的响应曲线中产生较高的峰值。高Q值是通过绕较大直径(较小规格)、较低电阻线的电感来实现的。

并联谐振响应随 Q 变化。

在半功率点之间测量并联谐振响应曲线的带宽。这对应于 70.7% 的电压点,因为功率与 E 2 成正比 . ((0.707) 2 =0.50) 由于电压与阻抗成正比,我们可以使用阻抗曲线。

带宽,Δf 是在并联谐振电路的 70.7% 阻抗点之间测量的。

在上图中,100% 阻抗点为 500 Ω。 70.7% 电平为 0707(500)=354 Ω。从曲线中读取的上下频带边缘分别为 281 Hz(fl)和 343 Hz(fh)。带宽为62Hz,半功率点为中心谐振频率的±31Hz:

BW =Δf =fh-fl =343-281 =62 fl =fc - Δf/2 =312-31 =281 fh =fc + Δf/2 =312+31 =343Q =fc/BW =(312 Hz)/(62 Hz) =5

相关工作表:

- 共振工作表

- 电路的代数替换工作表

工业技术