如何设计高速 PCB 的图像平面

如今,大多数高速电路系统都使用多层PCB,并且许多电路系统具有众多的工作电源,这对图像平面设计提出了严格的要求,特别是多个电源/地平面之间的关系的解决。此外,在器件层设计上需要设计特殊的覆铜表面,以阻止振荡器产生RF(射频)能量,并为大功率元件提供出色的散热。

图像平面的功能

图像平面是与印刷电路板中的信号层相邻的覆铜表面。图像平面的主要功能包括:

1)。降低回流噪声和 EMI(电磁干扰)。图像平面为信号回流提供低阻抗路径,尤其是当配电系统中流过大电流时。更重要的是,它们减少了信号和回流形成的闭环面积,从而降低了EMI。

2)。控制高速数字电路中信号线之间的串扰。串扰由比值 D/H 确定,其中 D 是指干扰源和被干扰对象之间的距离,H 是指信号层之间的图像平面的高度。通过改变H的值可以控制D/H的比值,从而最终控制信号线之间的串扰。

3)。控制阻抗。印制线路的特性阻抗与线路的宽度以及线路与图像平面之间的高度有关。如果没有像平面,就有可能无法控制阻抗,导致传输线匹配失败,信号反射失败。

此外,图像平面还能够控制从反射到外板的噪声。必须承认,仅图像平面不足以实现这些功能,必须补充严格的设计规则才能实现预期目标。这个事实可以表述为:为了控制高速数字电路中的噪声,图像平面是必不可少的,但它们不能单独工作。

信号回流的层跳过

在多层PCB中,每个布局层应与一个图像平面相邻,信号返回电路在相应的图像平面上流动。当信号线不穿过布局层时,通常的方法是先将信号线连接到布局层,然后将信号线通过通孔连接到另一层。因此,信号线从一层跳到另一层,电流也沿着相同的路径返回。当两层都是接地层时,返回电流能够通过连接两层的通孔或接地引脚跳过。当一层为电源层,另一层为地层时,返回电流唯一能在层间跳跃的机会是放置去耦电容的位置。如果没有去耦电容或接地层连接的过孔,则必须通过必须经过最远的返回电流进行跳跃,使返回电流与其他电路去耦,从而引起串扰和EMI。

因此,在PCB设计过程中,跳层最好设置在靠近元器件的接地引脚或去耦电容周围。当这不能实现时,可以在跳跃点放置接地通孔(在两个接地层之间跳跃)或旁路电容(在电源层和接地层之间跳跃),以使返回电流跳跃。

分割平面

在使用多层PCB的过程中,有时需要生成一个没有铜箔的具有一定宽度的区域,将一个集成的图像平面分割成几个独立的部分,称为分割平面。

分离平面通常用于阻止噪声干扰敏感电路和隔离不同的参考电压,例如阻止数字噪声进入模拟、音频、I/O 区域以及隔离 5V 和 3.3V 电源电压之间。

分裂平面可分为完全分裂和不完全分裂。前者是指分裂后电源层和地层之间的完全隔离。后者是指电源层之间的完全隔离,而接地层通过“桥”连接。使用完全分裂还是不完全分裂取决于分裂平面之间是否有信号连接。

• 平面分割示例

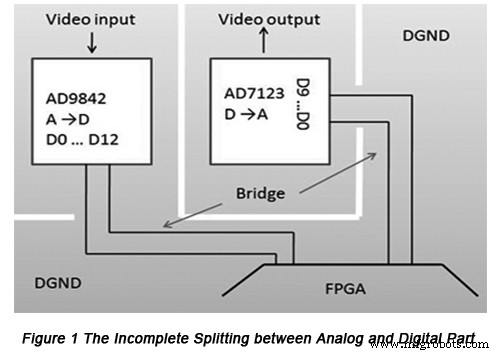

图 1 是某测试平台的模拟和数字混合电路的部分图像平面设计。视频模拟输入经AD转换后传输到FPGA,作为DA转换输出。 AD 和 DA 都使用独立的电源组件来提供电源。数字元件占据了电路板的大部分空间,而模拟元件只占了一小部分。但是,它们都是必不可少的部分,对整个系统的性能很重要。因此,在处理这些组件的过程中必须非常小心。数字部分的噪声不进入模拟部分是理想的。但是,来自 AD 和 DA 转换器的一些信号连接到数字部分的 FPGA。为了保证这些连接信号的回流,数字电源和模拟电源必须完全隔离,而数字地和模拟地必须完全隔离,使模拟部分对数字部分的影响降到最低。

从数字部分到模拟部分的所有线路都必须通过桥,其开口尺寸应刚好适合所需导线的通过,以便数据信号回流能够通过桥返回,从而避免对其他信号的干扰返回路径的绕组。在这个PCB设计中,AD和DA部分的地是完全相互隔离的。

• 平面分割过程中的一些问题

一个。隔离层的重叠

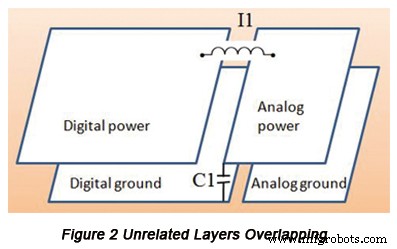

在多层 PCB 中,分裂平面通常用于隔离不同的电源。一般来说,这些电源对应的地层是相互隔离的,即每个电源都有自己的参考层。在PCB设计过程中,必须避免隔离层重叠。例如,在大多数多层 PCB 中,模拟部分和数字部分的电源层和接地层是相互隔离的。模拟电源层和数字地层不能像图2那样在空间上重叠。

如果出现重叠隔离层,则会在重叠区域出现一个小的焊盘电容 C1。电容会使射频能量从一层传输到另一个隔离的、静态的、独立的层,从而降低隔离的有效性。

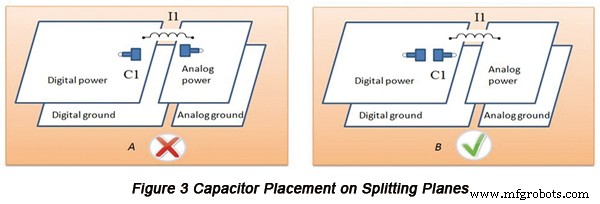

湾。去耦电容放置

为了滤除高速元件产生的高频噪声,PCB上布置了大量的去耦电容。如果PCB中出现了分层,在布局的过程中可能会出现去耦电容的地引脚没有与其他参考地层连接,而是与相应的地层连接的情况。这种类型的错误可能会发生并导致从一层到另一层的噪声去耦,这类似于分割平面重叠。这就是为什么这个问题应该在设计阶段解决。再以数模混合电路为例。模拟电源通过铁氧体磁珠从数字部分引入,C1 指数字部分的去耦电容。在图3A中,C1的电源管脚接数字电源,地管脚接模拟地,导致敏感模拟部分的高频数字噪声去耦,这是错误的连接。图 3B 是右侧的去耦电容连接。

C。单点接地

当不同电源的参考层连接在一起时,必须保证单点接地。在例示的数模混合电路中,电路板分为数字部分和模拟部分,数字地和模拟地都具有至少两个连接点,使得噪声信号可能通过这两个连接点在两个参考层之间形成循环,即称为“接地回路”。接地回路会导致噪声、EMI、能耗和散热困难。接地环路问题有一个简单的解决方案:只要参考层之间只有一个连接点,就无法形成环路。

局部地面层

作为图像平面的一部分,局部接地层是指覆盖在 PCB 上表面的铜箔,直接与内部接地层相连。它的主要功能是捕获一些关键芯片(如振荡器)内部产生的射频磁通或用于功率耗散。

为了获得出色的性能,振荡器、晶体和时钟支架应组装在独立的本地接地层上。原因包括:

1)。如果振荡器封装在金属包层中,金属包层内部产生的射频电流可能会很大,以至于其接地引脚无法通过低能耗的方法将大电流引至地。结果,这种金属包层就变成了单极天线。

2)。如果在 PCB 上放置振荡器时使用表面贴装组装技术,则上述问题会变得更糟,因为塑料材料通常用于 SMT 封装,阻止射频电流导致接地点。最后,封装内部产生的射频电流将辐射到自由空间,并与其他组件解耦。

3)。普通振荡器能够驱动时钟缓冲,属于超高速和快速边沿速率的器件,产生大量射频电流,可能导致电流功能失效。

如果在振荡器和时钟电路中组装一个局部接地层,将提供图像平面,用于捕获振荡器和相应电路内部产生的射频能量,从而减少射频辐射。

20-H 规则

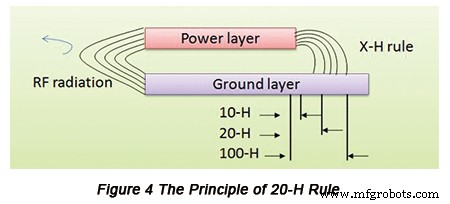

作为经验法则,20-H 法则描述了在高密度的多层 PCB 中,为了减少电路板向自由空间辐射的电磁能量,电源层的尺寸应比接地层的尺寸小 20H,其中 H指两层之间的距离。在图4中,左侧为电源/地层,没有任何特殊设计,边缘辐射强烈,会影响相邻电路的功能。右侧部分通过将功率表面尺寸减小 X-H 表示 RF 辐射情况。可以看出,地层吸引了大量的磁力线,射频辐射能量降低。根据实验结果,射频辐射力从10-H开始下降;在 20-H 的情况下,地面能够吸引 70% 的磁流;在100-H情况下,磁力可降低98%。

自然,20-H 并不适合所有 PCB 结构。 20-H 的效率取决于工作频率、电源/接地层的物理尺寸以及它们之间的距离,后两个元素决定了 PCB 板的 SRF(自谐振频率)。研究表明,当 PCB 在任何 SRF 下运行时,20-H 不起作用,接地也无法吸引辐射能量。更糟糕的是,反而会产生大量的辐射能量。因此,在实际的高速电路中,在决定是否选择20-H规则时必须考虑到具体情况。

有用的资源

• 高速布局技巧

• 减少 EMI 影响的高速 PCB 布线技术

• 高速 PCB 设计的误解和策略

• 差分等距高速 PCB 设计的处理和仿真验证

• PCBCart 的全功能 PCB 制造服务 - 多种增值选项

• PCBCart 的高级 PCB 组装服务 - 从 1 件开始

工业技术