如何使用最常见的 VHDL 类型:std_logic

VHDL 中最常用的类型是 std_logic .将此类型视为单个位,即由单个物理线路承载的数字信息。 std_logic 比 integer 让我们对设计中的资源进行更细粒度的控制 type,我们在之前的教程中一直在使用。

通常,我们希望数字接口中的线具有值 '1' 或 '0' .这两个值是位(二进制数字)可以具有的唯一值。但实际上,物理数字信号可以处于多种状态,std_logic type 可以很好地模拟。因此它是VHDL中最常用的类型。

这篇博文是基本 VHDL 教程系列的一部分。

std_logic type 可以有以下值:

| ‘1’ | 逻辑1 |

| ‘0’ | 逻辑 0 |

| ‘Z’ | 高阻抗 |

| ‘W’ | 信号弱,分不清是0还是1 |

| ‘L’ | 弱0,下拉 |

| ‘H’ | 弱1,上拉 |

| '-' | 无所谓 |

| ‘U’ | 未初始化 |

| ‘X’ | 未知,多个驱动程序 |

对于应该为单个二进制值建模的类型,这似乎有很多不同的状态。别担心,我们不会在本教程系列中使用所有这些类型。我们将使用 '1' 和 '0' 当然。我们还将看到 'U' 和 'X' ,这将帮助我们发现设计中的错误。其他值是高级 VHDL 功能,可用于建模通信,例如 I

2

C 设备,或用于创建三态总线。

如果多个进程试图向一个信号写入不同的值,我们说它有多个驱动程序 .如果一个 std_logic 信号有多个驱动程序,它不会是编译或运行时错误,至少在模拟器中不会。那是因为 std_logic 是一个已解析的类型 ,意味着它的值将由一个解析函数来确定。

std_logic 的值 两个驱动的信号将根据这个分辨率表来确定:

| U | X | 0 | 1 | Z | W | L | H | – | |

|---|---|---|---|---|---|---|---|---|---|

| U | X | X | 1 | 1 | 1 | 1 | 1 | X | 1 |

| U | X | 0 | X | 0 | 0 | 0 | 0 | X | 0 |

| U | U | U | U | U | U | U | U | U | U |

| U | X | X | X | X | X | X | X | X | X |

| U | X | 0 | 1 | Z | W | L | H | X | Z |

| U | X | 0 | 1 | W | W | W | W | X | W |

| U | X | 0 | 1 | L | W | L | W | X | L |

| U | X | 0 | 1 | H | W | W | H | X | H |

| U | X | X | X | X | X | X | X | X | – |

运动

在本视频教程中,我们将学习如何使用声明和显示 std_logic 波形中的信号:

我们在本教程中创建的最终代码:

library ieee;

use ieee.std_logic_1164.all;

entity T10_StdLogicTb is

end entity;

architecture sim of T10_StdLogicTb is

signal Signal1 : std_logic := '0';

signal Signal2 : std_logic;

signal Signal3 : std_logic;

begin

process is

begin

wait for 10 ns;

Signal1 <= not Signal1;

end process;

-- Driver A

process is

begin

Signal2 <= 'Z';

Signal3 <= '0';

wait;

end process;

-- Driver B

process(Signal1) is

begin

if Signal1 = '0' then

Signal2 <= 'Z';

Signal3 <= 'Z';

else

Signal2 <= '1';

Signal3 <= '1';

end if;

end process;

end architecture;

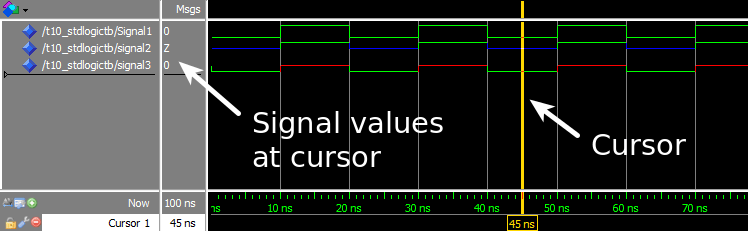

按下运行后ModelSim中的波形窗口,并在时间轴上放大:

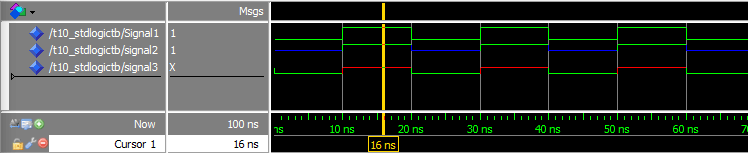

光标位于重复信号周期另一部分的波形:

分析

该练习演示了 VHDL 的解析功能如何与 std_logic 配合使用 类型。在处理数字逻辑时,以波形研究时间线通常更实用 而不是使用打印输出。因此,我们在本次练习中使用了 ModelSim 波形来检查信号值。

第一个进程和Signal1 仅用于更改第三个进程在 Signal2 上驱动的值 和 Signal3 .

第二个进程,驱动程序 A,将尝试驱动 'Z' 到 Signal2 , 和一个 '0' 到 Signal3 不断。

第三个进程,驱动程序 B,将在驱动 '1' 之间交替 和 'Z' 到两个 Signal2 和 Signal3 .

我们在波形截图中看到 Signal1 在 '0' 之间变化 和 '1' ,因为只有一个进程试图驱动这个信号。我们还可以看到,多个驱动信号是按照VHDL代码注释贴的解析表解析的:

| 信号 | 司机A | 驱动程序 B | 结果 |

|---|---|---|---|

| 信号2 | ‘Z’ | ‘Z’ | ‘Z’ |

| 信号2 | ‘Z’ | ‘1’ | ‘1’ |

| 信号3 | ‘0’ | ‘Z’ | ‘0’ |

| 信号3 | ‘0’ | ‘1’ | ‘X’ |

外卖

std_logic是 VHDL 中用于保存单个位值的最常见类型- 想想

std_logic在我们的数字设计中将信号作为物理线 - 如果多个进程试图驱动

std_logic信号,其值由分辨率表确定

转到下一个教程 »

VHDL