面向软件开发人员的 CPU 加 FPGA 设计流程:一个新的有形现实

最近,Brian Bailey 组织了一个圆桌会议,结果发表了一篇名为 Supporting CPUs Plus FPGAs 的两部分文章 .专家们讨论了基于 FPGA 和 CPU 的系统设计不断发展的现实。本次讨论涉及设计流程的最新发展,以及如何使用新技术帮助软件开发人员加快 CPU 加 FPGA 平台的上市时间。

简介

看着人们对人工智能(AI)日益增长的兴趣、物联网(IoT)的出现以及数据中心加速的趋势,我们不禁要问:三者之间的共同点是什么?

软件开发人员处于所有这些趋势的中心,他们正在寻求加速他们的编程和计算。最新的技术突破,包括 FPGA 和 CPU 之间的低通信延迟,加上当今 FPGA 相对较低的功耗,使基于 FPGA 和 CPU 的系统成为实现所需性能的正确选择。然而,在这种融合的中心,软件开发人员受到 FPGA 技术底层复杂性的阻碍。

在过去几年中,高级综合 (HLS) 工具在解决当今系统复杂性和缩短上市时间方面有了很大改进。但是,HLS 工具首先关注 IP 块(即,它们以 IP 为中心)。 HLS 工具无法支持大量系统级决策/优化来满足要求。其中一些要求包括在软件任务和硬件加速器之间找到适当的平衡、比较流水线与并行执行、实现所需的数据粒度、评估通信机制等等。

为了构建这些复杂的系统,软件开发人员需要一个设计流程来提供硬件和软件的联合支持。这样的流程必须足够简单,以保证它的使用(如软件开发人员流程)和软件开发人员的采用。流程还必须提供有关可用于实现所需性能目标的优化选择的深刻反馈。一些公司最近通过抽象硬件设计流程的技术细节,为方便软件开发人员完成任务铺平了道路。这些公司受到ESL 模型及其应用:电子系统级设计和实践验证中描述的系统级设计方法的启发 .

了解系统级设计流程方法

系统级设计专注于更高的抽象级别问题。虽然需要专注于更大的图景,但在实际开发之前,使用不同级别的抽象来验证、验证、改进和集成系统的不同部分。尽管工程社区不同意使用一种通用语言,但大多数设计工程师从算法级别开始。设计人员通过创建在 C/C++/SystemC、MATLAB、Simulink 和 LabVIEW 环境中编写的执行模型来验证非功能性和功能性系统规范。这些高级语言用于对整个系统的行为进行建模。

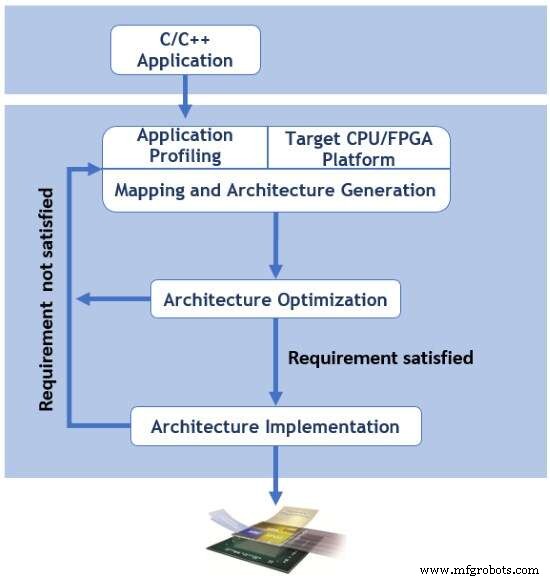

出于本次讨论的目的,我们专注于基于 C/C++ 规范的系统级设计流程(图 1)。第一块分为三个步骤。这些步骤中的第一步代表应用程序分析(即硬件-软件分区),其中考虑将 C/C++ 代码片段(函数、循环等)移动到硬件 (FPGA) 中。下一步是 CPU/FPGA 平台(例如 ARM53/FPGA、POWER8/FPGA)的规范和硬件平台元素(系统时钟、处理器缓存、互连等)的配置。接下来的步骤是在硬件和软件(即硬和/或软 CPU)之间映射应用任务(基于所分析的应用),并在最后生成可执行架构。

图 1. CPU/FPGA 的典型系统级设计流程

(来源:Space Codesign Systems, Inc.)

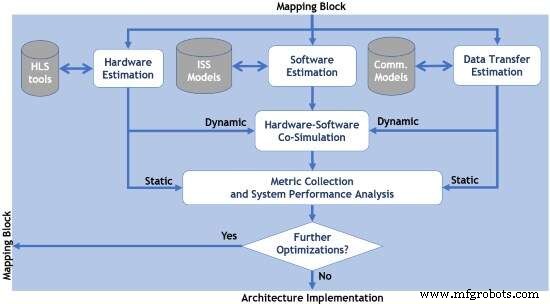

图 1 的第二个块涉及架构优化(也称为架构探索或性能验证)。这在图 2 中有更详细的描述。

图 2. 架构优化过程

(来源:Space Codesign Systems, Inc.)

架构优化过程涉及以下估计量:

- 硬件估算 评估硬件分区的指标(即在 FPGA 上移动的 C/C++ 代码)。它可以按资源、性能(例如,循环延迟)和功率估计进行细分。硬件估计由 HLS(高级综合)工具驱动。

- 软件评估 评估在 CPU(即硬和/或软 CPU)上运行的 C/C++ 分区代码的指标。这个过程是对硬件估计步骤的补充。性能指标的示例包括处理器负载、任务切换和缓存未命中。

- 数据传输估算 包括对硬件和软件通信的接口(即内存映射和流接口)进行建模。收集的指标示例包括总线性能(例如延迟和吞吐量)、队列和内存使用情况。

这些估计在数据库中汇总,并向开发人员提供系统性能分析,以评估是否满足系统要求。满足需求的架构进入架构实现过程;否则,将处理额外的系统级优化尝试。

图 1 的最后一个块与架构实现有关,其中使用 Xilinx Vivado 或 Intel Quartus Prime 等实现工具将系统架构转换为比特流(用于 FPGA 实现),以便在特定物理平台上执行最终和完整的系统生成。这一步必须生成高质量的代码,并且对软件开发人员应该是透明的。

系统级优化

长期以来,缺乏用于架构优化的自动化工具一直被认为是基于 FPGA 的计算的一个关键弱点。由于所涉及的复杂性和挑战,此类工具的开发很困难。

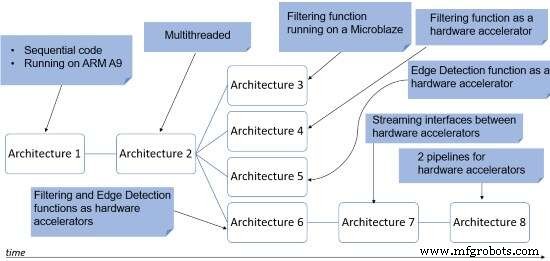

为了说明这些挑战,图 3 显示了在 Zynq-7000 平台上实现的由六个函数(C/C++ 代码段)组成的图像处理应用程序的架构探索过程中的典型系统级优化过程。在这里,我们列出了可以在平台上实施的八种潜在架构。由于上市时间不允许实施每种架构,因此必须迅速确定要实施的最佳架构。即使对于经验丰富的硬件设计人员来说,这一系列优化也可能具有挑战性。

图 3. 系统级决策的架构探索以蓝色显示

(来源:Space Codesign Systems, Inc.)

SDSoC/SDAccel (Xilinx)、Merlin Compiler (Falcon Computing Solutions) 和 SpaceStudio (Space Codesign Systems) 等 FPGA 软件开发工具是商业解决方案,可协助软件开发人员设计 FPGA/CPU 系统,同时实现系统级优化。这些工具采用与图 1 和图 2 中描述的流程类似的流程,并且——由此——它们展示了采用不同方法的新一代系统级工具的存在。

SDSoC 以两步法评估系统性能。最初,SDSoC 估计目标物理平台及其通信接口的硬件功能(来自 HLS 工具)和内部特征(即数据传输)的延迟。稍后,将此估计值与在物理平台上运行的纯软件版本的应用程序进行比较。

Merlin Compiler 提出了源到源的转换。源到源转换的目标是减少或消除软件/算法开发与现有 HLS 设计流程之间的设计抽象差距。 Merlin Compiler 依靠四个编译指示来推断特定的 FPGA 设计。除了显式 pragma 触发的四个主要优化之外,Merlin Compiler 还包含各种隐式优化(即编译器的转换通道),这些优化与 pragma 一起执行,以帮助改进流水线和并行化的结果。

SpaceStudio 为每个架构候选(映射)无缝生成一个可执行的虚拟平台(VP)。典型的 VP 由连接到各种模型的总线、内存控制器和其他数据外设模型的处理器内核模拟器组成。它在专为应用程序量身定制的联合仿真环境中对目标平台以及数据传输进行建模。这意味着可执行的 VP 可以对应用程序进行更准确的性能预测和算法验证。它还集成了监控和分析功能,用于对硬件功能和软件任务进行非侵入式性能分析。 VP 依赖 HLS 工具进行硬件估计,而硬件映射函数的延迟(例如,延迟)会自动注释以提高模拟过程的准确性。软件开发人员可以检查 VP 以了解优化任务是如何实现的。此类反馈有助于软件开发人员实现特定应用优化的预期设计。

查看商业生态系统的一种方式

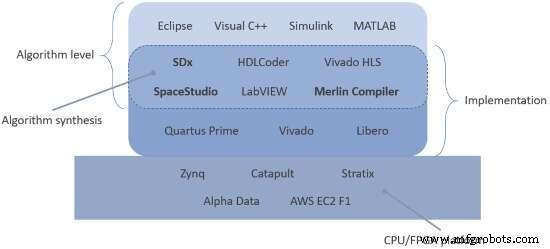

图 4 展示了在 CPU 和 FPGA 的基于平台的设计的世界范围内吸引的商业生态系统的视图。第一个(上)框显示了算法级别的主要设计条目。第二个框包含支持算法合成的环境(即从算法到实现)。以粗体标记的工具支持 C/C++ 设计入口并执行系统级优化。第三个框代表用于实现架构的工具,主要是来自 FPGA 供应商的工具,用于执行低级综合和比特流生成。在图的底部,举例说明了 CPU/FPGA 平台。

图 4. CPU/FPGA 平台的商业生态系统

(来源:Space Codesign Systems, Inc.)

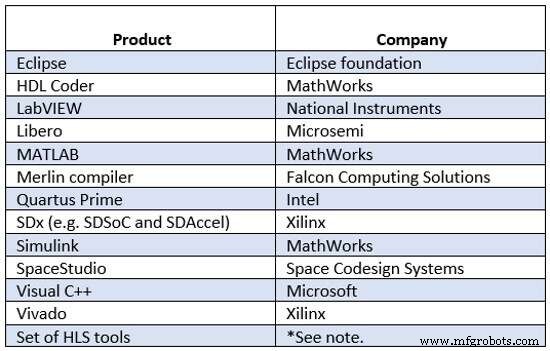

此外,表 1 列出了 CPU/FPGA 平台设计中使用的一些主要商业工具。

表 1. 商业自动化工具(*注:本次审查中提出了一个列表)

结论

最终目标是将 CPU 加 FPGA 平台的开发普及到更广泛的用户群,例如软件开发人员社区。从编程语言的类比来看,IT 行业花了 50 多年的时间才将编程语言演变为友好的语言,例如 Python 或最近的 Swift。 FPGA 编程行业正在发生类似的演变过程。 HLS 工具的接受需要一段时间才能得到系统设计人员的认可。今天,随着面向软件开发人员的系统级解决方案的出现,我们正在进入一个新阶段。 SpaceStudio、SDSoC 和 Merlin Compiler 等商业工具证明了这一验收过程。尽管如此,要在针对 CPU 和 FPGA 平台的编译器之间实现完全自动化和优化的流程,仍有许多工作要做。

Guy Bois,工程学博士 是 Space Codesign Systems 的创始人,也是蒙特利尔理工大学软件和计算机工程系的教授。 Guy 与 STMicroelectronics、Grass Valley、PMC Sierra、Design Workshops Technologies 和 Cadabra Systems 等行业领导者合作参与了许多研发项目。 Guy 在硬件/软件协同设计领域的研究专长促成了该解决方案的商业化以及 Space Codesign Systems Inc 的 SpaceStudio 的诞生。

嵌入式

- 专家访谈:AMendate 用于 3D 打印的自动拓扑优化软件

- 专家访谈:Altair 的 Ravi Kunju 关于 3D 打印仿真软件

- 给 Bosch Software Innovatons 新任 CEO Stefan Ferber 的 5 个问题

- 项目探索物联网安全的可信设计和验证流程

- 新的基于机器学习的工具提供自动化芯片设计流程优化

- 嵌入式视觉 MIPI 相机的 FPGA 加速器

- Cadence 和联电合作认证 28HPC+ 工艺的模拟/混合信号流

- 使用 FPGA 进行嵌入式设计:构建项目

- 自动化:低成本机器人的新硬件和软件

- 很酷的物联网用例:联网汽车的新安全机制

- 欧姆龙为其移动机器人推出新软件

- 适应制造业的新现实