具有减小的特征尺寸和干净的蚀刻停止层结构的 a-IGZO TFT 的增强可靠性

摘要

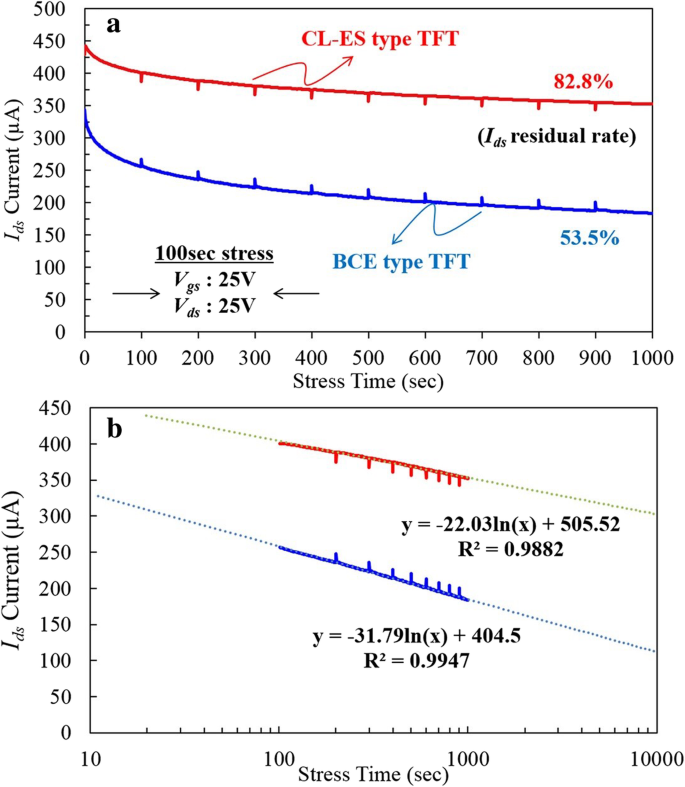

漫反射 Cu + 的影响 对非晶铟镓锌氧化物 (a-IGZO) 薄膜晶体管 (TFT) 在清洁蚀刻停止 (CL-ES) 工艺和背沟道蚀刻 (BCE) 工艺期间的微观结构和性能进行了研究和比较. TOF-SIMS 验证用清洁成分形成的 CL-ES 层可以保护 a-IGZO 层免受 S/D 蚀刻剂的影响并防止 Cu + 扩散,这有助于减少类受体缺陷的数量并提高 TFT 的可靠性。制造的 CL-ES 结构的 TFT 具有优异的输出稳定性(最终的 I ds/初始 I ds =82.2 %) 与 BCE 结构的 TFT (53.5%) 相比,因为它们具有更好的初始 SS 值(0.09 V/dec vs 0.46 V/dec)和更好的最终 SS 值(0.16 V/dec vs 0.24 V/dec) 在高电流应力 (HCS) 评估之后。特别是,阈值电压的变化有很大的差异(CL-ES TFT 为 3.5 V,BCE TFT 为 7.2 V),这意味着 CL-ES 结构的 TFT 比 BCE 结构的 TFT 具有更高的可靠性薄膜晶体管。因此,CL-ES工艺有望推动a-IGZO技术在半导体行业的广泛应用。

背景

最近,显示产品不仅强调大面积和高分辨率,而且还强调美观的外观设计[1,2,3]。窄边框已被用作这种设计重点的重要特征之一 [4]。要实现这一点,必须将驱动显示器的主电路集成到面板中。阵列上的栅极驱动 IC (GOA) 是一种相对简单且常用的方法,其中栅极信号一行一行地进入面板,V 开 每次都按顺序移动。 GOA 具有多种优势,例如降低成本(消除 G-IC 成本、去除 G-IC 键合工艺、提高玻璃基板利用率等)和美观效果(窄边框或无边界设备)[5]。然而,与单个像素 TFT 不同,GOA TFT 需要更严格的可靠性条件,以实现更高的输出电流和更长的导通时间性能。随着近年来市场对高分辨率产品的需求不断增加,提高GOA性能的可靠性已成为迫切和必要的[6]。

非晶氧化铟镓锌(a-IGZO)由于其高饱和电子迁移率(5~10 cm 2 )被广泛应用于显示器行业 /V s) 和低截止电流 (<1 pA) [7, 8]。背沟道蚀刻 (BCE) 技术通常用于工业中的 TFT 生产 [9, 10]。 BCE 结构的 a-IGZO TFT 对于单个像素 TFT 和 GOA TFT 的尺寸减小具有令人满意的特性。然而,一些关键的 TFT 特性,尤其是输出电流稳定性,无法满足 GOA TFT 所需的高电流应力 (HCS) 环境 [11,12,13],主要是由于 BCE 工艺的两个特征 [14]。第一个是 a-IGZO 薄膜(a-IGZO TFT 的背沟道)的表面暴露于 S/D 蚀刻剂,这些蚀刻剂传统上由 HNO3、H3PO4 和 CH3COOH 组成,蚀刻速度快且不可控用于 a-IGZO 薄膜 [15]。 S/D 电极(Cu 金属)蚀刻可以使用温和的 H2O2 基蚀刻剂,其蚀刻稳定且对 a-IGZO 膜的损坏最小,但对 a-IGZO 膜的表面损坏仍然是不可避免的 [16] .其次,S/D 金属 (Mo/Cu/Mo) 与 a-IGZO 膜的直接接触可能会污染 TFT 背沟道 [17]。幸运的是,清洁蚀刻停止 (CL-ES) 工艺更简单、成本更低且污染最小,可用于制造基于 a-IGZO 的 TFT,具有更高的均匀性和稳定性,适用于大面积显示器 [18]。尽管 CL-ES 结构的 TFT 显示出改进的性能,但蚀刻剂如何与 a-IGZO 膜反应以及 Cu + 扩散到a-IGZO薄膜中对器件的微观结构和性能的影响尚不清楚。

在这项研究中,通过 CL-ES 工艺通过批量蚀刻多层 a-IGZO/Mo/Cu/Mo 制造了具有减小的特征尺寸和干净的背沟道结构的 a-IGZO GOA TFT。此外,蚀刻剂和Cu + 的影响 研究了 CL-ES 结构的 a-IGZO GOA TFT 器件的微观结构和性能的扩散,并与 BCE 结构的 a-IGZO GOA TFT 器件进行了比较。更重要的是,CL-ES 器件的蚀刻停止层作为 S/D 蚀刻剂保护层以及 Cu + 扩散阻挡层,这有助于减少缺陷数量并提高高电流应力可靠性、SS 值、高电流应力和阈值电压变化等的可靠性。因此,这项工作提供了直接证据和有见地的证明CL-ES 结构 TFT 的性能与其 CL-ES 结构及其清洁组件高度相关,并证实 CL-ES 工艺可能是批量生产性能令人满意的显示器的有效途径。

实验方法

a-IGZO GOA TFT 的制造

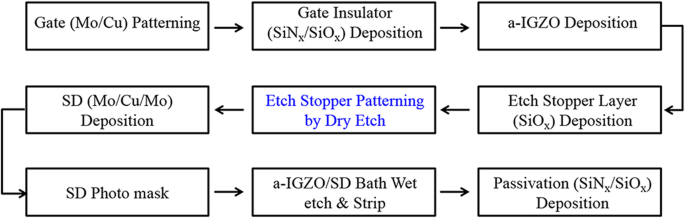

CL-ES 结构的 a-IGZO TFT 器件是通过改进的五步 CL-ES 工艺制造的(图 1),如我们之前的工作 [15] 中所报道的。首先,用 Mo/Cu 金属形成栅电极,并在 340 °C 下使用 PECVD 用 SiNx/SiOx (3000 Å/1000 Å) 双层沉积栅极绝缘体。其次,在氧气分压为 15% 的室温下使用 DC 磁控管反应溅射沉积 300 Å 的 a-IGZO 膜。使用 PECVD 在 240 °C 下沉积 1000 Å 的蚀刻停止层(SiOx,ESL),并通过 CF4 等离子体进行反应蚀刻以进行图案化,使用 BCE 工艺的有源光刻掩模作为蚀刻掩模。在这一步中,ES 层图案下方的 a-IGZO 膜受到保护,以免暴露于 CF4 等离子体,而其余的 a-IGZO 膜,不受 ES 层图案保护,也没有被蚀刻,而是转化为导电膜。第三,使用含有 0.2 wt% 氟化物添加剂的 H2O2 蚀刻剂、S/D 光刻掩模和 ES 溅射沉积和蚀刻源漏 (S/D) 电极(Mo/Cu/Mo 三层)层图案用作蚀刻掩模。第四,沉积3000 Å的钝化层。后续工艺与典型的TFT LCD背板制造工艺相似。

<图片>

a-IGZO GOA TFT的制作工艺

为了比较,使用传统的 BCE 工艺和相同的 BCE 掩模制造了 BCE 结构的 a-IGZO TFT 器件。

特征化

使用 SEM (Camscan Mx2600FE)、X 射线光电子能谱 (XPS, PHI Quantera II) 和飞行时间二次离子质谱 (IONTOF, TOF-SIMS 5) 表征样品的形貌、微观结构和成分.使用半导体特性分析仪 (Keysight 4082A) 在黑暗环境和 60 °C 下进行电气测量。为简单起见,使用 V 对超过 1000 s 的 HCS 可靠性进行了评估 gs 在 25 V 和 V ds 在 25 V。在评估过程中,GOA TFT 的状态通过测量 I ds 电流以 1-s 为间隔,以及 I 的趋势 ds 电流进行了分析。 我 d -V g 还以 100 秒的间隔监测传输特性。

结果与讨论

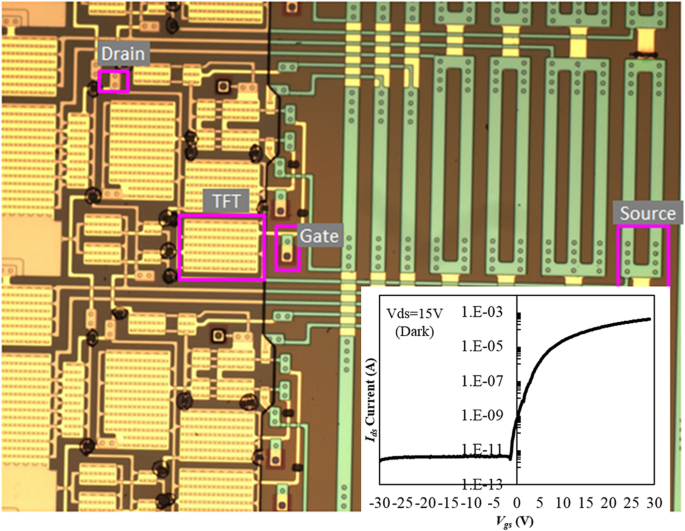

CL-ES 工艺制造的 GOA TFT 器件包含 TFT 通道和栅极、漏极和源极组件,如图 2 所示。为了准确测量每个 TFT 特性,使用激光断开所有 TFT,从而变得独立,使得栅极、源极和漏极不能与任何其他 TFT 共享一个节点。如图2中红线所示,该TFT采用多通道分离式GOA结构设计,通道宽度和长度分别为120 μm和10 μm,以方便电学测量。该 TFT 还设计为通过放置一块浮动金属(位于通道的中间),使每个 TFT 通道具有平均水平的电流,该金属片集成了每个通道。在进行 HCS 可靠性评估之前,首先通过评估感兴趣的 TFT 与其他外围 TFT 的电干扰来确认分离的操作可靠性。在这种情况下,I 经测量,分离的 GOA TFT 的关断噪声电流为 3 pA(图 2 中的插入曲线),确认附近没有来自其他 GOA 组成器件的电气干扰。

<图片>

与 GOA 电路电分离的 GOA TFT 的照片(插入:I 感兴趣的 TFT 和其他外围 TFT 之间的关断噪声电流)

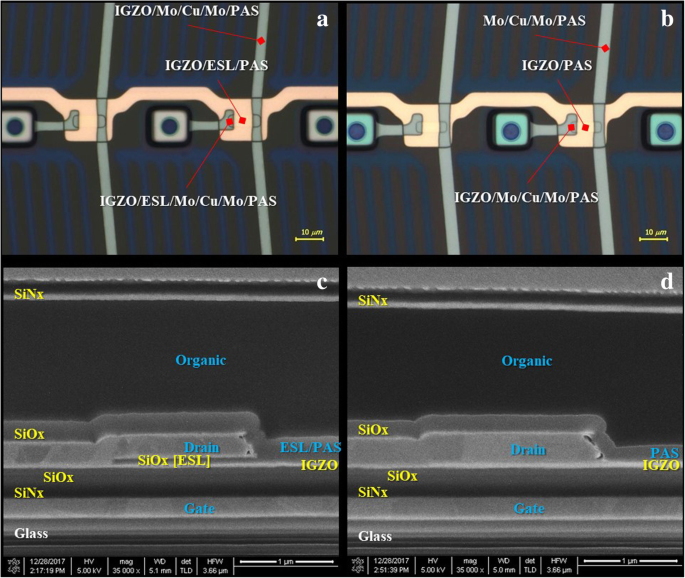

测量并比较了 CL-ES 结构的 TFT 和 BCE 结构的 TFT 的几个特征尺寸。对于 CL-ES 结构的 TFT(图 3a),宽度和长度分别为 4 μm 和 6 μm,类似于图 3b 中的 BCE 结构的 a-IGZO TFT。通常,BCE 工艺由于其小特征尺寸而适用于氧化物 TFT 制造。因此,获得的 CL-ES 结构的 TFT 显示出与 BCE 结构的 TFT 一样低的特征尺寸和高集成度。此外,CL-ES 结构的 TFT 的横截面尺寸与 BCE 结构的 TFT 的横截面尺寸相似(图 3c、d),而 CL-ES 结构的 TFT 显示出未观察到的明显 ES 层在 BCE TFT 中。 CL-ES 工艺主要形成 ES 图案,而多层 a-IGZO/Mo/Cu/Mo 上的批量蚀刻工艺可以使用与 BCE 工艺中类似的有源图案和源漏电极的掩模进行。因此,除了 ES 图案,CL-ES 工艺中使用的光刻掩模数量与 BCE 工艺相同。这种 CL-ES 工艺可以避免传统 ESL 工艺增加的掩模数量,并减小了特征尺寸,使其在经济上适合大规模生产。此外,无需使用半色调曝光,即TFT LCD行业常规使用的工艺简化程序,降低了工艺复杂度和制造成本。

<图片>

a-IGZO TFT 的 SEM 图像:a CL-ES 结构的 TFT 俯视图,b BCE 结构的 TFT 顶视图,c CL-ES 结构的 TFT 截面图,以及 d BCE结构TFT剖面图

为了进一步观察 BCE 制造过程中 BCE 结构 TFT 的表面缺陷,a-IGZO 薄膜在退火前(样品 1)、退火后(样品 2)和暴露于 H2O2 Cu 蚀刻剂后(样品)的表面组成3)通过XPS研究。在 a-IGZO 薄膜的全扫描光谱中(图 4a-c),在 BCE 制造过程中存在 In、Ga、Zn、O 和 C 元素的峰。如图 4d 所示,尽管 BCE 结构的 TFT 在退火前(样品 1)和在 330 °C 下退火 1 小时(样品 2)后 a-IGZO 薄膜的成分没有显着变化,但显着变化是暴露于湿化学品后观察到(样品 3)。特别是锌,其与氧的结合能相对较低,在样品 1 中为 4.82%,在样品 2 中为 5.42%,但在样品 3 中已降至 3.16%。在不同的过程中,Zn 相对于 In 的相对百分比变化是巨大的,即样品 1、2 和 3 分别为 44.1%、46.0% 和 27.6%。这与镓类似,它也与氧有很强的结合亲和力。换句话说,在湿蚀刻工艺期间,在氧化物半导体的暴露背表面上出现了不期望的缺陷,包括大量的Zn和Ga损失。造成这种现象的原因可能与它们对氧的结合能不同以及a-IGZO薄膜的分子结构不同有关[19]。

<图片>

a-IGZO薄膜表面成分的XPS分析a 退火前,b 退火后,c 在 BCE 过程中暴露于 H2O2 Cu 蚀刻剂后。 d 上述过程对应的原子百分比

众所周知,a-IGZO 薄膜对酸性蚀刻剂的耐化学性非常弱 [20]。特别是,据信决定 a-IGZO 分子结构的 Zn 的突然损失会导致 a-IGZO 膜的表面结构减弱。此外,通过其与氧的强结合能抑制载流子生成的 Ga 的还原可能会增加产生氧空位的可能性 [Vo] [21]。因此,即使在相对温和的H2O2基Cu蚀刻剂中,BCE结构的GOA TFT也无法避免对TFT背沟道的蚀刻损伤。

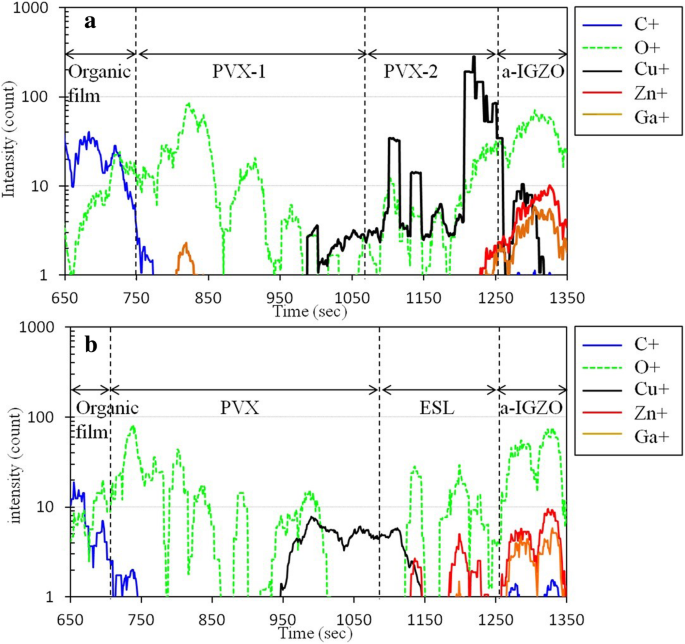

为了确认 ES 层的保护,通过使用 TOF-SIMS 对 BCE 和 CL-ES(清洁蚀刻停止层)工艺制备的样品研究 a-IGZO TFT 通道区域的组成(图 5)。由于Cu + 在a-IGZO薄膜中会产生受体型缺陷并俘获电子,因此a-IGZO TFT通道必须清洁以增强电稳定性。观察到,Cu + BCE 样本中检测到的峰值比 CL-ES 样本的峰值大 20 倍。此外,Cu + 的检测区域 与Zn + 的检测区域重叠 和 Ga + 在很大程度上(图 5a)。这些结果表明 BCE 结构的 TFT 中的 a-IGZO 薄膜被 Cu + 污染 由于 TFT 背沟道区中的 a-IGZO 膜与铜金属直接接触。对于 CL-ES 结构的 TFT(图 5b),Cu + 仅在 ES 区域检测到,表明避免了 a-IGZO TFT 沟道区域与 Cu 金属的直接接触。令人惊讶的是,大量的 Zn + 出现在 ESL 中。扩散的Zn + 是由 ESL 沉积期间较高的预处理等离子体条件和压力条件引起的。因此,CL-ES结构TFT中的ES层通过避免a-IGZO薄膜的表面损伤和污染来提高电稳定性至关重要。

<图片>

通过a制备的a-IGZO TFTs沟道区的TOF-SIMS分析 BCE 和 b CL-ES 流程

CL-ES 和 BCE 结构的 GOA a-IGZO TFT 的高电流应力 (HCS) 评估如图 6a 所示。对于相同的特征尺寸,初始 I CL-ES结构的TFT的ds电流为429 μA,高于BCE结构的TFT(343 μA)。经过 1000 s 的 HCS 评估后,I CL-ES 结构 TFT 的 ds 电流为 352 μA,约为其初始值的 82.2%。相比之下,I BCE 结构 TFT 的 ds 剩余电流已降至 183 μA,仅维持其初始值的 53.5%。此外,通过外推法评估(图 6b),I CL-ES 结构 TFT 的 ds 剩余电流预计为 302.6 μA,在 10,000 s 后保持其初始值的 70.5%。对于 BCE 结构的 TFT,I ds 剩余电流急剧下降至 111.7 μA,仅保持其初始值的 33.7%。因此,在相同的输出特性下,CL-ES工艺制造的GOA TFT的集成度比BCE工艺提高了271%。

<图片>

一 1000 s 和 b 的实验数据 CL-ES 和 BCE 结构的 GOA TFT 长期 HCS 评估的外推

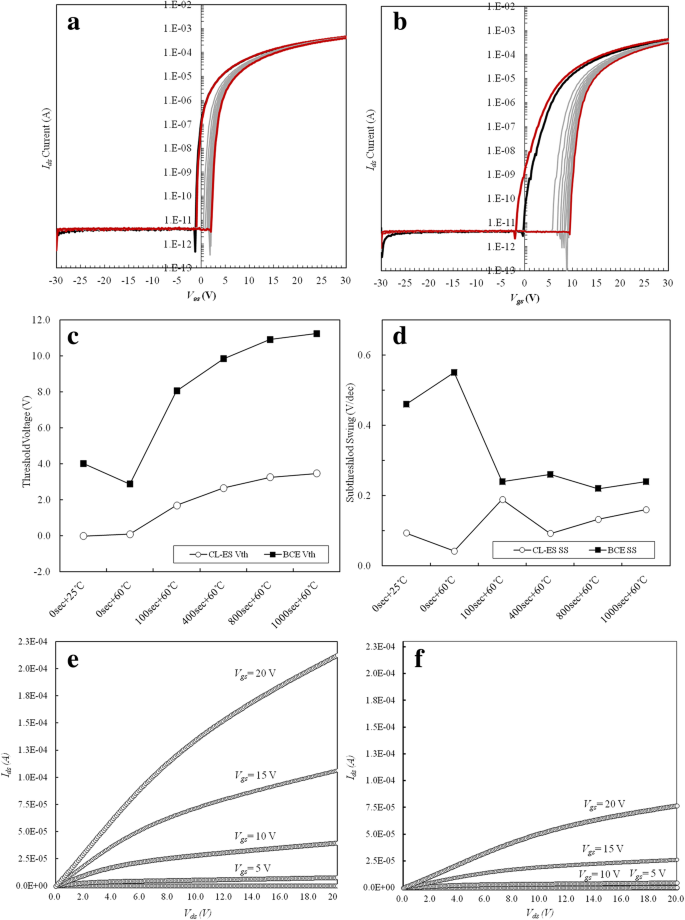

此外,I -V 还测量了 HCS 可靠性评估期间 CL-ES 和 BCE 结构的 GOA TFT 的转移特性(图 7 和表 1)。对于 CL-ES 结构的 TFT(图 7a),初始 HCS 评估(25 °C)中的阈值电压为 0.0 V,在 60 °C 下进行 1000 s 的 HCS 评估后,阈值电压为 3.5 V。此外,阈值电压在正方向上不断变化,总变化量(ΔV th) 的 3.5 V。亚阈值摆幅 (SS) 值从 0.09 略微增加到 0.16 V/dec。对于 BCE 结构的 TFT,阈值电压要高得多,即 25 °C 时为 4.0 V,在 60 °C 下进行 HCS 评估 1000 s 后,阈值电压增加到 11.2 V。这些高阈值电压的一个可能原因是 Cu + 的扩散 在 BCE 工艺的湿蚀刻工艺期间进入 a-IGZO 膜。铜 + 可以作为 a-IGZO 薄膜中的受体型缺陷位点,以及高密度的 Cu + 可以俘获大量电子。被俘获的电子产生屏蔽库仑电位,导致瞬态阈值电压偏移现象。通常,栅极绝缘体块体和 a-IGZO 膜块体内部新形成的缺陷位点可以增加 TFT 的 SS 值 [11]。这些结果清楚地解释了 I BCE 结构 TFT 中的 ds 剩余电流。然而,BCE 结构的 TFT 的 SS 值显示出从 0.46 下降到 0.24 V/dec 的趋势。这种降低的 SS 值是由于电子在 a-IGZO 界面附近积累造成的,之后栅极绝缘体可以迅速填充最初存在的受体型陷阱位点的高能级。此外,陷阱位点的填充速度比 HCS 产生的要快,因此,被困电子的数量随着时间的推移逐渐减少。这与阈值电压的正向偏移行为一致。

<图片>

我 -V 在 a 的 HCS 评估期间测量的传递特性 CL-ES 和 b BCE 结构的 GOA TFT。 c 的行为 阈值电压和 d 以 1000 s 和 V 为间隔的亚阈值摆动 ds =15 V. I 的初始测量值 d -V d e 的输出特性 CL-ES- 和 f 具有 V 的 BCE 结构的 GOA TFT gs =0、5、10、15 和 20 V

至于CL-ES特性的均匀性,因为ESL提供了Cu + 的主动反向通道保护 污染和蚀刻剂损坏,其结果与 BCE 相比是稳定的。此外,应该注意的是,输出曲线的特性显示出 BCE 没有差异,并且可以保证 CL-ES 的生产和稳定性(表 2,图 7e,f)。

图 7 c 和 d 显示了亚阈值摆动和阈值电压行为以及 HCS 评估进程的结果。通常,GOA TFT 的亚阈值摆动值逐渐增加,如 CL-ES 结构的 TFT(图 7d)所示。然而,BCE 结构的 TFT 表现出异常行为,亚阈值摆动值最初增加,随后在 HCS 评估期间减少。当衬底温度从 25°C 增加到 60°C 时,BCE 结构 TFT 的 SS 值从 0.46 V/dec 增加到 0.55 V/dec。同时,阈值电压从 4.0 负移至 2.9 V(图 7c)。这种异常现象是由于添加了氟化物的 H2O2 蚀刻剂损坏了 a-IGZO 膜表面。如前所述,a-IGZO 薄膜的表面损伤意味着缺乏 Zn、Ga 和氧原子,从而形成许多缺陷位点,包括氧空位。据信,这些缺陷位点作为浅供体状态是活跃的,接近最小导带,并且能够热激发并充当导带的电子源,导致 a- IGZO TFT 特性。基于上述结果,CL-ES结构的TFT具有小受体态和氧缺陷作为浅供体态,是比BCE结构TFT更好的结构。

结论

总之,我们证明 CL-ES 结构的 GOA TFT 具有减小的器件特征尺寸和干净的蚀刻停止层,可以显着提高器件性能和稳定性。通过所提出的 CL-ES 结构的 TFT 制造工艺,TFT 背沟道的损坏和污染被最小化。此外,对于与BCE结构的GOA TFT相同的集成度,CL-ES结构的TFT工艺可以满足美学设计和制造成本效率的目标。与 BCE 结构的 GOA TFT 相比,CL-ES 结构的 GOA TFT 显示出优异的电气性能,包括更高的残余离子电流(~ 187%)、更低的初始 SS 值(0.09 V/dec)和低得多的阈值电压变化 (3.5 V)。这意味着具有更高集成度和可靠性的 GOA 设计的可能性。增强的性能和稳定性表明 CL-ES 结构的 TFT 具有简化的工艺和干净的蚀刻停止层,成功克服了由氧缺乏引起的类施主缺陷和由 Cu + 引起的类受体缺陷 BCE 过程中的扩散。因此,CL-ES结构TFT中a-IGZO沟道区的清洁表面成分对于生产具有高可靠性、高分辨率和窄边框显示器的a-IGZO TFT背板非常重要。

缩写

- TFT:

-

薄膜晶体管

- GOA:

-

阵列上的栅极驱动 IC

- a-IGZO:

-

无定形铟镓锌氧化物

- LCD:

-

液晶显示器

- PEVCD:

-

等离子体增强化学气相沉积

- ESL:

-

蚀刻阻挡层

- BCE:

-

背道蚀刻

- HCS:

-

高电流应力

- SiOx:

-

氧化硅

- SiNx:

-

氮化硅

- SS:

-

亚阈值摆动

纳米材料

- 使用蓝牙网状网络进行设计:节点和特征类型

- MCU 具有增强的性能、连接性和安全性

- 利用机器学习提高可靠性并改善维护结果

- 结构和类的区别:用 C++ 示例解释

- 螺旋型天线微桥结构太赫兹微测辐射热计的调频和吸收改进

- 具有 GeSiSn 纳米岛和应变层的半导体薄膜的形态、结构和光学特性

- 通过蚀刻停止纳米层使用清洁界面工艺增强 a-IGZO TFT 器件性能

- 通过氩等离子体处理插入 ZnO 降低金属和 n-Ge 之间的接触电阻

- 具有增强型双栅极和部分 P 埋层的超低导通电阻横向双扩散金属氧化物半导体晶体管

- 对亚甲基蓝具有显着增强吸附性能的分级结构高岭石纳米球

- 通过原子层沉积制造的用于具有增强电容的超级电容器电极的 TiO2 纳米膜

- IBM:通过 EAM 主动确保可靠性和安全性