通过蚀刻停止纳米层使用清洁界面工艺增强 a-IGZO TFT 器件性能

摘要

为了克服用于工业生产的非晶铟镓锌氧化物 (a-IGZO) 基显示器背板的技术和经济障碍,开发了一种清洁蚀刻停止 (CL-ES) 工艺来制造基于 a-IGZO 的薄板在第 8.5 代玻璃基板(2200 毫米 × 2500 毫米)上具有改进的均匀性和再现性的薄膜晶体管 (TFT)。与具有背沟道蚀刻 (BCE) 结构的基于 a-IGZO 的 TFT 相比,新形成的 ES 纳米层 (~ 100 nm) 和同时蚀刻 a-IGZO 纳米层 (30 nm) 和源漏电极层首先被引入到具有CL-ES结构的a-IGZO基TFT器件中,以提高大面积显示器件的均匀性和稳定性。 8.05 cm 2 的饱和电子迁移率 /V s 和 V 在具有 CL-ES 结构的基于 a-IGZO 的 TFT 器件上实现了 0.72 V 的均匀性。在a ± 30 V偏压下3600 s的负偏压温度光照应力和正偏压热应力可靠性测试中,测得的V CL-ES 结构器件的 th 位移显着降低至 - 0.51 和 + 1.94 V,远低于 BCE 结构器件(- 3.88 V,+ 5.58 V)。具有CL-ES结构的a-IGZO基TFT器件的电气性能意味着从基于硅的TFT工艺到基于金属氧化物半导体的LCD制造工艺的经济转移是非常可行的。

背景

具有更高分辨率和更大面板尺寸的薄膜晶体管 (TFT) 背板在平面显示行业中非常受欢迎。具有高电子迁移率的半导体材料对于提高 TFT 背板的性能至关重要。特别是,基于金属氧化物半导体的 TFT 背板被认为是克服硅基 TFT 背板在机械柔韧性和电子迁移率方面的局限性的有希望的候选者 [1,2,3,4]。尽管基于金属氧化物半导体的TFT背板显示出良好的性能,但仍需要一种低成本的工艺方法,可用于工业应用的大规模沉积[5]。

非晶铟镓锌氧化物 (a-IGZO) 是一种优异的金属氧化物半导体,具有高饱和电子迁移率 (~ 5–10 cm 2 /V s) 和低截止电流 (<10 pA) [6,7,8,9,10]。 a-Si:H 基 TFT 背板的常见工业生产方法是五掩模背沟道蚀刻 (BCE) 工艺。然而,a-IGZO 纳米薄膜对目前 BCE 工艺中使用的典型蚀刻剂的耐化学性非常低。特别是,a-IGZO 纳米薄膜暴露在由磷酸、硝酸和乙酸组成的铝蚀刻剂中时,会在几秒钟内被完全蚀刻 [11,12,13]。这种无法控制的快速蚀刻阻碍了基于 a-IGZO 的 TFT 背板采用 BCE 工艺。为了在 BCE 结构背板中使用 a-IGZO,已开发出 Cu 布线技术,因为 Cu 布线工艺中使用的蚀刻剂基于 H2O2,比 Al 布线中使用的蚀刻剂对 a-IGZO 纳米膜温和得多[11, 13]。不幸的是,即使使用较温和的蚀刻剂,a-IGZO 纳米膜在 Cu 布线过程中仍然会损坏。即使是较温和的蚀刻剂也会对形成 TFT 器件背沟道的 a-IGZO 纳米薄膜的表面造成损坏。这些损伤导致a-IGZO纳米薄膜表面附近的化学计量分子组成比崩溃,导致大面积显示的均匀性和TFT器件的可靠性恶化。迄今为止,开发了传统的六掩模蚀刻停止层 (CV-ES) 工艺来制造具有蚀刻停止层 (ESL) 结构的基于 IGZO 的 TFT 背板 [14, 15]。然而,这种六掩模 ES 工艺可能会导致负面的经济可行性。此外,薄膜层数的增加会增加层间重叠面积,导致寄生电容增加和开口率降低 [16,17,18]。尽管最近报道了使用半色调和剥离技术生产 TFT 背板的五掩模 ES 工艺,但该工艺无法用于生产基于 a-IGZO 的 TFT 背板,因为它们的有源层表面仍暴露于在最后一步使用剥离剂和光刻胶等工艺化学品,可能会对 a-IGZO 造成相当大的污染,从而降低器件质量和产量 [19,20,21]。因此,具有高度均匀性和稳定性的a-IGZO基TFT背板的工业化生产方法仍然具有挑战性。

在本文中,我们通过引入 ESL 来制造基于 a-IGZO 的 TFT 背板,提出了一种清洁的五掩模 ES 工艺(CL-ES)。这种新开发的 CL-ES 工艺与 BCE 设备的现有工艺高度兼容。这种 CL-ES 工艺设计为具有与 BCE 工艺相同的掩膜,确保现有 AM-LCD TFT 背板 FAB 的生产力损失可以忽略不计。使用CL-ES工艺生产的a-IGZO基背板依次沉积栅极绝缘体、IGZO纳米层和ES纳米层,然后通过干蚀刻方法形成新的ESL掩模。这可以防止 a-IGZO 纳米层及其界面受到蚀刻剂、剥离剂和溶剂的污染。这种新形成的纳米掩模有助于提高 TFT 器件的均匀性和稳定性。与传统的BCE结构器件相比,具有CL-ES结构的a-IGZO基器件显示出增强的电学性能,即更高的饱和电子迁移率、高开口率和低功耗。

方法/实验

基于 IGZO 的 TFT 背板的制造

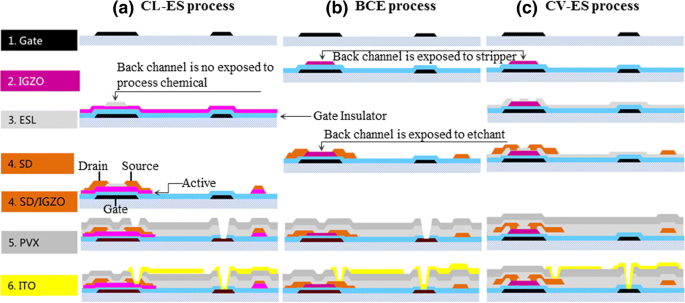

通过CL-ES工艺制作的具有ES结构的a-IGZO基TFT背板如下(图1)。

<图片>

(Color online) a 的示意图 CL-ES,b BCE 和 c CV-ES流程

首先,双层(Mo/Cu:30 nm/250 nm)用于栅电极,因为它具有相当低的电阻率。然后,通过等离子体增强化学气相沉积 (PECVD) 方法沉积栅极绝缘体、氮化硅 (SiNx)/氧化硅 (SiOx) (300 nm/100 nm)。该 SiNx 膜旨在防止 Cu 金属化和 Cu 离子扩散到栅极绝缘体中。随后,沉积SiOx薄膜。 PECVD SiOx 薄膜的沉积条件为 17-KW RF 功率、1000 mTorr 压力、1:55 SiH4/N2O 气体比和 350°C 温度。然后,使用直流旋转磁控管溅射将 a-IGZO 纳米膜沉积到 30 nm。靶的直径为 171 毫米,而组成为 In2O3:Ga2O3:ZnO =1:1:1 mol%。 a-IGZO纳米薄膜的溅射参数为5~ 9 × 10 -7 Torr,射频溅射功率为 10 千瓦,溅射压力为 5 毫托 Ar/O2 气体混合物(85% Ar-15% O2)。沉积温度在室温条件下。生产的 a-IGZO 薄膜在清洁干燥的空气环境中在 330°C 下退火 1 小时。

其次,使用PECVD方法沉积蚀刻停止(ES)纳米层(SiOx)。同时沉积 ES 纳米层以防止 a-IGZO 层中的污染。与BCE工艺一样,在S/D电极构图工艺之前,a-IGZO纳米膜没有保护层,表面污染,形成TFT沟道时S/D刻蚀剂对a-IGZO纳米膜的损伤在所难免。 CL-ES 工艺中的 ES 纳米层可以有效保护 TFT 通道免受外部污染和损坏。 ES纳米层被沉积到100nm的厚度。 SiOx 薄膜的沉积条件为 17-KW RF 功率、1000 mTorr 压力、1:66 SiH4/N2O 气体比和 240°C 温度。通过干蚀刻和图案化来蚀刻产生的 ES 纳米掩模。在蚀刻过程中,CF4和O2气体以2000 sccm/800 sccm的速率供应。

第三,Mo/Cu/Mo 也用于 S/D 电极。为了选择 a-IGZO TFT 的 S/D 电极,考虑了金属和 a-IGZO 之间的功函数差异,以形成欧姆接触和低电阻率材料。如止蚀工艺中所述,在 ES 纳米掩模的构图过程中,未受到止蚀层保护的 a-IGZO 纳米薄膜已经通过 CF4 等离子体的轰击进行了处理。因此,欧姆接触与 Mo/Cu/Mo 自然形成[22]。 S/D 层以 30 nm/300 nm/30 nm 的厚度沉积,溅射条件与栅电极相同。此外,使用“含有氟化物添加剂的 H2O2 基 Cu 蚀刻剂”批量蚀刻 Mo/Cu/Mo 和 a-IGZO 的多薄膜层以完成 S/D 电极。在Cu顶部添加30nm的Mo,以防止后续工艺中的钝化膜(SiOx)对Cu表面的氧化,并防止在干蚀刻钝化孔形成过程中对Cu表面的等离子体损伤。

第四,采用PECVD方法沉积钝化膜,分为两种薄膜。第一个钝化层由 SiOx 薄膜制成。薄膜厚度为 250 纳米。第二钝化层由 SiNx 薄膜构成。薄膜厚度为200纳米。

第五,作为像素电极,采用了显示行业最常用的氧化铟锡(ITO)薄膜。 ITO 膜厚 40 纳米,使用直流溅射进行沉积。然后,使用热风炉在 230°C 的清洁干燥空气环境中进行最终退火 1 小时。使用 Keysight 4082A 参数测试系统测量制造的 a-IGZO TFT 的电气特性。该工艺将获得与BCE工艺相同数量的掩膜(TN产品标准:五个掩膜),广泛用于批量制造。

作为对比,采用BCE工艺制作了具有BCE结构的a-IGZO基TFT背板。

特征化

TFT 的 I-V 测量是在室温下使用半导体特性分析仪进行的。评估 TFT 在负栅极偏置温度照明应力 (NBTIS) 下的稳定性的分析条件如下。 V gs 和 V ds分别固定在- 30和15 V,底物温度保持在60°C。 NBITS 的亮度设置为 5000 cd/m 2 .评估压力持续时间为 3600 秒 [23]。在 V 下测试正栅极偏置热应力 (PBTS) gs 为 30 V 和 V ds 为 15 V,基板温度设置为 60 °C。评估压力持续时间为 3600 s [24]。

结果与讨论

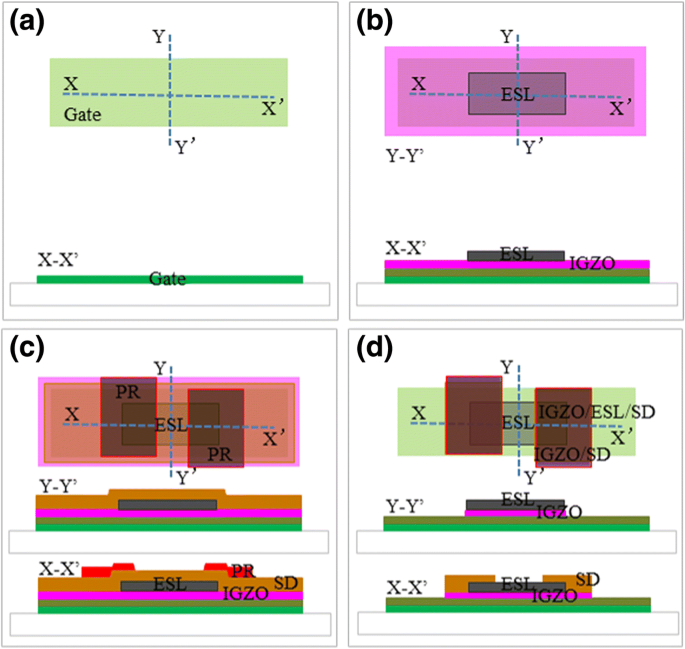

通过 CL-ES 工艺制造的基于 a-IGZO 的 TFT 显示出与 BCE 工艺相同的掩模编号(图 1)。与BCE结构的a-IGZO-based TFT相比,CL-ES结构的a-IGZO-based TFT显示出两个优点:(1) 使用CL-ES工艺生产的a-IGZO-based背板沉积栅极绝缘体,a-IGZO nano -层,ES纳米层,然后通过干蚀刻法形成ESL纳米掩模。这种新形成的 100 nm ESL 纳米掩模可以防止 a-IGZO 纳米膜暴露于蚀刻剂、剥离剂或光刻胶。因此,有效防止了层间界面的污染[25]。 (2) 同时,a-IGZO 纳米薄膜在 ESL 纳米掩模形成过程中不受 ES 层保护,而是受到 CF4 等离子体的轰击,从而成为导体。这自然形成了后续工艺的 S/D 电极和 a-IGZO 半导体之间的欧姆接触。另一方面,S/D和a-IGZO纳米层的同时刻蚀可以作为ESL-(a-IGZO+S/D金属化)层的一个重叠余量,可以减少a-的两次重叠工艺误差。传统 ESL 工艺中的 IGZO-ESL 和 ES-S/D 金属化层(图 2)。 a-IGZO、ES和S/D层的重叠数量减少,导致TFT器件尺寸减小,从而降低了寄生电容。结果平面结构类似于BCE结构(图3a,b)。

<图片>

(Color online) CL-ES工艺TFT通道与S/D电极同时形成方法示意图。 一 第一步,形成栅电极。 b 第二步,形成蚀刻停止层。 c 第三步,形成 S/D 照片图案。 d 第四步形成S/D电极和有源图形

<图片>

(彩色在线)a-IGZO TFT (a , b 顶视图; c , d 侧视图)具有 CL-ES 结构(a , c ) 和 BCE 结构 (b , d )

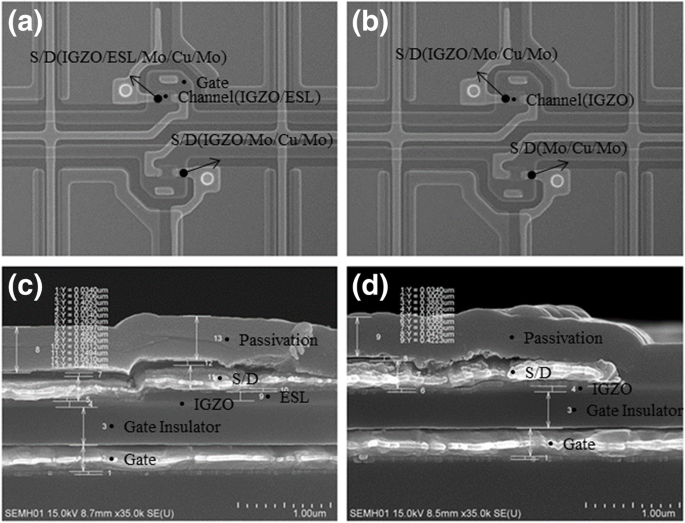

图 3 显示了具有 CL-ES 结构(图 3a、c)和 BCE 结构(图 3b、d)的基于 a-IGZO 的 TFT 的 SEM 图像。从俯视图来看,很难区分 CL-ES 结构和 BCE 结构之间的差异(图 3a、b)。从侧面看,在 CL-ES 结构中,在 a-IGZO 纳米层和 S/D 电极层之间可以发现 ES 纳米层(图 3c)。同时,在 BCE 结构的 a-IGZO 纳米层的顶部可以找到钝化层(图 3d)。在所提出的 CL-ES 工艺中,沉积了厚度为 30 nm 的 a-IGZO 纳米层。此外,湿蚀刻过程中的损坏可以忽略不计。对于 BCE 工艺,沉积 70-nm a-IGZO 纳米层,因为 a-IGZO 层需要补偿蚀刻损失。在 SEM 图像中可以观察到 CL-ES 和 BCE 结构中 a-IGZO 纳米层的厚度差异(图 3c、d)。

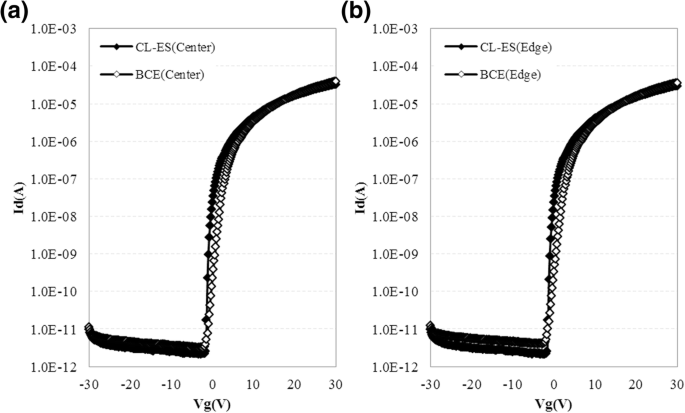

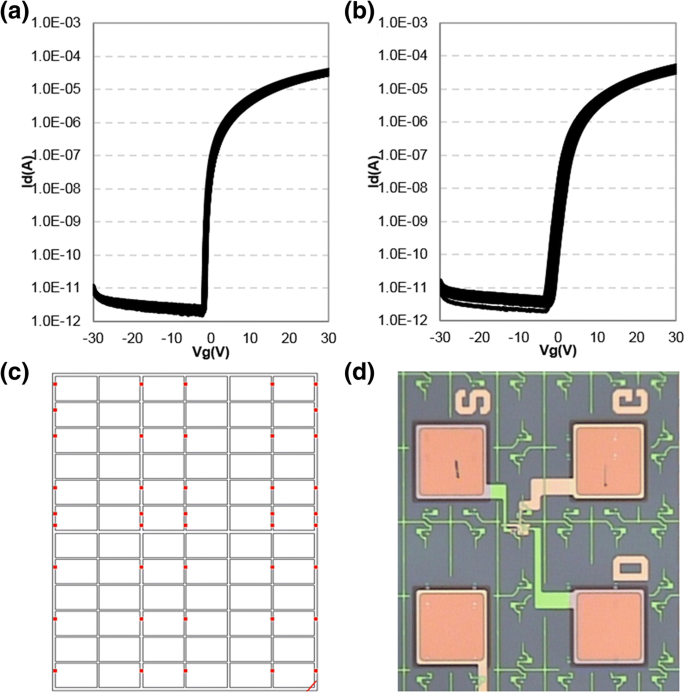

比较了具有 CL-ES 结构和 BCE 结构的基于 a-IGZO 的 TFT 的 I-V 特性(图 4)。饱和电子迁移率、阈值电压、亚阈值电压摆幅 (SS) 值和更多特征值汇总在表 1 中。请注意,表 1 中汇总的值是来自 8.5 代玻璃基板中心和边缘的平均数.具有CL-ES结构的a-IGZO基TFT实现V − 0.8 V 的 th,SS 值为 0.18 V/dec,饱和电子迁移率为 8.05 cm 2 /V 秒。在具有BCE结构的a-IGZO基TFT中,对应的结果为V + 0.5 V 的 th,SS 值为 0.77 V/dec,饱和电子迁移率为 6.03 cm 2 /V 秒。与 BCE 结构相比,CL-ES 结构显示出改进的器件性能。然而,具有 CL-ES 结构的基于 a-IGZO 的 TFT 器件的导通电流特性低于具有 BCE 结构的器件。这是因为 CL-ES 和 BCE 结构中的 TFT 通道结构不同。通常,BCE 结构的 TFT 通道长度是 S/D 金属电极之间的距离,本研究中测量的通道长度为 5 um [21]。在 CL-ES 结构中,电极与在 ESL 纳米掩模侧面拉伸的 a-IGZO 纳米薄膜接触。因此,沟道长度由在蚀刻停止层两侧定义的 a-IGZO 之间的距离决定,而不是由电极之间的距离决定。本 CL-ES 结构器件的沟道长度实测为 10 um。

<图片>

(Color online) 以 CL-ES 和 BCE 结构为中心的 a-IGZO TFT 的 I-V 特性比较 (a ) 和边 (b ) 8.5代玻璃基板

如表 1 所示,I 的测量值 在/我 关闭率 (~ 10 6 ,见表 1) 大约比典型值小 10 倍 (> 10 7 ) 基于 a-IGZO 的 TFT。这是因为这里使用的测量设备是针对8.5代量产的。这些测量需要长电缆,因为工业设备的尺寸很大。长电缆导致测量噪声增加。在接下来的可靠性测试中,使用了较小规模的测量设备,并以单个 TFT 器件作为测量样本。这样,测得的I 在/我 关闭比率都是上 10 7 (见下文)。

CL-ES 工艺经过精心设计,可防止 a-IGZO 沟道层暴露于蚀刻剂、光刻胶或剥离剂。在生产CL-ES工艺、栅极绝缘体、a-IGZO纳米层和ES纳米层的过程中,每个层间界面仅与去离子水接触以进行清洁。因此,绝缘体层和 a-IGZO 纳米层中的化学污染可以忽略不计 [25, 26]。然而,BCE 工艺不仅将通道层暴露于化学品中,而且还涉及 Cu 离子扩散污染,因为 a-IGZO 通道直接暴露于 Cu 金属。这在具有 CL-ES 结构的设备中也可以避免。 a-IGZO 纳米薄膜的沟道区受到 ESL 纳米掩模的良好保护。 CL-ES 工艺中的低化学污染可能导致 a-IGZO 纳米层和绝缘体层之间界面处的载流子陷阱密度低,从而导致优异的 SS 值。 CL-ES工艺对a-IGZO基TFT器件的这种低化学污染也有助于提高a-IGZO TFT的均匀性和再现性,这在工业生产中非常重要[27, 28]。

图 5 显示了从 8.5 代基板上的 42 个测量点得出的具有 CL-ES 结构和 BCE 结构的 TFT 的测量 I-V 特性。具有 CL-ES 结构的基于 a-IGZO 的 TFT 具有 V th 范围为 0.72 V,而 BCE 结构器件的范围为 2.14 V(表 1)。也就是说,CL-ES结构显着提高了器件性能的均匀性。

<图片>

(颜色在线)a CL-ES 结构。 b BCE 结构的 TFTs I-V 传输特性。 c 42个测量点。 d TFT的照片。均在 8.5 代基板上测量

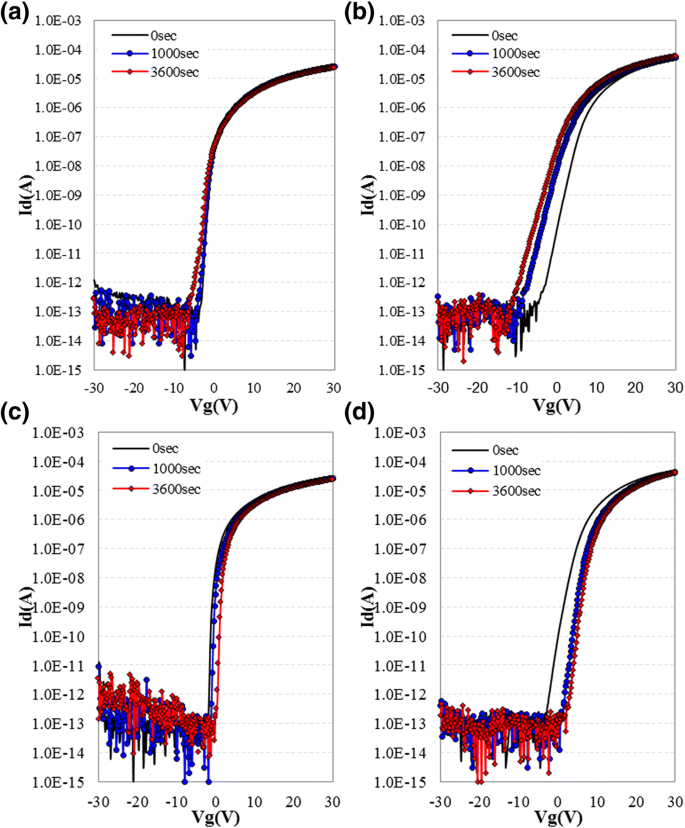

图 6a、b 分别显示了在 NBTIS 测试中获得的 CL-ES 结构器件和 BCE 结构器件的 I-V 特性偏移。 NBTIS 测试结果总结在表 2 中。在表 2 描述的应力条件下,V CL-ES 结构器件和 BCE 结构器件的 th 位移分别为 - 0.51 和 - 3.88 V。此外,CL-ES 结构器件的导通电流偏移、截止电流偏移和 SS 值方差均低于 BCE 结构器件(表 2);这是因为具有 CL-ES 结构的基于 a-IGZO 的器件可以有效防止 a-IGZO 的污染和降低 a-IGZO TFT 通道的载流子陷阱密度。特别是,当查看前 1000 秒应力的结果时,在 CL-ES 结构的器件中没有观察到 SS 值变化。这种现象与 BCE 结构器件的 SS 值增加 0.16 V/dec 相当,因为它表明缺陷位点可以在构成 CL-ES TFT 背沟道的 a-IGZO 纳米膜表面形成载流子陷阱,不是由电和光照应力额外产生的。这些结果充分证明CL-ES结构的器件比BCE结构的器件稳定得多。图 6c、d 显示了从 PBTS 测试获得的 CL-ES 和 BCE 结构的 TFT 的 I-V 曲线偏移。详细的 PBTS 测试结果总结在表 3 中。在 PBTS 评估过程中,CL-ES 结构的 TFT 和 BCE 结构的 TFT 都降低了离子电流。这是由 V 的偏移引起的 th 向正方向。在 PBTS 评估期间,具有相对较小 V 的 CL-ES 结构 TFT 的残余离子电流比 [(最后一个离子/初始离子) × 100] th 正移 (+ 1.94 V) 处于 88.2% 的水平。与 BCE 结构 TFT 的 41.3% 的残余离子电流比相比,CL-ES 结构的 TFT 明显优越。这显示了在阵列上的栅极驱动 (GOA) 电路设计过程中的重要容量差异。与 NBTIS 不同,CL-ES 结构的 TFT 的 SS 值没有显着变化((ΔSS 0.06 V/dec),或者像 BCE 结构的 TFT 一样降低(ΔSS - 0.86)。这可能是由于载流子通过正栅偏压在栅绝缘体和a-IGZO纳米薄膜的内部空间和界面处积聚,在早期填充载流子陷阱位,导致载流子陷阱现象减少。载流子电荷被困在栅极绝缘体和 a-IGZO 纳米膜之间的界面附近。CL-ES 结构的 TFT 的小阈值电压漂移表示 a-IGZO 的界面和内部空间非常干净。总之,PBTS 测试也表明CL-ES结构和工艺导致更好的器件可靠性。

<图片>

(Color online) CL-ES 的 I-V 传递特性漂移 (a , c ) 和 BCE (b , d ) 从 NBITS (a , b ) 和 PBTS 测试 (c , d )

结论

总之,新开发的 CL-ES 工艺已成功开发用于制造具有五个掩模的基于 a-IGZO 的 TFT 背板,用于高级显示。 CL-ES工艺具有蚀刻阻挡层结构的优点,同时保持与BCE工艺相同的掩膜数量和相似的器件面积,克服了传统蚀刻阻挡TFT器件增加掩膜数量和占用面积的问题.新形成的 ESL 纳米掩模和 a-IGZO 纳米层和 S/D 电极纳米层的同步蚀刻使大面积显示器件具有高均匀性和稳定性。在电性能方面,CL-ES结构的a-IGZO基TFT器件性能的再现性和可靠性远优于BCE结构的器件。基于a-IGZO的TFT器件具有V 8.5 代玻璃基板上 42 个测点 TFT 的 th 分布,电压为 0.72 V,饱和电子迁移率为 8.05 cm 2 /V s,SS 值为 0.18 V/dec。根据 NBTIS 和 PBTS 获得的可靠性评估结果,V 基于 CL-ES a-IGZO 的 TFT 在应力之前和之后的 th 方差在 3600 秒应力之后分别为 - 0.51 和 1.94 V。 SS 值差异为 0.33 和 0.06 V/dec。因此,通过克服技术和经济障碍,所提出的CL-ES技术将为下一代高分辨率和大面板显示产品铺平道路。

缩写

- a-IGZO:

-

无定形铟镓锌氧化物

- AM-LCD:

-

有源矩阵液晶显示器

- BCE:

-

背道蚀刻

- ESL:

-

蚀刻阻挡层

- GOA:

-

阵列上的栅极驱动

- NBTIS:

-

负偏压温度光照应力

- PBTS:

-

正偏置温度应力

- SiNx:

-

氮化硅

- SiOx:

-

氧化硅

- SS:

-

亚阈值摆动

- TFT:

-

薄膜晶体管

- TN LCD:

-

扭曲向列液晶显示器

纳米材料