具有增强型双栅极和部分 P 埋层的超低导通电阻横向双扩散金属氧化物半导体晶体管

摘要

超低比导通电阻 (R 本文提出并研究了 on,sp) 具有增强型双栅极和部分 P 埋层的横向双扩散金属氧化物半导体晶体管 (LDMOS)。所提出的 LDMOS 的导通电阻分析模型旨在深入了解漂移区电阻和沟道区电阻之间的关系。在 P 阱下引入 N 埋层,以提供低电阻传导路径并显着降低沟道区的电阻。增强型双栅极结构由 N 埋层形成,同时避免关断状态下的垂直穿通击穿。 N-漂移区下方采用长度优化的部分P-埋层,扩展垂直耗尽区,缓和截止状态下的电场峰值,提高击穿电压(BV),漂移区电阻低。对于具有增强型双栅和部分 P 埋层的 LDMOS,结果表明 R on,sp 为 8.5 mΩ·mm 2 而 BV 是 43 V。

背景

随着模拟电源 IC 对更复杂、更快速的逻辑功能需求的增加,提高横向双扩散金属氧化物半导体晶体管 (LDMOS) 的性能,特别是最小化比导通电阻 ( on,sp) 并最大化断态击穿电压 (BV) [1,2,3,4,5,6,7,8,9]。大多数开发的技术都专注于优化漂移区域以改善 R 的权衡 LDMOS 器件的 on,sp 与 BV [10,11,12,13,14,15,16,17,18,19,20]。在我们之前的工作中,提出了具有超浅沟槽隔离 (USTI) 的 LDMOS [21]。 USTI 的深度和角角经过优化,以实现一流的性能。然而,对于低压 LDMOS,漂移区在 R 中失去了主导地位 on,sp 和沟道区的贡献不容忽视。

方法

在这项工作中,研究了一种具有增强型双栅极和部分 P 埋层的新型超低比导通电阻 LDMOS。物理模型 IMPACT.I、BGN、CONMOB、FLDMOB、SRH 和 SRFMOB 用于数值模拟。提出导通电阻分析模型以深入了解漂移区电阻和沟道区电阻之间的关系。基于该模型,优化N埋层和部分P埋层以实现低R on、sp 和高 BV。

结果与讨论

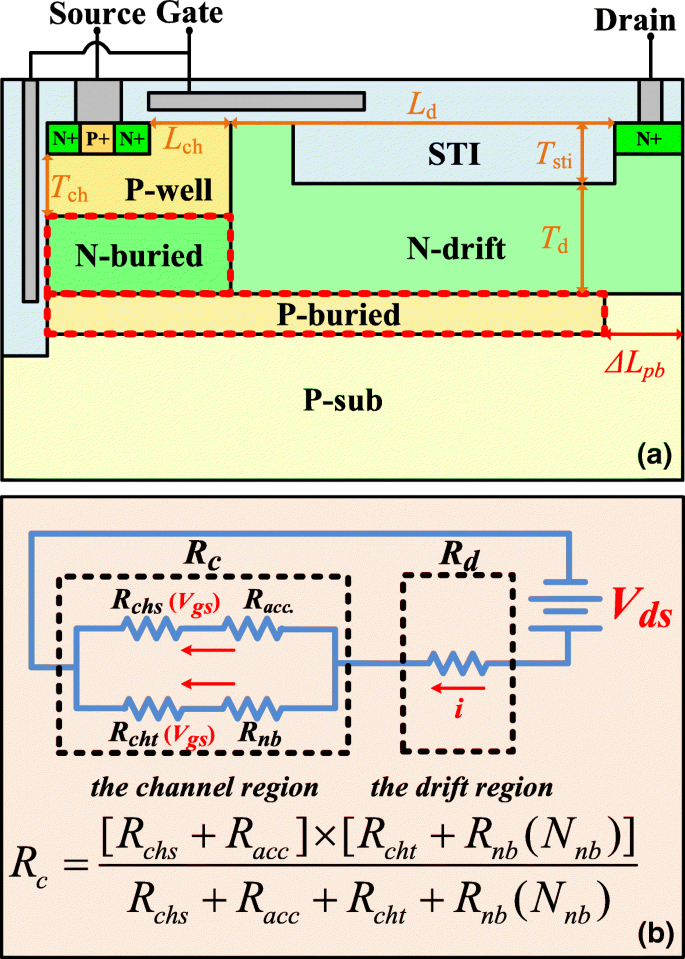

图 1a 显示了具有增强型双栅极和部分 P 埋层的超低比导通电阻 LDMOS 的横截面示意图。 LDMOS 具有双栅极 N 埋层和部分 P 埋层,有助于降低 R on,sp 和增强 BV,分别。在沟道区,增强型双栅由沟槽栅和高掺杂N埋层构成。与传统的双栅极结构相比,N 埋层通过在导通状态下在 P 阱下方提供低导通电阻传导路径,显着降低了沟道区的电阻。在漂移区,在N漂移区下方引入部分高掺杂浓度的P埋层,以提高BV,同时保持低R 在,sp。部分 P 埋层有助于降低截止状态下的垂直电场,而不会破坏漂移区的电荷平衡。表 1 列出了新型设备的密钥大小。

<图片>

一 具有增强型双栅极和部分 P 埋层的超低比导通电阻 LDMOS 的横截面示意图。 b LDMOS等效导通电阻示意图

图 1b 显示了所提出的 LDMOS 的等效导通电阻模型示意图。总导通电阻被认为是漂移区的电阻 (R d) 和沟道区的电阻 (R c) 串联。在沟道区,表面沟道传导路径与沟槽沟道传导路径平行。因此,R c 等于 (R chs + R acc)//(R cht + R nb),其中 R chs, R ACC,R cht 和 R nb 分别是表面栅极沟道、累积区、沟槽栅极沟道和 N 埋层的电阻。基于所提出的导通电阻模型,R的减少 c 将通过减少 R 来实现 nb 不影响其他性能,因为其他电阻主要由工艺技术、工作电压和阈值电压决定。 R 在我们之前的工作中,通过在 N 漂移区域下引入 P 埋层以增强减少表面场 (RESURF) 效应,d 已被减少。在这项工作中,采用部分 P 埋层来提高 BV,同时保持低 R d.

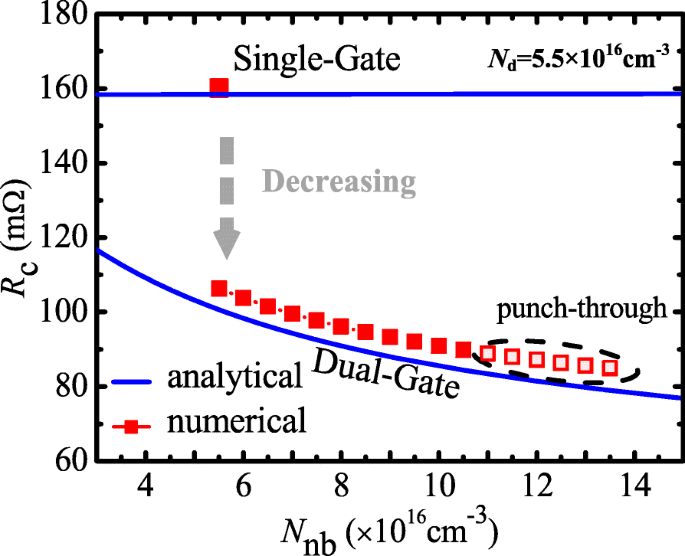

旨在减少R c、在P-well下引入高掺杂浓度的N埋层。图 2 显示了数值和解析 R c 作为 N 埋层掺杂浓度的函数 (N nb) 具有单门和双门。表明双栅结构有助于降低R c 与单门相比。当 N nb =N d =5.5 × 10 16 厘米 −3 , R c 是 110 毫欧。根据导通电阻模型,R nb 是 R 的主要贡献者 C。然后,R 为了减小 R,希望 nb 减小 C。如图 2a 所示,R c 用 N 减少 nb 增加。当 N nb =1.35 × 10 17 厘米 −3 , R c 降至 85 mΩ。然而,图 2 也表明 N nb 会受到穿通击穿的限制。由于增加了沟槽栅,R c首先随着N下降34% nb =N d =5.5 × 10 16 厘米 −3 .作为 N nb 增加,R c 持续减少。使用优化的 N nb =1.05 × 10 17 厘米 −3 , R c 最终降低了 45%。当 N nb> 1.05 × 10 17 厘米 −3 ,P 阱会发生穿通击穿。 R的分析结果 图 2 所示的 on,sp 表明所提出的模型与数值模拟结果很好地拟合。因此,该模型具有指导优化设计的可信度。

<图片>

数值和分析 R c 作为 N 的函数 nb 具有单门和双门 (Z =1 厘米)。 N d 为 N 漂移区的掺杂浓度

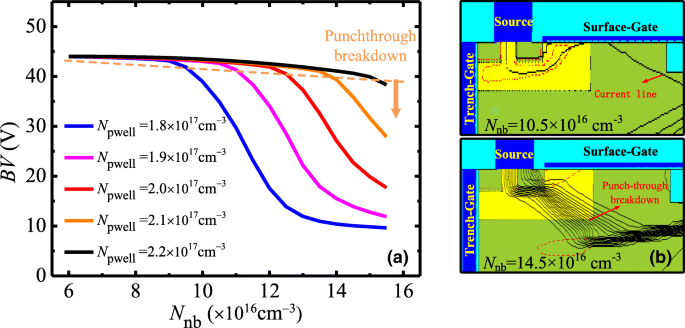

图 3a 显示了数值 BV 作为 N 的函数 nb 具有不同掺杂浓度的 P 阱 (N 井)。 N nb 不仅对 R 有影响 c,也是BV。对于给定的 N pwell,BV 保持在小 N 不变 nb,然后随着 N 减小 nb 增加。当 N nb 增加到 1.2 × 10 17 厘米 −3 , BV 以 N 开始下降 pwell =2 × 10 17 厘米 −3 . BV 的下降归因于 P 阱区域中的穿通击穿,如图 3b 所示。随着漏极电压的增加,P 阱中的耗尽区延伸到源极。当耗尽区攻击 N+/P 阱结时,就会发生穿通击穿。对于大 N pwell,耗尽区主要延伸到漂移区,在不降低 BV 的情况下避免了穿通击穿。尽管具有高掺杂浓度的 P 阱有利于避免穿通击穿,但它会提高阈值电压。因此,N 2 × 10 17 的pwell 厘米 −3 选择考虑阈值电压和 BV 和 R 之间的权衡 在,sp。

<图片>

一 作为 N 函数的数值 BV nb 具有不同的 N 普威尔。 b N 的电流密度分布 nb =10.5 × 10 16 厘米 −3 和 14.5 × 10 16 厘米 −3 而 N pwell =2 × 10 17 厘米 −3 崩溃时

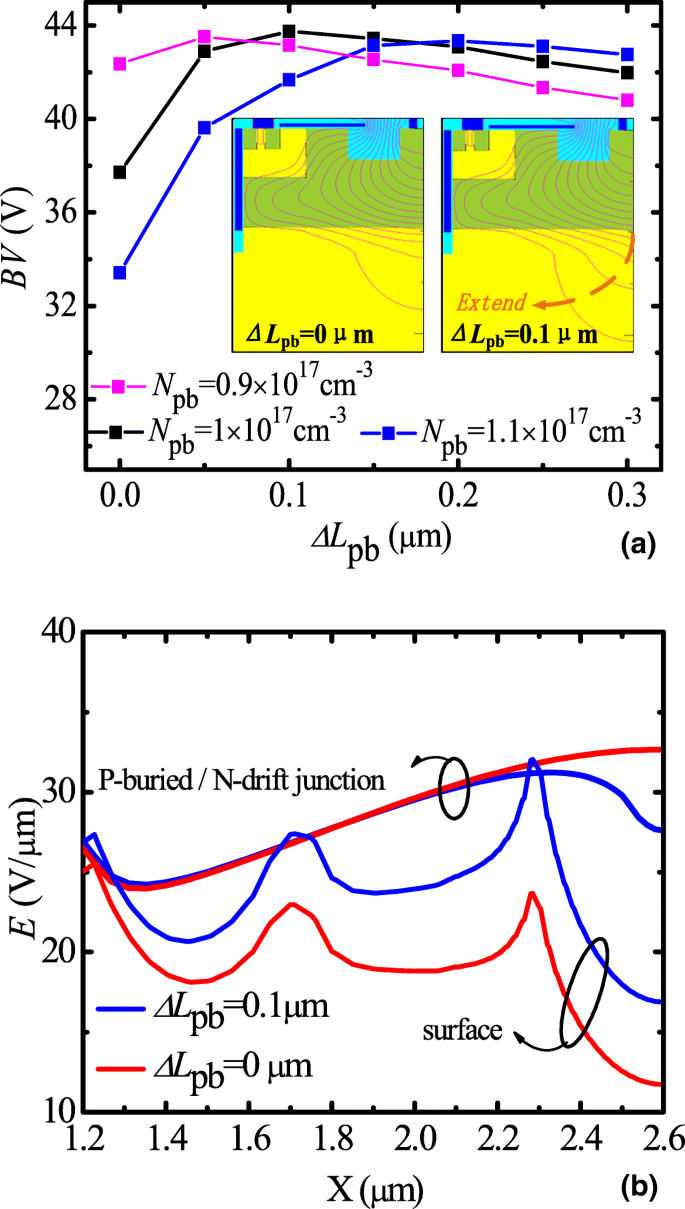

为了实现低R d 和高 BV,在 N 漂移区下方引入部分 P 埋层。图 4a 显示了 BV 作为 ΔL 的函数 具有不同 N 的 pb 铅对于给定的 N pb, ΔL pb 增加,BV 增加然后略有下降。当ΔL pb =0.1 μm, N pb =1 × 10 17 厘米 −3 , BV 达到最大值 43 V. 插入显示带有 N 的等电位轮廓轮廓 pb =1 × 10 17 厘米 −3 .结果表明,与完整的 P 埋层相比,部分 P 埋层结构中的等电位轮廓更多地延伸到衬底。图 4b 显示了表面和 P 埋 / N 漂移结界面处的电场分布。对于优化的传统 LDMOS,击穿通常发生在 N 漂移/P 埋界面。对于所提出的 LDMOS,N-drift/P-sub 的结取代了 N-drift/P-buried 的结以松弛垂直电场并扩展耗尽区,从而在保持低 R 的同时获得更高的 BV d.

<图片>

一 BV 作为 ΔL 的函数 具有不同 N 的 pb 铅刀片是带有 N 的等电位轮廓轮廓 pb =1 × 10 17 厘米 −3 . b 表面和P埋/N漂移结界面的电场分布

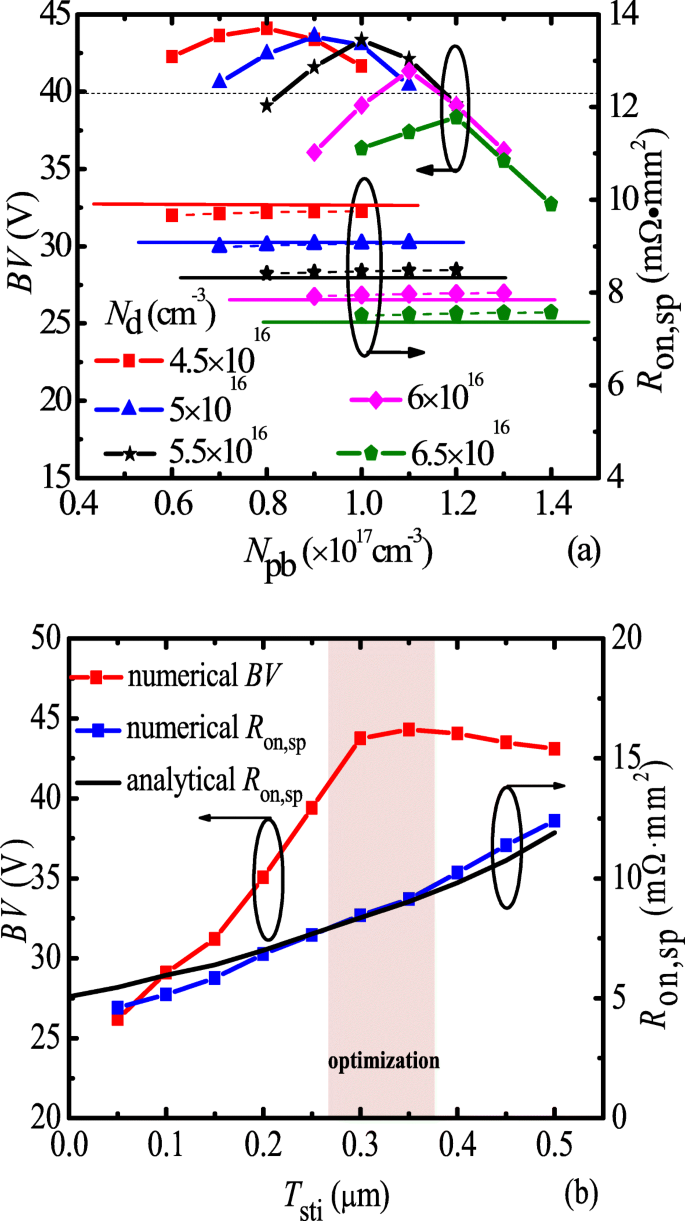

需要 N 漂移和部分 P 埋层之间的电荷平衡来实现高 BV。图 5a 显示了数值和解析 BV 和 R on,sp 作为 P 埋层 (N pb) 对于不同的 N d.对于给定的 N d、BV随着N的变化有一个最大值 pb 和 BV 的最大值 随着N的减少而增加 d.然而,R on,sp 可以增加为 N d 减少。由于 BV 要求高于 40 V,N d =5.5 × 10 16 厘米 −3 和 N pb =1 × 10 17 厘米 −3 被选中。图 5b 显示了数值和解析 BV 和 R on,sp 作为 STI 层厚度的函数 (T st)。 T sti 对 BV 和 R 有很大影响 on,sp,它应该像我们以前的工作一样仔细设计和优化[21]。对于 T sti <0.3 μm,多场板边缘下方的击穿点具有较高的电场峰值。作为 T sti 增加,电场峰值松弛,然后 BV 增加。对于 T sti =0.3 μm,得到43 V的BV。对于 T sti ≥ 0.3 μm,多场板边缘下的电场峰值足够低,击穿点转移到漏侧下方的P/N结。作为 T sti 增加,BV 增加然后饱和。

<图片>

一 数值(虚线)和解析(实线)BV 和 R on,sp 作为 N 的函数 不同 N 的 pb d. b 数值(虚线)和解析(实线)BV 和 R on,sp 作为 T 的函数 斯蒂

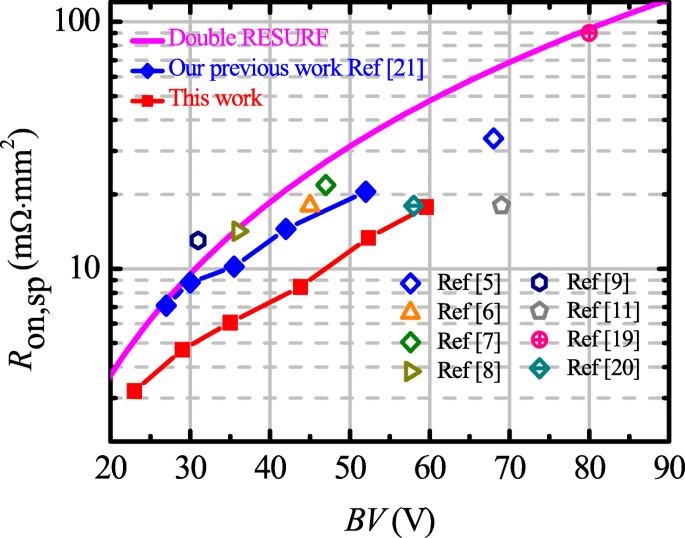

图 6 显示了现有双极-CMOS-DMOS (BCD) 技术和提议的 LDMOS 的基准。显然,所提出的 LDMOS 的工艺技术与我们开发的 BCD 技术兼容,实现了 LDMOS 的同类最佳性能。在所提出的 LDMOS 的制造过程中,N 埋层可以与 P 阱共享相同的掩模。对于提议的 LDMOS,R on,sp 为 8.5 mΩ·mm 2 而BV =43 V,与我们之前的工作相比降低了约37%。

<图片>

现有 BCD 技术的基准和提议的 LDMOS

结论

本文提出并通过数值模拟研究了一种具有增强型双栅极和部分 P 埋层的新型超低比导通电阻 LDMOS。利用高掺杂浓度的N埋层实现降低R的增强型双栅 C。在 N 漂移区下引入部分 P 埋层以增强 BV 保持电荷平衡。这项工作中 LDMOS 的制造工艺与我们之前工作中报道的现有 BCD 技术兼容。结果表明,R 与之前的工作相比,在 43 V 的 BV 下,所提出的 LDMOS 的 on,sp 降低了 37%。随着半导体加工技术向纳米级发展,R on,sp 会随着通道长度的减少而进一步降低。

缩写

- BCD:

-

双极-CMOS-DMOS

- BV:

-

击穿电压

- LDMOS:

-

横向双扩散金属氧化物半导体晶体管

- RESURF:

-

减少表面场

- R 上,sp :

-

比导通电阻

- USTI:

-

超浅沟槽隔离

纳米材料

- 用于增强药物递送的纳米纤维和细丝

- 通过等离子体增强原子层沉积原位形成 SiO2 中间层的 HfO2/Ge 叠层的界面、电学和能带对准特性

- 具有增强光催化性能的新型 Bi4Ti3O12/Ag3PO4 异质结光催化剂

- 氧化铝支撑层热稳定性增强对垂直排列单壁碳纳米管生长的影响及其在纳滤膜中的应用

- 嵌入TiO2致密层的不同尺寸和浓度的Ag纳米颗粒对钙钛矿太阳能电池转换效率的影响

- 基于紫杉醇的靶向脂质纳米颗粒的抗增殖和细胞凋亡触发潜力,通过转铁蛋白受体增强细胞内化——白血病细胞研究

- 在具有极大增强的局部电场的可见区域中由空心等离子体效应产生的全向吸收器

- 具有高开/关比和极性可切换光电导性的 SnSe2 场效应晶体管

- 通过原子层沉积制造的用于具有增强电容的超级电容器电极的 TiO2 纳米膜

- 具有部分表面改性的 ZnO 多孔纳米片,可在太阳辐射下增强电荷分离和高光催化活性

- 通过原子层沉积氧化铝和两步后退火提高 Si 钝化和 PERC 太阳能电池效率

- 关于具有 2DEG 通道和新型 GaN 纳米柱垂直场效应晶体管 (FET) 的 Baliga 品质因数 (BFOM) 增强带图案的基材