如何让处理器值得信赖

现代集成电路 (IC) 提供计算和系统控制能力来处理大量数据、实时做出安全关键决策并保护敏感数据。从头开始设计专用集成电路 (ASIC) 或现场可编程门阵列 (FPGA) 片上系统 (SoC) 将非常昂贵且耗时。许多关键功能是使用第三方知识产权 (IP) 实现的。例如,处理器内核来自专业组织,并通过其指令集架构 (ISA) 提供灵活的软件可编程功能,该架构定义了硬件和软件之间的接口。开源处理器架构为在已经面临流动威胁环境的系统中进行更深入的审查和严格的安全保证提供了机会。本文介绍了一种基于RISC-V开源ISA的IP和SoC安全保障方法。

RISC-V 由加利福尼亚大学发明,由非营利性 RISC-V 基金会管理,是第一个真正成为广泛应用的可行工业选择的开源 ISA。

RISC-V 是加州大学发明的开源 ISA,由 RISC-V 基金会管理,RISC-V 基金会是一个成立于 2015 年的非营利组织,拥有 300 多名成员。RISC-V 是第一个成为适用于广泛应用的真正可行的工业选择。工具、软件和专业知识的生态系统是强大的,并且在稳步增长。许多个人和组织已经捐赠了实施 RISC-V ISA 的开源硬件 IP。例如,OpenHW Group 的目标是使人们期待已久的开源硬件(尤其是处理器内核)的大批量芯片前景成为现实。

RISC-V 的兴起背后有很多原因。 RISC-V 从头开始构建,考虑到自定义可扩展性,允许针对特定工作负载的硬件优化达到新的水平。摩尔定律正在放缓,而定制对于维持半导体制造工艺中的技术进步无法再提供的性能改进水平至关重要。此外,RISC-V 架构免于许可成本和版税,使更多公司能够开发出创新的、价格合理的产品。例如,物联网和具有人工智能功能的可穿戴设备领域正在发生很多事情。

SoC 集成商通常使用开源或第三方 RISC-V 处理器 IP。这些设计及其相关的工具链可以通过自定义指令进行扩充。与 IP 一起提供的高质量验证环境和额外的系统级测试可以让人们确信 IP 没有严重错误。不幸的是,对于许多应用程序来说,这还不够,还有其他严重的风险需要考虑。

漏洞和木马

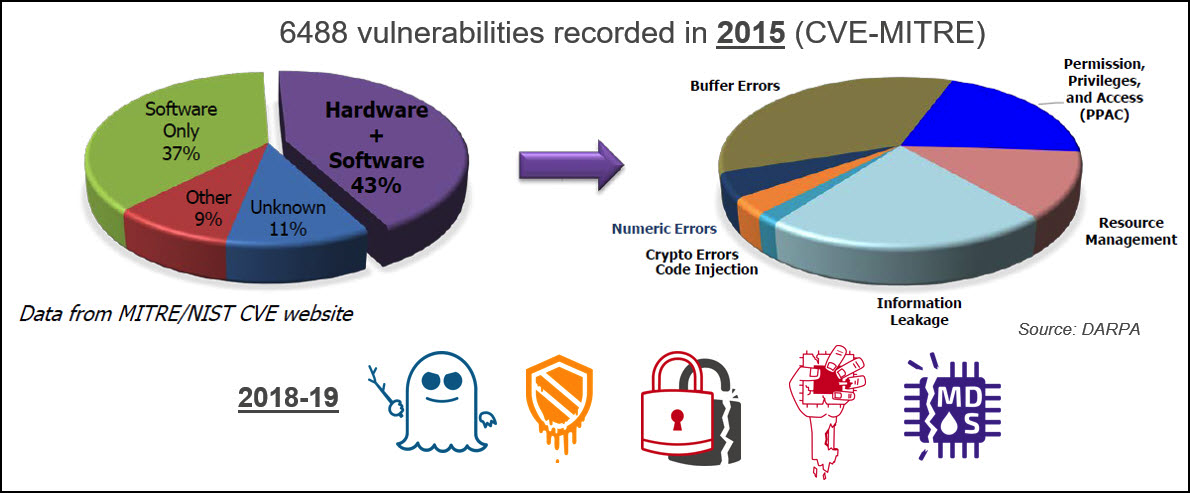

传统上,电子系统中的安全漏洞与系统级和软件问题有关。最近,硬件 IP,尤其是处理器,也成为一个核心问题(见图 1)。处理器实现使用基于管道的微架构,通常包括性能和功耗优化功能。复杂性不仅会增加遗漏功能错误的风险,还会增加遗漏安全漏洞的风险。 2018 年初发现 Meltdown 和 Spectre 攻击的安全研究人员已经证明,处理器中的性能优化功能可以以意想不到的方式用于恶意目的。从那时起,在高端和低端处理器中发现了更多漏洞。侧信道和瞬时执行攻击可能会破坏安全飞地,并允许恶意应用程序泄漏机密数据甚至接管系统的控制权。与软件不同的是,硬件问题无法通过无线更新轻松修复。通过软件解决硬件问题通常会导致严重的性能下降。

RISC-V 架构具有许多支持安全嵌入式系统实现的功能。例如,权限规范定义了四种权限模式(机器、主管、管理程序和用户)。正在批准过程中的自定义指令和 ISA 扩展(例如加密扩展)提供了额外的安全功能。设计人员可以实施多个安全飞地来隔离应用程序并防止敏感数据泄漏。然而,RTL 微架构特性仍然会导致安全漏洞。这些风险无法在 ISA 级别完全解决。正在探索的一种新方法是使用增强型 ISA (aISA) 来定义微架构级别的指令执行方面,例如,控制在 ISA 级别不可见的缓冲区或寄存器的状态。 RTL 功能错误仍可能危及所有这些安全功能。

RISC-V 内核中存在恶意逻辑或硬件特洛伊木马的可能性较小但严重性要高得多。硬件木马是一种故意设计为隐蔽的逻辑功能,它会在只有攻击者知道的极少数情况下激活。例如,当系统在其目标用例中运行时不会发生的特定数据和控制事件序列会触发特洛伊木马逻辑,进而提供破坏性的有效载荷、泄露秘密或严重破坏系统行为。使用开源或第三方 RISC-V 内核的 SoC 集成不能再忽视这种风险。

确保处理器做它应该做的事情很困难,但确保它不做任何不应该做的事情是一项更具挑战性的任务,但在很大程度上仍未解决。安全关键系统和数据隐私保护至关重要的系统需要高效、高质量的解决方案来解决安全漏洞和特洛伊木马的风险。

图 1:CVE-MITRE 数据库在 2015 年记录了 6488 个漏洞,其中 43% 可以归类为软件辅助硬件漏洞。 2018 年和 2019 年,研究人员发现并报告了处理器中的众多漏洞,包括 Meltdown 和 Spectre、Foreshadow、ZombieLoad 以及 RIDL 和 Fallout。 (来源:DARPA 和 OneSpin)

智能硬件保障

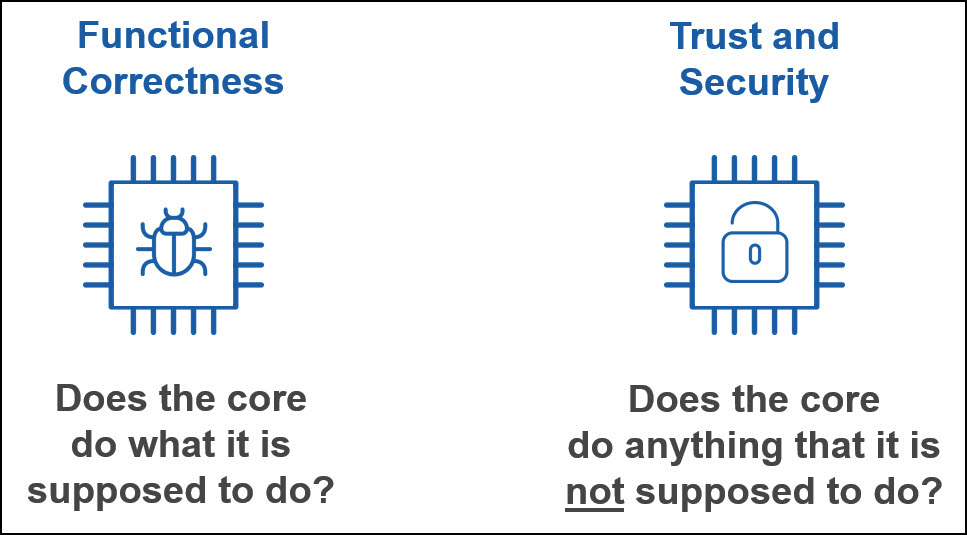

确保 RISC-V IP 的信任和安全需要创新和高效的技术解决方案,这些解决方案与功能正确性方法互补,主要针对 IP 预期用例(见图 2)。 IP 供应商负责应用最先进的信任和安全验证流程,而 IP 集成商应该有权访问独立的保证解决方案,这些解决方案可以快速部署并且无需深入了解 IP 实施细节。

正式方法可以详尽地分析硬件功能,并提供 IP 或 SoC 精确匹配 SystemVerilog 断言中经常捕获的预期行为的证据。使用商业模型检查器的硬件形式验证在过去十年中得到了广泛采用。通常,IP 供应商和 SoC 集成商在他们的队伍中有正式的验证专家,试图将遗漏功能错误的风险降至最低。虽然某些定义明确的形式验证任务可以通过应用程序自动化 ,一般来说,为了在断言中捕获 IP 的预期行为,需要大量的工程工作。此外,不能保证已经编写了足够的断言。断言集中未记录的功能或意外的差距可能导致未经验证的 IP 功能。

RISC-V 的开源特性允许开发预先打包的独立保证解决方案。例如,OneSpin 的 RISC-V 完整性验证解决方案可应用于各种微架构。它包括可扩展并可容纳自定义指令的 RISC-V ISA 和特权 ISA 模型。该解决方案的一个关键方面是它基于 OneSpin 的 GapFreeVerification™ 流程,该流程提供了严格的证据,证明对 RISC-V ISA 建模的断言集是完整的且没有漏洞。当检测硬件木马或未记录的逻辑是一个关键目标时,这方面是最重要的。该解决方案使在 RISC-V 和 RTL 实施方面具有有限专业知识的 SoC 集成商能够获得对 IP 质量和可信度的信心。 IP 开发者可以使用它在发布前检测安全弱点和功能错误。

图 2:功能正确性验证可确保处理器实现按规定运行并满足最终用户的要求。另一方面,信任和安全验证可确保处理器没有未记录的功能、不可预见的侧信道、硬件木马或其他可能被恶意行为者利用的漏洞。 (来源:OneSpin)

有用吗?

上一节中描述的 RISC-V 完整性保证过程已成功应用于多个 RTL 设计。例如,Edaptive Computing 是一家集成创新解决方案以快速优化、保证和自动化系统和流程系统,为美国国防部和商业部门客户提供服务的公司,已将该流程应用于 RocketCore。 RocketCore 是一个开源的、经过硅验证的 64 位 RISC-V 内核,带有 39 位虚拟内存系统。它有一个五阶段、单发出、有序流水线,对于长延迟指令(例如除法)可以无序完成。它包括分支预测和指令重放的高级功能。

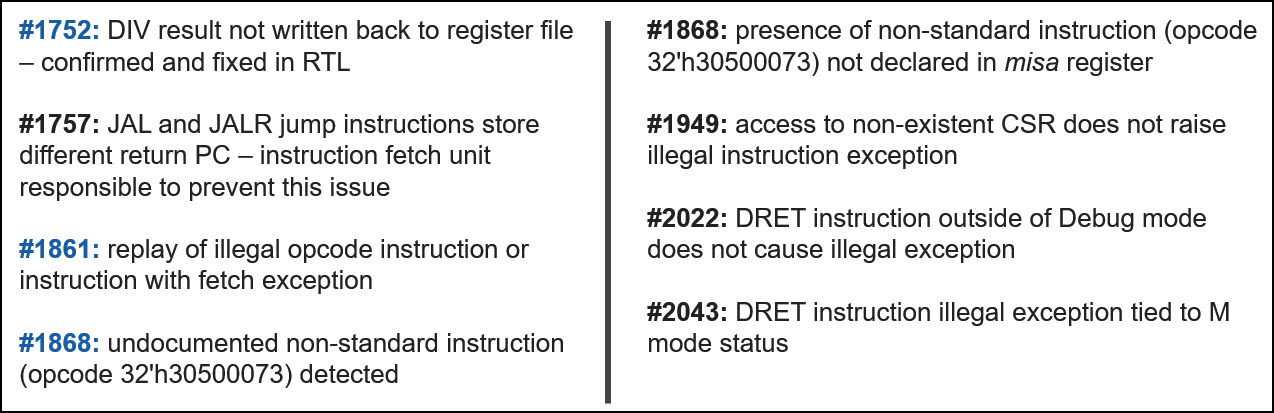

RISC-V完整性验证解决方案应用于所有指令、特权级别、中断和异常机制的设计,并检测到8个问题(见图3)。下面报告了其中 3 个的其他信息。

部门角落案例 :与除法指令的无序完成相关的深层角落错误。此问题可能导致软件程序使用除法运算计算出错误的结果并导致系统行为异常。该问题仅在极少数情况下才会出现,这就是之前的验证工作未能解决的原因。

非法指令重放 :这不是一个极端情况下的错误。重放非法指令可能会浪费处理周期,但如果仅在极少数情况下发生这种情况,则性能影响可以忽略不计。但是,还有其他方面需要考虑。指令重放可能会导致不必要的内存请求。这些请求可能会产生副作用,可以在旁道攻击中加以利用。因此,这种行为需要被消除或清楚地理解和记录。

无证说明 :检测到一个未记录的、非标准的指令,称为 CEASE,它停止了核心。实际上,RISC-V RocketCore 可以做一些它不应该做的事情。当涉及信任和安全性时,即使未记录的隐藏功能与被认为与最终应用程序无关的用例相关,也是不可接受的。

RocketCore 案例研究在 GOMACTech 2019 论文中详细介绍,该论文标题为 Complete Formal Verification of RISC-V Processor IPs for Trojan-Free Trusted ICs。 要获取副本,请访问 onespin.com/resources/white-papers。

图 3:OneSpin 的 RISC-V 完整性验证解决方案检测到并在 GitHub RocketCore 项目中报告的问题列表。 (来源:OneSpin)

下一步是什么?

本文中介绍的 RISC-V 保证过程会检测可能影响安全性的场景,并系统地揭示影响处理器行为的未记录功能和硬件木马,无论它们多么罕见和隐蔽。然而,并没有系统地检测到侧信道。对所有潜在侧信道的详尽检测需要采用适当技术的专用解决方案。已经有解决这一挑战的原型。有关更多信息,请访问 onespin.com/resources/technical-articles 并阅读 EE Times 文章嵌入式处理器的侧信道攻击。

处理器内核是嵌入式系统中的关键 IP。但是,典型的 SoC 集成了许多其他 IP,这些 IP 也可能包含硬件木马。与 RISC-V 内核不同,独立的信任保证解决方案可能并不容易获得。在这种情况下,拥有适用于任何 IP 的自动化、省力的信任评估流程将非常有价值。不包含可信 IP 模型的进程无法确保木马不存在。但是,可以识别异常和可疑的代码模式和已知的特洛伊木马签名,以及可能在后期开发阶段被利用以达到恶意目的的弱点。一篇关于此主题的论文,标题为用于硬件保障的自动硅前 IP 可信度评估 由 AEROSPACE Corporation 和 OneSpin 工程师共同撰写,将在 GOMACTech 2020 会议上发表。

嵌入式