源极和漏极触点之间只有 2 纳米距离的高性能矩形栅极 U 沟道 FET

摘要

本文提出了一种新型高性能矩形栅极 U 沟道 FET (RGUC FET),用于实现源极和漏极触点之间的极端集成距离。 RGUC FET 表现出近乎理想的亚阈值特性,直到源极/漏极 (S/D) 触点之间的距离减小到 2 nm。与其他凹陷或U形沟道型场效应晶体管不同,栅极接触不需要形成在凹陷区域内,只需在U沟道两侧的两个垂直部分之间设置一层隔离物即可。其结构优势使其可以应用于制造具有更高集成度的集成电路,以实现源极和漏极触点之间的极端集成距离。通过研究设计参数的影响,包括 S/D 触点之间的水平距离、S/D 区的延伸高度以及栅氧化层的厚度和材料,仔细研究了 RGUC FET 的电性能。 RGUC FET 的电气特性通过量子模拟得到验证。与其他非规划通道多栅极场效应管相比,新型 RGUC 场效应管适用于更高的集成度。

介绍

作为纳米级集成电路 (IC) 中最有前途的器件之一,无结场效应晶体管 (JL FET) 与传统的基于结的金属氧化物半导体 (MOS) FET 相比具有显着的电气特性,此外其制造简单,近年来得到了深入研究 [1,2,3,4]。增加栅极电压在沟道中形成累积区,导致更大的导通电流[5],多栅极(MG)FET的引入加强了栅极电压对源漏电流的可控性,导致设备的更好的亚阈值特性。多年来,无结多栅极 (JL MG) FET 也得到了广泛的研究 [6,7,8]。尽管垂直沟道环栅 MOSFET 显示出近乎理想的 I -V 由于半径只有几纳米的性能,它的垂直沟道使得源极和漏极接触不能在同一层中制造,这使得IC的布局与planner技术不兼容。此外,由于半导体制造已被迫将沟道长度缩小到小于 10 nm,MG FET 再次面临短沟道效应 [9,10,11]。为了克服短沟道效应,凹陷沟道MOSFET成为近年来的热门话题[12,13,14,15,16]。凹槽沟道MOSFET的建模和仿真工作也全面展开[17,18,19,20]。凹陷沟道 MOSFET 具有位于源极和漏极触点下方的平面垂直沟道部分和水平平面沟道部分。与只有水平平面沟道的传统 MOSFET 相比,它实际上延长了有效沟道长度。对于源漏接触距离相同的器件,与传统的平面沟道MOSFET相比,可以更不受短沟道效应的影响;然而,实验数据表明,具有凹槽沟道的 MOSFET 的亚阈值摆幅无法实现亚 100 nm 有效沟道长度的理想亚阈值摆幅。那是因为尽管沟道长度延长了,但栅极可控性并没有像 MG FET 那样得到加强。需要注意的是,最好定义一个新的与积分描述相关的关键几何参数,而不是通道长度。源漏接触距离更现实有效,因为纳米级器件设计的最终目标是在有限的给定芯片面积内实现最佳性能,而实际器件尺寸与沟道宽度有关以及源极和漏极触点之间的距离。为了结合 MG FET 和凹槽沟道 MOSFET 的优点,在我们之前的工作中,我们提出了具有 U 形沟道的鞍形栅极 FET [21,22,23],这将栅极可控性提升到水平凹槽沟道的沟道部分从平面单栅型到3-D三栅型。之后,我们升级了不仅在水平通道部分而且在两个垂直通道部分形成的 3-D 三栅极特征。该器件被命名为 H 栅极 U 沟道 FET,凹槽沟道也相应升级为 3-D U 形管沟道 [24]。如上所述,纳米级器件设计的最终目标是通过优化在有限的给定芯片面积内实现最佳性能。为了实现优化的高性能器件,需要很好地考虑和设计栅极结构和相应的沟道结构。还应该很好地考虑制造复杂性。上述器件如凹槽沟道器件、先前提出的鞍形场效应管和HGUC FET具有共同点,在小的凹陷区域内应形成良好的栅极氧化物/栅极/栅极氧化物的夹层结构。这一结构特点限制了其进一步推进整合。似乎促进集成的一个好方法是简化凹陷区域的结构特征,同时保持对 U 形沟道的垂直沟道部分和水平沟道部分的栅极控制能力。为了实现这些器件的特性和功能,在本文中,我们提出了一种新颖的矩形栅极 U 沟道 FET (RGUC FET),用于源极和漏极触点之间的极端集成距离。它具有U形沟道,可以在不增加源漏接触距离的情况下延长效应沟道长度。与其他U型沟道场效应晶体管相比,RGUC FET在U型沟道的凹陷区域具有更简单的内部结构;之后,可以实现更简单的凹陷区内部制作,更小源漏接触距离(更高集成度)。所提出的结构具有更好的栅极可控性和更小的反向漏电流以及更高的I ON/I 关闭比率。源极触点和漏极触点之间的距离可以缩小到小于 2 nm。通过量子模拟分析了整体电学特性。

方法

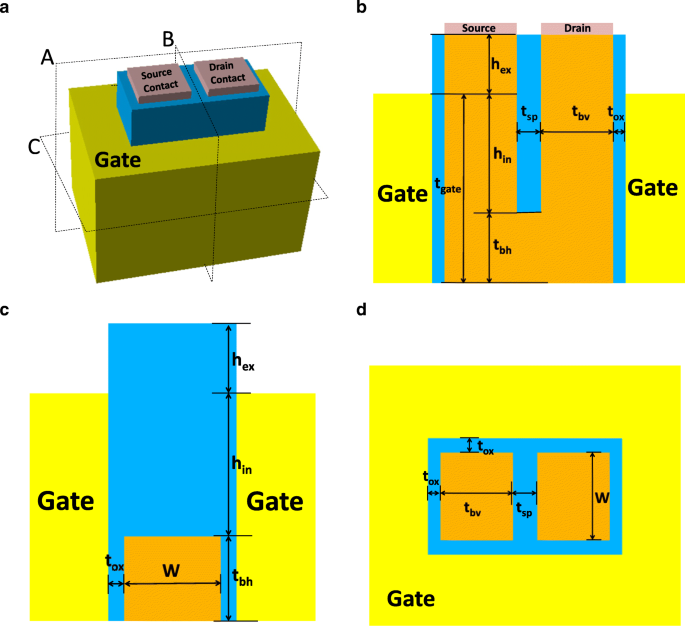

图 1a 显示了 RGUC FET 的 3D 示意图,图 1b 到 d 是通过图 1a 中所示的平面 A、B、C 和 D 切割的器件轮廓。 W 是硅的主体宽度,t b 是硅的主体厚度,h in是凹陷区域中间隔物的内部高度,h ex 是扩展源/漏区的高度,t ox 是硅体周围栅极氧化层的厚度,t sp为沉积在U型沟道凹陷区域的绝缘层的间隔厚度,等于源极接触与漏极接触之间的距离。

<图片>

一 RGUC FET 的 3D 示意图。 b 穿过a平面A的设备剖面图 . c 设备剖面图穿过 a 的 B 平面 . d 设备剖面图通过 a 的平面 C

由于硅体厚度小于6 nm,本文引入量子模拟代替经典模拟,以获得更精确的模拟结果。所有模拟均使用 SILVACO Atlas 3D 器件模拟的 TCAD,使用浓度相关迁移率模型、浓度相关 Shockley-Read-Hall 模型、俄歇复合模型、带隙变窄模型、标准带间隧道模型和玻姆量子势模型[25]。仿真参数如表1所示。两个垂直的主体部分实际上是一个有四个边的立方体,其顶面覆盖有源区或漏区,底面均与水平体部分相连。垂直体部的外侧三边被栅氧化层和矩形栅接触包围,另一内侧连接到凹陷区域中的内部间隔物。水平体的四个边都被栅氧化层和矩形栅接触包围。可以推测,由于上述结构特点,矩形栅极对水平体和垂直两个部分都具有很强的场效应控制能力。并且,内部隔离物实际上延长了硅中源极和漏极触点之间最短路径的距离,这可以消除具有平面沟道特征的多栅器件无法避免的短沟道效应。与其他3-D沟道器件[21,22,23,24]相比,该结构不需要在凹陷区形成栅极,大大降低了凹陷区内部结构的复杂性。

结果和讨论

玻姆量子势 (BQP) 模型使用从量子力学的玻姆解释导出的辅助方程计算位置相关的势能项。该模型源自纯物理学,允许该模型近似不同类别设备以及一系列材料的量子行为。量子限制对器件性能的影响,包括I -V 特征,然后将被计算为一个很好的近似值。以往的研究表明,当氧化层厚度大于0.5 nm时,栅极漏电流可以忽略不计[7, 26]。

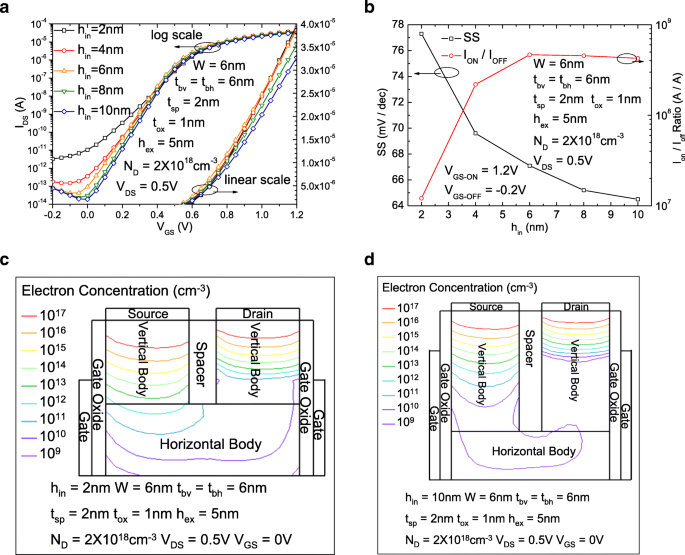

图 2a 显示了漏源电流栅源电压 (I DS-V GS) 具有不同 h 的 RGUC FET 特性 在对数和线性尺度上输入。图 2b 显示了亚阈值摆动 (SS) 和 I 的比较 ON/I 具有不同 h 的 RGUC FET 的关断比 插入随着h的增加 在,整个沟道从源极到漏极的垂直路径不断增加,然后最短有效沟道长度逐渐增加,短沟道效应逐渐减弱并最终消除。对于 h,SS 可以实现接近理想的 65 mV/dec 值 在达到 10 nm。 我 ON/I 对于 h,OFF 比率也增加了约 35 倍 由于 SS 不断降低,in 从 2 增加到 10 nm。延长的 h in 使源极到漏极的最短路径距离从 6 增加到 22 nm,等于 2 h 在 + t sp 和等效于所提出结构的有效通道长度。图 2c 和 d 显示了具有 2 nm 和 10 nm h 的器件在关闭状态下硅体中的二维电子浓度分布 在,分别。对于2 nm的情况,水平体区的最高电子浓度约为10 12 厘米 −3 并且源漏接触与水平体区之间的距离很短。此后,源漏偏压严重影响水平体区的电子分布;解决方案是延长垂直沟道,使源极/漏极远离水平体区。对于 10 nm 的情况,在图 2d 中,我们可以看到水平体区的最高电子浓度下降到 10 9 厘米 −3 ,它为关态提供了一个更理想的完全耗尽区,从而带来更低的漏电流水平。

<图片>

一 I 的比较 DS-V 具有不同h的RGUC FET的GS特性 在对数和线性尺度上输入。 b 亚阈值摆动 (SS) 和 I 的比较 ON/I 具有不同 h 的 RGUC FET 的关断比 插入c 具有 2-nm h 的器件在关断状态下硅体中的二维电子浓度分布 在。d 具有 10 nm h 的器件在关断状态下硅体中的二维电子浓度分布 在

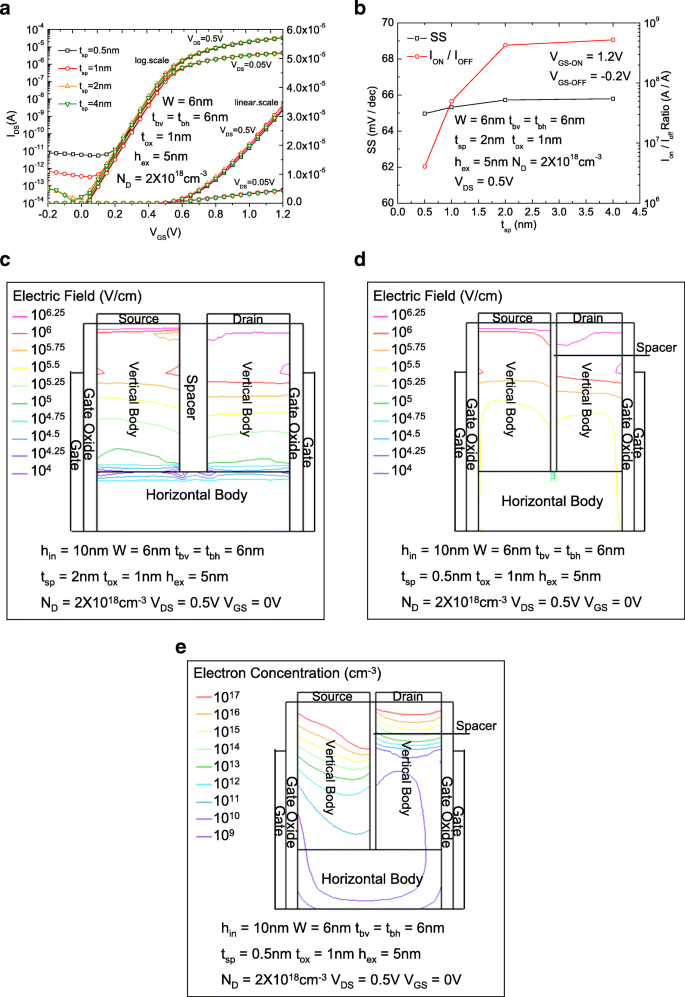

图 3a 显示了 I 的比较 DS-V 具有不同 t 的 RGUC FET 的 GS 特性 对数和线性尺度上的 sps。图 3b 显示了亚阈值摆动 (SS) 和 I 的比较 ON/I 具有不同 t 的 RGUC FET 的关断比 sps.随着t的减少 sp,源极和漏极触点之间的距离也在不断减小。漏电流主要由带间隧道电流引起。隧穿概率与能带弯曲成正比,能带弯曲可以等效于某一点的电场强度。总隧道电流为体区各点产生的隧道电流之和。

<图片>

一 I 的比较 DS-V 具有不同 t 的 RGUC FET 的 GS 特性 对数和线性尺度上的 sps。 b 亚阈值摆动 (SS) 和 I 的比较 具有不同 t 的 RGUC FET 的 ON/IOFF 比 sps. c 具有 2 nm t 的器件在关断状态下硅体中的二维电场分布 sp. d 0.5 nm t 器件在关断状态下硅体中的二维电场分布 sp. e 0.5 nm t 器件在截止状态下硅体中的二维电子浓度分布

图 3c 和图 2d 显示了具有 2 nm 和 0.5 nm t 的器件在关断状态下硅体中的二维电场分布 sp,分别。对于更大的间隔层厚度或更小的漏源电压 (V DS)偏置,凹陷区域的间隔物之间的界面上的电场强度不足以产生大量的漏电流。最强电场强度出现在栅氧化层与垂直体部分的界面附近,由V决定 广东。然而,如果源极到漏极的距离减小到小于 1 nm(小于栅极氧化层厚度),则在凹陷区中的间隔物与两个垂直主体部分之间的界面附近会出现最强的场强。可以看出,当t 对于较大的 V,sp 小于 1 nm DS(例如0.5 V),漏电流几乎与栅极偏置无关,主要由V决定 DS。 SS 几乎独立于 t sp 并且对于 h 保持接近理想的值 65 mV/dec 在 =10 nm的情况下直到t sp小于2 nm。 我 ON/I OFF比维持10 8 直到 t sp =2 nm 并且在 t 内严重退化 由于强电场引起的漏电流增加,sp 小于 2 nm 出现在凹陷区域中的间隔物和两个垂直主体部分之间的界面附近。体区硅体的电场强度在0.5 nmt全面增强 sp案例。图 3e 显示了具有 0.5 nm t 的器件在关断状态下硅体中的二维电子浓度分布 sp.与图 2d 相比,可以清楚地看到水平体区的电子浓度从 10 9 放大 到 10 10 厘米 −3 .此外,0.5 nm间隔层厚度的尺寸非常接近单分子层,这可能会在一定程度上破坏间隔层的绝缘性能。由于上述原因,t 建议sp为2 nm,用于高集成、低漏电、低功耗设计。

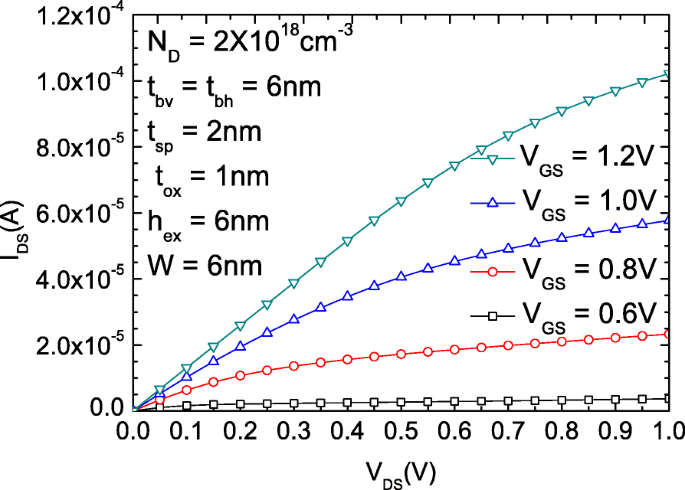

图 4 显示了 I DS-V 不同结构下优化结构的RGUC FET的DS。

<图片>

我 DS-V 器件参数优化后的 RGUC FET 的 DS 特性

V GS 值,其 SS 约为 63 mV/dec,I ON/I 关闭是 10 9 ~ 10 10 .饱和电流随着 V 而增加 GS 增加。

结论

本文提出了一种具有高集成度和高性能的新型 RGUC FET,它具有低亚阈值摆幅和更高的 I ON/I 关闭比率。源/漏(S/D)接点间距可缩小至2 nm,具有近乎理想的SS、反向漏电流、I等特性 ON/I 关闭比率。所有电气特性均采用量子模型进行模拟,以确保更精确的结果。

缩写

- BQP:

-

玻姆量子势

- FET:

-

场效应晶体管

- h 例如:

-

S/D区间间隔物的延伸高度

- h 在:

-

凹陷区间隔物内高

- I 关闭:

-

断电

- I 开 :

-

当前

- JL:

-

无连接

- MOS:

-

金属氧化物半导体

- N :

-

掺杂浓度

- RGUC:

-

矩形门U形通道

- 标准/日期:

-

源/漏

- SS:

-

亚阈值摆动

- t 哈:

-

横体厚度

- t bv :

-

立式机身厚度

- t 门:

-

浇口垂直长度

- t 牛:

-

栅氧化层厚度

- t sp:

-

S/D区之间的间隔厚度

- V DS :

-

漏源电压

- V 高:

-

栅源电压

- W:

-

体宽

纳米材料

- 结构和类的区别:用 C++ 示例解释

- while 和 do-while 之间的区别:用例子解释

- 具有高级农业化学活性的智能纳米材料和纳米复合材料

- 具有低电阻 Au 欧姆接触的多层 SnSe 纳米片场效应晶体管

- 不同纵横比的银纳米线的简便合成并用作高性能柔性透明电极

- 具有低电阻率的紫外线固化喷墨印刷银栅电极

- 通过氩等离子体处理插入 ZnO 降低金属和 n-Ge 之间的接触电阻

- 带有 V 形槽腔的通道等离子体纳米线激光器

- 在基体和填料之间具有满意界面接触水平的石墨烯辅助热界面材料

- 用碳纳米管和石墨烯改性的 FeF3·0.33H2O 高性能正极材料,用于锂离子电池

- 关于具有 2DEG 通道和新型 GaN 纳米柱垂直场效应晶体管 (FET) 的 Baliga 品质因数 (BFOM) 增强带图案的基材

- 具有由臭氧和等离子体后氧化形成的 GeOx 钝化的 Ge pMOSFET