具有低电阻 Au 欧姆接触的多层 SnSe 纳米片场效应晶体管

摘要

我们报告了 p 型单硒化锡 (SnSe) 单晶,使用改进的布里奇曼技术在 920°C 下在双层密封石英安瓿中生长。 X 射线粉末衍射 (XRD) 和能量色散 X 射线光谱 (EDX) 测量清楚地证实生长的 SnSe 由单晶 SnSe 组成。通过从块状单晶剥离制备的多层 SnSe 纳米薄片的电传输使用在 SiO2/Si 衬底上具有 Au 和 Ti 触点的背栅场效应晶体管 (FET) 结构进行,揭示了多层 SnSe由于 SnSe 纳米薄片表面上的 Sn 空位,纳米薄片表现出 p 型半导体特性。此外,在 70-90 nm 厚的 SnSe 纳米片 FET 中观察到了很强的载流子屏蔽效应。此外,还讨论了金属触点对多层 SnSe 纳米薄片基 FET 的影响,以及两种不同的金属,例如 Ti/Au 和 Au 触点。

背景

瞬态金属硫属化物提供一系列光学带隙,使这些材料适用于各种光学和光电应用 [1]。这些材料的薄膜,包括 PbTe、PbSe 和 Bi2Se3 [2],由于它们在红外光电器件、辐射探测器、太阳能电池、存储器件和全息记录器件中的预期用途而引起了相当大的关注 [3,4,5 ,6,7,8]。单锡和二硒化物(SnSe 和 SnSe2)由于其高吸收系数而成为研究的焦点,这有利于光电应用。此外,这些材料有望用于热电应用 [9,10,11,12,13,14,15,16,17,18,19,20,21,22,23,24]。单硒化锡 (SnSe) 是一种 p 型半导体,其带隙允许的间接跃迁接近 ~0.9 eV,允许的直接跃迁接近 ~1.2 eV,而二硒化锡 (SnSe2) 是 n 型半导体 [6] . SnSe的晶体结构为斜方晶系,其晶胞参数为a =11.496 Å, b =4.151 Å 和 c =4.444 Å;这种正交结构在高温下转变为四方结构,但仍低于SnSe2的熔点[25]。

最近,基于 Sn 的二元硫族化物和二硫族化物电子器件,包括具有大面积公共背栅的场效应晶体管 (FET),已被广泛研究。特别是,在表征基于 Sn 二硫属化物的 FET 方面取得了很大进展 [26, 27]。 2016 年,Pei 等人. 报道了几层 SnSe2 FET,显示出 ~10 4 的高开/关比 具有聚合物电解质的顶盖层 [27]。郭等人。还报道了一种厚度约为 8.6 nm 的高迁移率少层 SnSe2 FET [28]。从先前的工作中,已经证实薄且低载流子浓度的 SnSe 膜产生高迁移率和 SnSe2 FET 的电流开/关比。然而,尽管在利用 SnSe2 方面做出了这些努力,但尚未报道通过从单晶剥离制备的 SnSe FET 的电学特性。必须对少层和多层 SnSe2 薄片中的电传输进行详细表征,以评估锡硫属化物(例如 SnSe 纳米薄片)的电传输特性,因为预计单个 SnSe 晶体的载流子迁移率约为 7835 cm 2 /V s [29]。

在这项工作中,我们表征了使用改进的布里奇曼方法生长的单晶 SnSe。通过从块状单晶剥离制备的多层 SnSe 纳米薄片 FET 中的电传输首次使用 SiO2/Si 衬底上的背栅 FET 结构进行表征。此外,还针对两种不同类型的接触(Ti/Au 和 Au)研究了金属接触对多层 SnSe 纳米片基 FET 的影响,因为接触金属的功函数决定了空穴载流子通过肖特基势垒的传导金属-SnSe纳米薄片界面。

方法

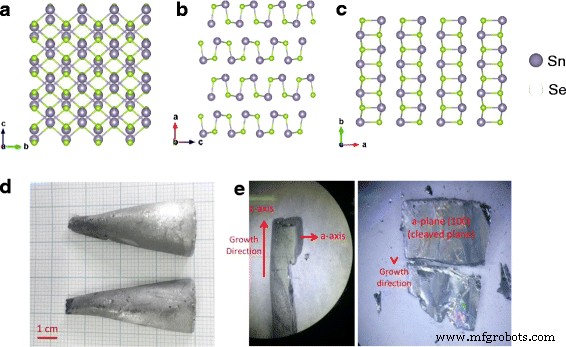

SnSe 在室温下具有层状正交晶体结构 [24]。图 1a-c 显示了沿 a 的 SnSe 晶体结构的透视图 , b , 和 c 轴向。如图 1c 所示,具有两个原子层的 SnSe 板是开槽的,而晶体中的容易解理沿(100)面发生(图 1b)。如前所述 [24, 30] 使用改进的 Bridgman 方法生长单个 SnSe 晶体。化学计量的 Sn(99.999% 喷丸,Alfa Aesar)和 Se(99.999% 粉末,Alfa Aesar)首先在双密封石英安瓿中熔化成锭(~20 g)。将原料缓慢加热至 500°C 并保温 10 小时,然后在 920°C 下再保持 10 小时,然后关闭炉子。将得到的锭磨成粉末,装入锥形石英管中,抽真空,火焰密封。这个带电的锥形石英管被放入一个更大的石英管中。外管内充入氩气以防止爆炸和氧化,然后进行火焰密封。装入的石英安瓿置于立式管式炉中温度梯度最大的位置。将立式管式炉缓慢加热至 970°C 20 小时,保持 10 小时,然后以 0.5°C/小时的速率冷却至 830°C。将炉子在 830°C 下再保持 24 小时,然后以 100°C /h 的速度冷却至 500°C,然后关闭炉子。

<图片>

一 –c 沿 a 的 SnSe 晶体的晶体结构 -, b -, 和 c - 轴向。 d 生长的单晶 SnSe 的照片。 e 沿 a 切割的 SnSe 晶体的照片 -轴 (100) 平面。 SnSe 单晶的解理面 (100) 的顶视图(右图 在 d )

结果与讨论

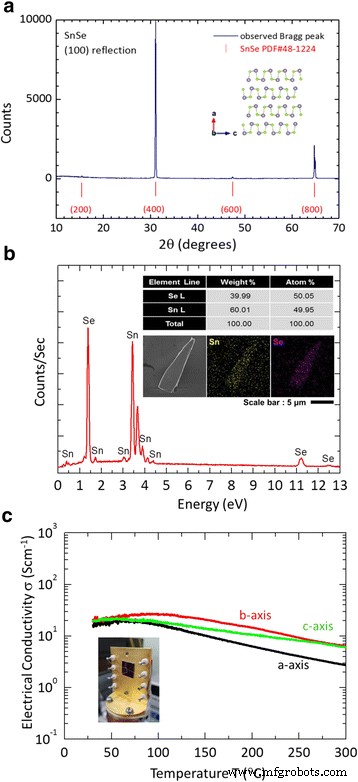

获得了锥形 SnSe 晶体(直径,30 毫米;长度,70 毫米),如图 1d-e 所示。由于在从石英安瓿中提取晶体时出现裂纹,所得晶体被分成两块(图 1d)。通过使用具有 Cu Kα 的粉末 X 射线衍射仪(XRD,New D8-Advance,Bruker-AXS,德国)检查生长的 SnSe 晶体的质量 (λ =1.5406 埃)。图 2a 显示了正交 SnSe 的功率衍射文件 (PDF) 48-1224 的 XRD 图案,以及晶体 a 的图案 轴,垂直于 SnSe 晶体的解理面 (100)。如图 2a 所示,单晶 SnSe 的 XRD 图案强烈表明具有空间群 Pnma 的单相正交晶体 [31],表明具有 (h00) 反射的强烈首选方向,这与之前的报告 [32] 非常一致。此外,主要峰是(400)和(800),在 2θ = 分别为 31.081° 和 64.818°,如图 2a [33] 所示。如图 2b 所示,能量色散 X 射线光谱 (EDX) 显示 Sn:Se 原子比为 1:1,证实了 Sn 和 Se 的化学计量比(图 2b 的插图)。图 2b 的插图还显示了器件厚度为 90 nm 的 SnSe 纳米薄片 FET 的扫描电子显微镜 (SEM) 图像和 EDX 映射。这一结果与之前的报告 [24, 33] 非常吻合。此外,使用传统的四点探针方法在 30-300 K 的温度范围内测量了单晶 SnSe(图 2b 的插图)的电导率。图 2c 显示了 SnSe 单晶沿三个不同结晶方向的温度依赖性电导率,表明由于 SnSe 中沿不同轴向的不同空穴迁移率,具有相似的温度依赖性行为和各向异性行为。如图 2c 所示,沿着 b 的电导率 - 和 c -axis 在 300 K 被确定为 ~6.00 S cm -1 , 比 a 大~2.2 倍 -轴 (~2.7 S cm −1 )。该结果与之前单晶 SnSe 的结果非常吻合 [24]。在图 2c 中,单晶 SnSe 的温度依赖性电导率显示为半导体范围 (30-100 K) 和金属范围 (>100-300 K)。超过 100 K,生长的 SnSe 晶体表现出金属传输行为,与之前的观察结果一致 [24]。

<图片>

一 SnSe 单晶的 XRD 图案,显示出清晰的 (h00) 衍射。 b SnSe单晶的EDX光谱。插图 显示了 Sn 和 Se 的原子比的详细信息。 插入 展示了器件厚度为 90 nm 的 SnSe 纳米薄片 FET 的 SEM 图像和 EDX 映射。 c SnSe 单晶的温度依赖性电导率,温度范围为 30-300 K,使用四点探针法测量

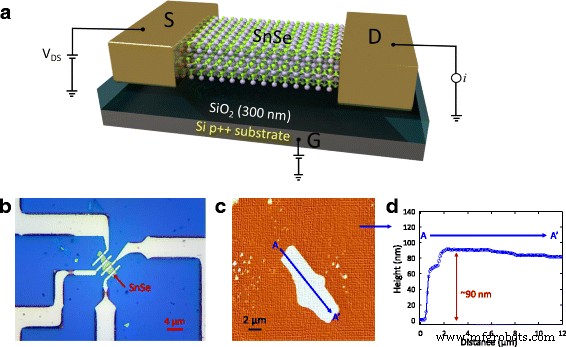

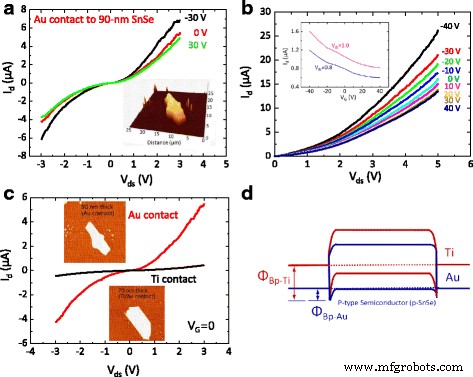

SnSe FET 器件制造如下。首先,将 SnSe 纳米薄片机械剥离到 300 nm 厚的 SiO2/p ++ 来自单个 SnSe 晶体的 Si 衬底,使用众所周知的透明胶带方法(图 1e)在(100)平面中很容易解理 [26, 27, 34]。制备的单个 SnSe 纳米薄片 FET 中的电传输测量是在室温下在背门控 FET 配置中进行的。图 3a 示意性地显示了具有大面积背栅的基于 SnSe 纳米薄片的 FET 器件。在这项研究中,在 SiO2/Si 衬底上制备了两种 SnSe 纳米薄片(70 和 90 nm 厚的 SnSe 纳米薄片)。 SnSe FET 是使用标准电子束光刻方法制造的,然后是两种类型的金属化,即 Au(厚度,100 nm)和 Ti/Au(厚度,10/100 nm)被认为是 SnSe 纳米薄片上的欧姆接触。在金属化过程之前,进行缓冲氧化物蚀刻 (BOE) 以去除纳米薄片表面上的聚合物和氧化物残留物。图 3b 显示了器件厚度为 90 nm 的 SnSe 纳米薄片 FET 的光学图像。在室温下使用原子力显微镜 (AFM) 测量 SnSe 纳米薄片的厚度(图 3c-d)。如图 3b 和图 2b 的插图所示,制造的 90 nm 厚 SnSe FET 的沟道长度为 (L ) 的 5 μm 和宽度 (W ) 为 4.71 μm,而对于 70 nm 厚的 SnSe FET L 是 5 μm 和 W 是 6 μm。所有的电流-电压 (I -V ) 特性是在室温下在电屏蔽探针台上使用半导体参数分析仪(HP 4155C,安捷伦科技公司,美国)测量的。图 4a 显示了漏极电流 (I d) 作为栅极电压的函数 (V g),对于 90 nm 厚的 SnSe 纳米薄片,对于源漏电压 (V ds) 在室温下为 -30、0 和 30 V,表明明显的 p 型半导体行为,这主要归因于 Sn 空位,如之前报道的 [15, 16, 22, 24, 35,36, 37,38,39]。图 4a 中的结果表明,具有高功函数的金属 AU 有望在 SnSe 纳米薄片上形成弱欧姆接触,表明 SnSe 纳米薄片的导带具有较低的肖特基势垒。稍后将提供关于不同金属的功函数的更详细讨论。图 4b 显示了 I d 与 V 不同 V 的 ds g,范围为 -40–40 V,步长为 10 V。从图 4b 中,空穴迁移率 (μ p) 确定为 ~2.7 cm 2 /V s,从 μ 获得 p =t 米 [L ⁄ (WC 牛 V ds)],其中 t m 是跨导 (=dI d/dV g =2.89 × 10 − 8 A /V ), L 是长度 (~5.1 μm),W 是宽度 (~4.75 μm),V ds 是 SnSe FET 的漏源电压 (~1 V),C 牛 (=ε r ε 0/d =11.5 nF/cm 2 ) 与 ε r(介电常数)为 3.9 和 d (氧化层的厚度)为 300 nm 是背栅式 SnSe 纳米片 FET 的单位面积电容。经评估的机械剥离 SnSe 纳米片 FET 的空穴迁移率远小于外延 SnSe 薄膜的空穴迁移率 (~60 cm 2 /V s) 使用富硒靶材通过脉冲激光沉积在 MgO 基材上制备 [40]。然而,这里获得的值比单晶 SnSe 纳米板获得的值大 ~1.8 倍 (~1.5 cm 2 /V s) [33]。这种相对较低的空穴迁移率可归因于 SnSe 表面的 Sn 空位 [18, 36, 41, 42] 以及 Au 金属-SnSe 纳米薄片界面处相对较高的肖特基势垒导致的强声子散射。

<图片>

一 在 SiO2/p ++ 上机械剥离的 SnSe 纳米薄片 FET 的示意图 硅衬底。 b 用于电传输测量的制造的 SnSe 纳米片 FET 的光学图像。 c SiO2/Si 衬底上的 SnSe 纳米薄片的 AFM 图像。 d SnSe 纳米薄片的 AFM 高度轮廓,用于估计和制造 FET 器件的厚度

<图片>

一 漏极电流 (I d) 作为外加源漏电压的函数 (V ds),对于栅极电压 (V g) -30、0 和 30 V,对于 90 纳米厚的 SnSe 纳米片 FET,在室温下。 b 我 d 与 V V 的 ds 对于 90 纳米厚的 SnSe 纳米片 FET,g 范围为 -40–40 V,步长为 10 V。 插图 显示 I d 与 V g 代表 V ds 为 0.8 和 1.0 V,在室温下测量。 c 我 d 与 V ds 没有偏置 V g (=0) 用于 SnSe 纳米片 FET 上的 Au 和 Ti 触点。 插图 显示了 SnSe 纳米薄片的 AFM 扫描图像。 d 两种金属Au和Ti在p型SnSe半导体上的能带图示意图

此外,我们在 I 的耗尽区观察到电导的弱栅极调谐。 d 与 V ds 曲线(图 4c)和低电流开/关比(V 时约为 2 ds 为 1 V,插图 4c) 在具有 Au 金属触点的 p-SnSe 纳米薄片 FET 中。其他具有相似厚度的二维 (2D) 半导体材料也报告了类似的行为,包括 SnS FET(厚度,~50–80 nm)[43]、~15.8 nm 厚的 SnSe 纳米片 [33]、~80 -nm 厚的 MoS2 [44] 和 ~84-nm 厚的 SnSe2 [26]。这些行为可以通过有限载流子屏蔽长度效应来解释,因为在厚度大于屏蔽长度的 FET 器件中存在表面导电表面层 \( \left(\sqrt{\varepsilon {K}_B T}{e }^2 p\right) \),其中 ε , K B 和 p 分别是半导体的介电常数、玻尔兹曼常数和空穴载流子密度,[43]。

金属触点重要地决定了 2D FET 器件的特性 [45]。为了确定金属的功函数对 SnSe 的影响,我们将 Au(功函数,~5.1 eV)和 Ti(功函数,~4.3 eV)视为 SnSe 纳米薄片上的金属触点。图 4c 显示了典型的 I d 与 V 没有门调制的 ds 曲线 (V g =0) 对于具有 Au 和 Ti 触点的 SnSe 纳米片 FET,表明与 Au (~0.56 MΩ) 相比,Ti (~15.4 MΩ) 的总电阻更高。因此,对于 Ti,金属-SnSe 界面处的肖特基势垒更高(图 4c)。在所有具有 Ti 触点的 SnSe FET 上始终观察到这种行为。如图 4d 所示,孔肖特基势垒的高度随着金属功函数的降低而增加。因此,具有大功函数的金属,例如 Pd、Au 和 Pt,可以适合作为 p-SnSe 纳米片 FET 上的欧姆接触,因为对于这些金属,用于注入空穴的肖特基势垒的高度会更低。应测量其他金属的接触电阻,以确定它们作为 SnSe 纳米薄片上的金属接触的适用性。目前正在使用传输长度方法解决此问题。

结论

总之,多层 SnSe 纳米薄片在 SiO2/Si 衬底上生长、剥离并表征具有背栅 FET 结构的 SnSe FET 通道。电传输测量表明,具有 Au 金属触点的多层 SnSe 纳米薄片表现出 p 型半导体特性,在剥离的 SnSe 纳米薄片 FET 上具有相对较低的肖特基势垒和低接触电阻。此外,我们强调这项研究是第一个报告机械剥离的基于 SnSe 纳米片的 FET 的研究,我们相信我们的 SnSe 纳米片 FET 在 2D 电气设备以及能量收集应用中非常有前途,包括未来的热电.

纳米材料