Verilog 和 HDL 语言简介

简介:

在本文中,我们将向您介绍 VHDL 和 Verilog。我们还将学习 Verilog 模块的基本结构,并熟悉 Verilog 的“连线”数据类型及其向量形式。我们还将告诉您 Verilog 和 VHDL 之间的基本区别。

什么是 Verilog?

Verilog 是一种硬件描述语言 (HDL),标准化为 IEEE 1364。它最常用于描述电子电路和系统,用于数字电路的设计和验证。

什么是 VHDL?

VHDL 也是一种用于电子设计自动化的硬件描述语言 (HDL),用于描述电子系统的行为和结构,特别适合作为描述数字电子硬件设计的结构和行为的语言以及传统的数字电路。

我需要 Verilog 和 VHDL 吗?

在我们继续之前,让我们讨论一下我们是否需要这两种语言?它们都是用于设计复杂数字电路的强大工具,但您可以自由掌握您希望使用的工具。但是,您应该对两种语言都有基本的了解。

Verilog 的演变

Verilog 于 1984 年由 Gateway Design Automation 设计。 1987 年,VHDL 成为 IEEE 标准,而 Verilog 于 1995 年进入现场。今天,这两种都是强大的 HDL(硬件描述语言)。 “Verilog”一词源自“验证”和“逻辑”这两个词。这是因为该语言首先被用作模拟和验证工具。

现在我们将讨论一些 Verilog 概念。

示例 1:

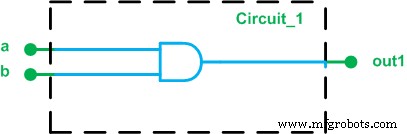

在这个例子中,让我们为如下所示的电路编写 Verilog 代码。

显示了两个输入和一个输出,端口为一位宽。该电路显示了来自两个输入的 AND 函数,从而在 out1 端口产生一个输出。 Verilog 描述可以显示为:

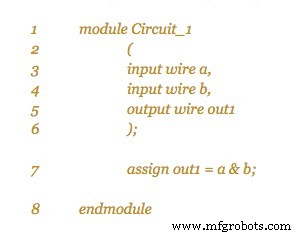

第 1 行和第 8 行:

关键字“module”和“endmodule”用于指定它们之间描述Circuit_1的行。

第 2 到 6 行:

这些行指定了“Circuit_1”与其环境的接口。关键字“输入”和“输出”显示输入和输出端口。在此之后,关键字“wire”指定了 Verilog 数据类型,它表示设计中的物理线。我们的模块中有三根线 a、b 和 out1。

第 7 行:

该行使用按位与运算符“&”描述了电路的与功能。关键字'分配;用于将 a &b 放在输出端口上。这也称为连续赋值,因为只要表达式在右侧发生变化,它总是处于活动状态,左侧会重新计算,即其输出不断更新。

将示例 1 与 VHDL 代码进行比较:

下图显示了 Circuit_1 模块的 Verilog 和 VHDL 描述。

在 VHDL 中,我们必须包含一些定义数据类型和运算符的库。因此,VHDL 代码更具描述性。然而,在某些情况下,这在高级系统的建模中是有利的。

Verilog 的四值系统:

Verilog 数据类型中使用了四个值:

- 0:低逻辑/假

- 1:高逻辑/真

- z:为高阻态(也用于描述三态缓冲器的输出)

- x:未知值

VHDL std_logic 数据类型可以采用九个不同的值,但常用的值是“0”、“1”、“Z”和“-”(“-”表示未知值)。

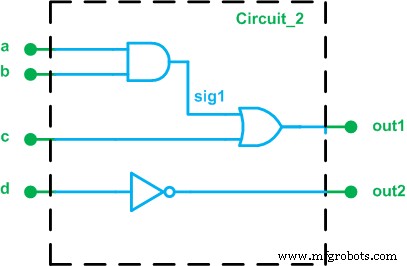

示例 2:

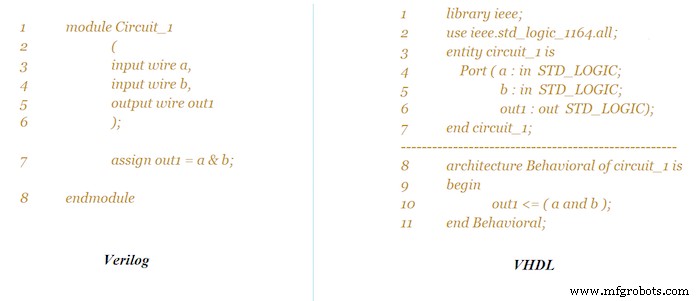

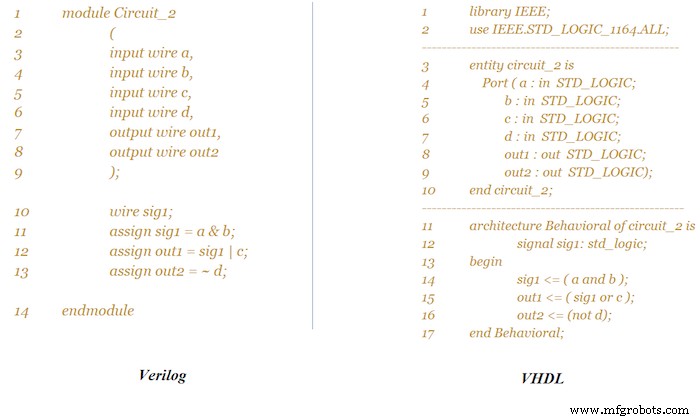

在下一个示例中,让我们为下图所示的电路 (Circuit_2) 编写 Verilog 代码。

下面的 Verilog 代码描述了所示电路:

使用的元素与我们之前的示例中的元素相似,但是在第 10 行中定义了一个内部信号。关键字“wire”指定了此连接的数据类型。按位运算符“~”用于 NOT,“|”用于 OR 操作。位运算符“^”用于异或运算。

下图将显示 Circuit_2 模块的 Verilog 和 VHDL 描述,以便您观察差异。

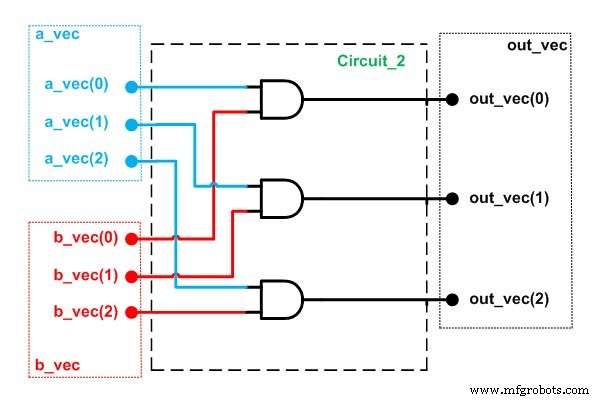

示例 3:

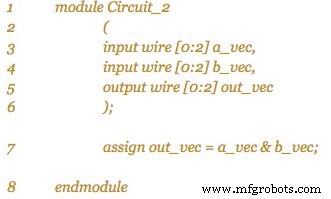

对于我们的第三个也是最后一个示例,我们将给出下图所示原理图的 Verilog 代码:  您会注意到红色和蓝色输入端口与 AND 运算符组合在一起。结果由输出端口显示。我们可以将信号分组并将它们视为一个向量,这将使我们的代码紧凑且可读。我们可以使用 Verilog 代码来描述上述电路。我们还可以轻松地扩展清单 1 中的代码来描述这个电路。

您会注意到红色和蓝色输入端口与 AND 运算符组合在一起。结果由输出端口显示。我们可以将信号分组并将它们视为一个向量,这将使我们的代码紧凑且可读。我们可以使用 Verilog 代码来描述上述电路。我们还可以轻松地扩展清单 1 中的代码来描述这个电路。

请记住,向量的索引范围可以是升序([0:2])或降序([2:0])。降序格式通常不太容易出错,可以改为使用。

工业技术