当我第一次必须创建逻辑来连接 AXI 模块时,我对 AXI 接口的特殊性有点恼火。代替常规的忙/有效、满/有效或空/有效控制信号,AXI 接口使用名为“就绪”和“有效”的两个控制信号。我的沮丧很快变成了敬畏。 AXI 接口具有内置流量控制,无需使用额外的控制信号。这些规则很容易理解,但在 FPGA 上实现 AXI 接口时必须考虑一些陷阱。本文将向您展示如何在 VHDL 中创建 AXI FIFO。 AXI 解决了延迟一个周期的问题 防止过度读取和覆盖是创建数据流接口时的常见问题。问题是当两个时钟逻辑模块进行通信时,每个模块只能以一个时钟周期延迟读取其对应模块的输出。 上图显示了顺序

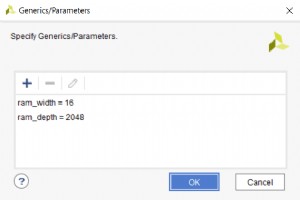

使用初始值填充块 RAM 的一种方便方法是从 ASCII 文件中读取二进制或十六进制文字。这也是在 VHDL 中创建 ROM(只读存储器)的好方法。毕竟在 FPGA 中 RAM 和 ROM 是一回事,ROM 是你只能读取的 RAM。 本文中的示例将假定以下常量和 RAM 类型已在 VHDL 文件的声明区域的开头声明。 constant ram_depth : natural := 256;constant ram_width : natural := 32;type ram_type is array (0 to ram_depth - 1) of std_logic_vector(ram

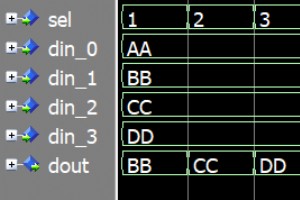

从文件中读取信号值是为被测设备 (DUT) 生成刺激的另一种方法。测试台序列和时序硬编码在 VHDL 测试台逐行读取的激励文件中。这使您可以轻松更改要馈送到测试对象的波形模式。 有时,您有一个非常具体的测试模式或事件序列,您希望您的 DUT 通过。您可以通过在 ASCII 文件中指定每个信号应具有的信号值以及它们应更改的相对仿真时间来实现此目的。 VHDL 测试平台在这种策略中的作用是从激励文件中读取数据,并在正确的时间将这些值应用于 DUT 输入。 本文是 VHDL 文件访问系列文章的第二篇。我们在上一篇博文中了解了如何从文件中读取十六进制、八进制和二进制值,如果您想了解有关使用 TEX

将图像文件转换为位图格式是使用 VHDL 读取图片的最简单方法。 Microsoft Windows 操作系统中内置了对 BMP 光栅图形图像文件格式的支持。这使得 BMP 成为一种合适的图像格式,用于存储用于 VHDL 测试平台的照片。 在本文中,您将学习如何读取像 BMP 这样的二进制图像文件并将数据存储在模拟器的动态内存中。我们将使用一个示例图像处理模块将图像转换为灰度,这将是我们的被测设备 (DUT)。最后,我们将 DUT 的输出写入一个新图像,我们可以在视觉上与原始图像进行比较。 这篇博文是关于在 VHDL 中使用 TEXTIO 库的系列文章的一部分。在此处阅读其他文章: 如何

该视频是关于 FPGA 和可编程逻辑技术的介绍性演示。我于 2019 年 11 月 19 日在泰国曼谷由 7 Peaks Software 主办的一次活动中发表了这个 45 分钟的演讲。 演讲的亮点包括: 05:07 谁在使用 FPGA? 09:06 什么是 FPGA? 12:13 如何使用静态 RAM 模拟逻辑门 17:47 通用 FPGA 原语 19:51 最便宜和最昂贵的 FPGA 20:53 FPGA 平面图 24:30 VHDL 28:05 综合和布局布线 30:50 软核 33:15 混合 FPGA/CPU (Zynq-7000) 36:44 FPGA 的优缺点 40:28

VHDL 有一个内置的伪随机生成器,但它只能生成介于 0 和 1 之间的浮点数。幸运的是,您可以从中派生出您应该需要的任何其他类型的随机数据格式。继续阅读本文以了解如何生成 real 或 integer 任何范围的值,以及随机的 std_logic_vector 序列和 time 价值观。 uniform IEEE MATH_REAL 包中的过程是本文描述的算法的基础。请注意 uniform 依靠软件生成随机数。因此,这些算法都不是可综合的。您只能在测试平台中使用它们。 procedure UNIFORM(variable SEED1, SEED2 : inout POSITIVE;

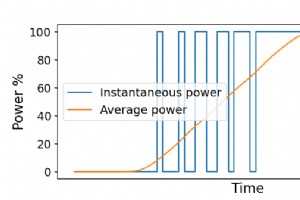

脉宽调制 (PWM) 是一种从纯数字 FPGA 引脚控制模拟电子设备的有效方法。 PWM 不是试图调节模拟电压,而是在模拟设备的全功率下快速打开和关闭电源电流。这种方法使我们能够精确控制提供给消费设备的能量的移动平均值。 适合 PWM 的用例示例包括音频调制(扬声器)、光强度控制(灯或 LED)和感应电机。后者包括伺服电机、电脑风扇、泵、电动汽车用无刷直流电机,不胜枚举。 另请参阅:使用来自 FPGA 引脚的 PWM 的 RC 伺服控制器 PWM 的工作原理 通过高频开关设备的电源,我们可以准确地控制流过它的平均电流。下图显示了 PWM 工作原理的基础知识。 PWM 输出控制一个二进制

我注意到过去几年我购买的许多小工具已经从 LED 闪烁转向 LED 呼吸。大多数电子小玩意都包含一个状态 LED,其行为会指示设备内部正在发生的事情。 我的电动牙刷在充电时会闪烁 LED,而我的手机出于各种原因使用 LED 来引起我的注意。但 LED 不再像过去那样闪烁。它更像是一种强度不断变化的模拟脉冲效果。 下面的 Gif 动画显示了我的罗技鼠标使用此效果来指示它正在为电池充电。我将这种效果称为呼吸 LED 因为光强度模式在速度和加速度上与人类呼吸周期相似。它看起来很自然,因为照明周期遵循正弦波模式。 本文是上周关于脉宽调制 (PWM) 的博客文章的延续。今天,我们将使用我们

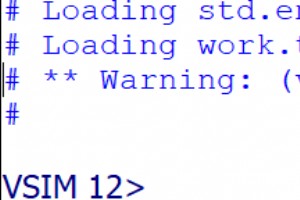

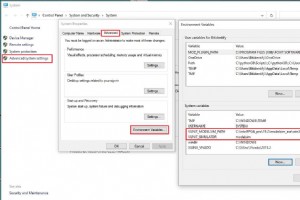

仿真完成后如何停止 VHDL 仿真器?有几种方法可以做到这一点。在本文中,我们将研究结束成功的测试台运行的最常见方法。 这里提供的 VHDL 代码是通用的,它应该可以在任何有能力的 VHDL 模拟器中工作。对于涉及Tcl的方法,我将列出ModelSim和Vivado模拟器的命令。 如果您安装了 ModelSim,您可以从本文下载一个包含四个不同测试平台的示例项目。在下面的表格中输入您的电子邮件地址以接收 Zip 文件! 使用完成 程序 VHDL 完成 procedure 是我最喜欢的停止 VHDL 测试平台的方法,该测试平台可以无错误地完成。您必须从 STD.ENV 包中导入“完

大多数 VHDL 仿真器使用工具命令语言 (Tcl) 作为其脚本语言。当您在模拟器的控制台中键入命令时,您正在使用 Tcl。此外,您可以使用 Tcl 创建在模拟器中运行并与您的 VHDL 代码交互的脚本。 在本文中,我们将创建一个使用 Tcl 而不是 VHDL 的自检测试平台来验证 VHDL 模块的行为是否正确。 另请参阅:为什么需要学习 Tcl使用 Tcl 的交互式测试台 您可以使用下面的表格下载本文和 ModelSim 项目中的代码。 DUT:VHDL 中的密码锁模块 在开始测试平台之前,我将介绍被测设备 (DUT)。它将是一个密码锁模块,当我们在密码键盘上输入正确

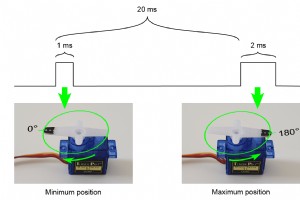

无线电控制 (RC) 模型伺服系统是微型执行器,通常用于爱好者模型飞机、汽车和船只。它们允许操作员通过无线电链路远程控制车辆。由于 RC 模型由来已久,事实上的标准接口是脉宽调制 (PWM),而不是数字方案。 幸运的是,使用 FPGA 可以施加在其输出引脚上的精确时序很容易实现 PWM。在本文中,我们将创建一个通用伺服控制器,适用于任何使用 PWM 的 RC 伺服。 RC 伺服的 PWM 控制如何工作 我已经在之前的博客文章中介绍了 PWM,但我们不能使用该模块来控制 RC 伺服。问题是 RC 伺服系统不希望 PWM 脉冲如此频繁地到达。它不关心整个占空比,只关心高周期的持续时间。

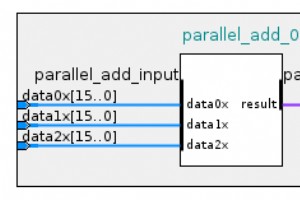

VHDL 中的 generate 语句可以自动将代码块复制到具有相同信号、进程和实例的闭包中。它是架构区域的 for 循环,可以创建链式进程或模块实例。 与只能存在于进程或子程序中的常规 for 循环不同,generate 语句直接放置在 VHDL 文件的体系结构区域中。当与泛型一起使用时,它成为设计可定制 VHDL 模块的强大工具,允许跨设计重用。 生成语句语法 generate语句的语法如下: [label :] for <constant_name> in <range> generate [declarations_local_to_each_loop

VHDL 中的文本字符串通常仅限于固定长度的字符数组。这是有道理的,因为 VHDL 描述了硬件,而通用长度的字符串需要动态内存。 要定义字符串数组,您必须在编译时为要存储的最大字符串数分配空间。更糟糕的是,您必须确定字符串的最大长度,并将每次出现的字符都填充到该字符数。下面的代码显示了这种构造的示例用法。 type arr_type is array (0 to 3) of string(1 to 10); signal arr : arr_type;begin arr(0) <= "Amsterdam "; arr(1) <= "Bang

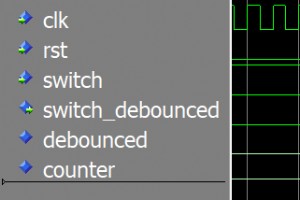

本教程介绍如何使用集成逻辑分析仪 (ILA) 和虚拟输入/输出 (VIO) 在 Xilinx Vivado IDE 中调试和监控您的 VHDL 设计的内核。 在许多情况下,设计人员需要执行片上验证。也就是说,为了验证目的,在他们的 FPGA 设计中访问内部信号的行为。 一种选择是将这些信号带到 FPGA 引脚并将它们连接到 LED 以直观地查看它们的行为。此选项简单、快速且适用于简单案例,但不灵活、可扩展或不现实。 另一种选择是拥有一个具有高级功能的外部逻辑分析仪,可以显示和描绘这些信号的行为,但它需要外部且相对昂贵的设备。 集成逻辑分析仪 (ILA) 是一种结合了先前两种选择的优点的

在为安全关键型 FPGA 应用设计 VHDL 时,尽最大努力编写测试平台是不够的。您必须出示该模块按预期工作且没有不良副作用的证据。 形式验证技术可以帮助您将需求映射到测试,证明您的 VHDL 模块符合规范。它是验证医疗保健应用或获得 DO-254 机载 FPGA 解决方案认证的工具。 为了揭开形式验证的神秘面纱,VHDLwhiz 在 Michael Finn Jørgensen 的帮助下撰写了这篇客座文章。 Michael 在该主题方面拥有丰富的经验,并在他的 GitHub 页面上分享了许多技巧。 本文可下载示例中的待测设备来自现有教程:如何使用就绪/有效握手在块 RAM 中制作

VUnit 是当今最流行的开源 VHDL 验证框架之一。它结合了 Python 测试套件运行器和专用 VHDL 库来自动化您的测试平台。 为了给您提供这个免费的 VUnit 教程,VHDLwhiz 邀请了 Ahmadmunthar Zaklouta,他是本文其余部分的幕后人员,包括您可以下载并在您的计算机上运行的简单 VUnit 示例项目。 让我们转告艾哈迈德! 本教程旨在演示 VUnit 框架在您的设计验证过程中的使用。它将指导您完成设置 VUnit、创建 VUnit 测试平台、使用 VUnit 检查库以及在 ModelSim 中运行 VUnit 测试的过程。它还演示了一些验证技

您是否曾经想通过 VUnit 验证框架运行包含 Quartus IP 内核的 VHDL 仿真? 这就是 FPGA 工程师 Konstantinos Paraskevopoulos 的想法,但他找不到合适的教程。幸运的是,他利用自己的才能弄清楚如何通过这篇客座文章与 VHDLwhiz 分享它 . 让我们转告康斯坦丁诺斯! 在使用 VUnit 仿真您的系统时,通常需要将 Quartus IP 目录中的预定义 IP 合并到您的设计中。因此,以下教程旨在为读者提供生成、合并和链接外部 Quartus IP 库到 VUnit 环境的知识。 对 VUnit 不熟悉?查看本教程:VUnit 入门

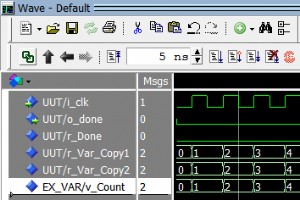

VHDL 中的变量的作用类似于 C 中的变量。它们的值在代码中修改变量的确切位置有效。因此,如果一个信号使用变量 before 的值 赋值,它将具有旧的变量值。如果信号使用变量之后的值 分配它将具有新的变量值。 变量规则: 变量只能在进程内部使用 在一个进程中创建的任何变量都不能在另一个进程中使用 变量需要在关键字process之后定义 但在关键字开始之前 使用 := 分配变量 赋值符号 立即赋值的变量采用赋值的值 要理解的最重要的事情是变量会立即获取其赋值的值。 下面的示例展示了使用变量的一种有用方法:存储数据以供临时使用 .它使用 case 语句和与 (&) 连接运算符。

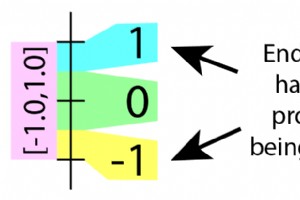

所有数字设计师都必须了解 FPGA 或 ASIC 内部的数学原理。第一步是了解有符号和无符号信号类型是如何工作的。 numeric_std 中存在有符号和无符号类型 包,它是 ieee 库的一部分。需要注意的是,还有一个包文件经常被用来进行数学运算:std_logic_arith .但是,std_logic_arith 不是官方 ieee 支持的包文件,不建议在数字设计中使用。 定义为 signed 类型的信号 意味着工具将此信号解释为正面或负面。定义为 unsigned 类型的信号 意味着信号只会是积极的。在内部,FPGA 将使用 Twos Complement 表示。例如,一个 3 位

VHDL 中的 Record 构造可用于简化您的代码。记录类似于 C 中的结构 .记录最常用于定义新的 VHDL 类型。这种新类型包含用户想要的任何一组信号。大多数情况下,这用于简化接口。这对于具有大量始终相同的信号的接口非常方便。例如,与片外存储器的接口可能很大,并且在整个设计中一遍又一遍地具有相同的信号。记录可用于缩小代码大小并减少实体中需要维护的信号。设计者只需在单个包文件中定义记录类型,然后将包文件用于任何使用该记录类型的实体。 下面的示例在包文件 (example_record_pkg.vhd) 中创建两种记录类型。这些类型在 example_record.vhd 中用于简化 F

VHDL