具有高 PSRR 的纳米级低功耗无电阻电压基准

摘要

在本文中,提出了一种具有高电源抑制比 (PSRR) 的纳瓦级无电阻亚阈值电压基准。提出了一种自偏置 MOS 分压器来为整个电压参考提供偏置电流,这是一个包含阈值电压特性的正温度系数 (TC) 电流。通过将产生的电流注入具有不同阈值电压的晶体管,实现了负TC大大降低的delta阈值电压,同时通过产生的正TC项进行温度补偿。因此,在所提出的具有低功耗和高 PSRR 的紧凑方法中实现了温度稳定的电压参考。使用 65-nm CMOS 技术的验证结果表明,在 0.00182-mm 2 的情况下,最小电源电压可低至 0.35 V 活动区。生成的参考电压为 148 mV,在 − 30 至 80 °C 的温度范围内,TC 为 28 ppm/°C。线路灵敏度为 1.8 mV/V,在 100 Hz 下没有任何滤波电容器的 PSRR 为 53 dB,功耗为 2.28-nW。

介绍

电压基准是电子系统的核心模块之一,广泛应用于医疗电子、电源管理、无线环境传感器、通信电路等。随着电子系统的电源电压随着技术的进步而不断降低,对采用纳米技术的低功耗电压基准的需求正在急剧增加[1, 2]。

传统的电压参考基于带隙参考 (BGR) 电路,它是 V 的加权和 BE 和热电压 [3, 4]。然而,由于 V 的非线性温度行为 BE,必须使用曲率补偿方法来提高 BGR 的精度 [5, 6]。 BGR 的另一个缺点是功耗。 V BE 大约为 0.7 V,而不会随着工艺改进而缩小,这绝对限制了电源电压。这些使得 BGR 不适用于低压和纳米级应用。

为了实现低功耗运行,逐渐采用仅 MOS 亚阈值电压参考 [7,8,9,10]。由于弱反型区的晶体管在电流很小的低功率应用中具有先天优势,因此可以有效降低相关电压参考的功耗。此外,由于金属氧化物半导体场效应晶体管(MOSFET)的特性与工艺改进相一致,基于MOSFET的电压基准更适合先进技术。此外,在低功率应用中也应避免使用电阻器。由于参考电压中的电流通常与电阻值成反比,因此低功耗意味着高阻值电阻[10],这会导致占用大芯片面积的大噪声。

电源抑制比 (PSRR) 是电压基准的另一个重要参数。传统的提高 PSRR 的解决方案是以芯片面积和功耗为代价的,例如额外的放大器 [11]、长沟道晶体管 [12]、共源共栅结构和额外的增益级 [13]。

为了克服上述问题,本文提出了一种基于纳米瓦 MOSFET 的无电阻亚阈值电压基准,具有高 PSRR,适用于纳米级工艺等先进技术。所提出的参考电压采用了用于 PSRR 增强的自偏置 MOSFET 分压器,它可以产生包含阈值电压特性的正温度系数 (TC) 电流。该电流用作整个电压参考的偏置电流。此外,论文中通过将偏置电流注入具有不同阈值电压的MOSFET来再现偏置电流中嵌入的阈值电压。使用所提出的方法,增量阈值电压 (∆V TH) 大大减少了负 TC。此外,还得到了一个与绝对温度成正比的加权(PTAT)项,而ΔV的加权和 TH和PTAT电压同时实现。由于两个不同阈值电压的相互TC抵消,可以大大降低温度补偿所需的PTAT电压。通过该方法,实现了结构紧凑、功耗低的仅MOSFET无电阻电压基准。

方法

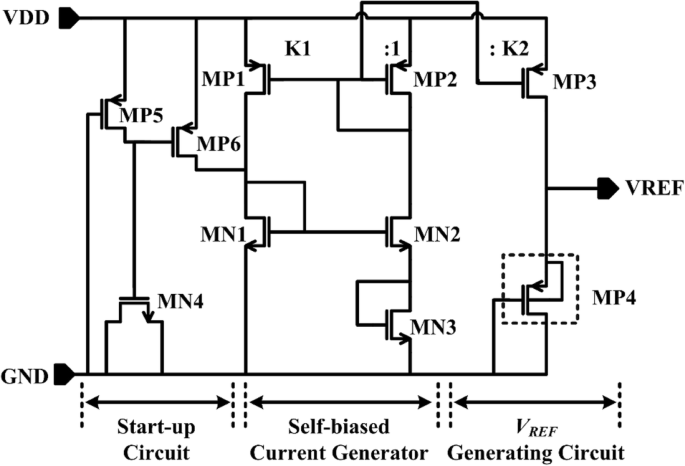

如图 1 所示,建议的参考电压由启动电路、自偏置电流发生器和 V 组成 REF产生电路。所有 n 沟道 MOSFET 都是中等阈值电压 N 型金属氧化物半导体 (mvt NMOS)。 MP4为高阈值电压晶体管P型金属氧化物半导体(hvt PMOS),其他p沟道MOSFET为中等阈值电压PMOS(mvt PMOS)。除了启动电路中的晶体管外,图1所示的所有晶体管都工作在亚阈值区域。

<图片>

建议参考电压示意图

启动电路

启动电路由 MP5、MP6 和 MN4 组成。在上电阶段开始时,MP6 的栅极电位为低电平,MP6 开启。 MP6产生的电流使MN1和MN2的栅极电位升高,整个电路开始工作。同时,MP5 为启动电容器 MN4 充电。随着MN4的充电过程,晶体管MP6逐渐关闭,这使得启动电路脱离了建议的电压参考的核心,而不会产生额外的功耗。通过这种方法,所提出的参考电压可以工作在所需的工作点,同时避免退化点。

自偏置电流发生器

图 1 中的中间部分是一个自偏置电流发生器,它基于仅 MOSFET 的分压器。这部分产生了整个电压参考的正TC偏置电流,这与NMOS的中等阈值电压有关。利用所提出的偏置电流的独特特性以方便的方式实现所提出的参考电压,这将在“方法”部分进行分析。

对于亚阈值区晶体管的电压电流特性,亚阈值区晶体管的漏极电流几乎与V无关 带有 V 的 DS DS> 4V T,其中 V T=kT/q 是热电压,k 是玻尔兹曼常数,q 是基本电荷,T 是绝对温度。因此,电流可以表示为:

$$ {I}_{\mathrm{D}}={SI}_{\mathrm{SQ}}\exp \left(\frac{V_{\mathrm{GS}}-{V}_{\mathrm{ T}\mathrm{H}}}{mV_{\mathrm{T}}}\right) $$ (1)其中S =W/L 是纵横比,m 是亚阈值斜率因子,V TH 是阈值电压,I SQ 代表特定电流,表示为:

$$ {I}_{\mathrm{SQ}}=\mu {C}_{\mathrm{OX}}\left(m-1\right){V_T}^2 $$ (2)其中 μ 是载流子迁移率和 C OX为单位面积的氧化物电容。

因此,通过由 MN1、MN2 和 MN3 组成的纯 MOSFET 分压器的电流可以表示为:

$$ {I}_{\mathrm{D}\_\mathrm{MN}1}={S}_{\mathrm{MN}1}{I}_{\mathrm{SQN}}\exp \left( \frac{V_{\mathrm{GS}\_\mathrm{MN}1}-{V}_{\mathrm{T}\mathrm{HN}}}{mV_{\mathrm{T}}}\right) $$ (3) $$ {I}_{\mathrm{D}\_\mathrm{MN}2}={S}_{\mathrm{MN}2}{I}_{\mathrm{SQN}} \exp \left(\frac{V_{\mathrm{GS}\_\mathrm{MN}2}-{V}_{\mathrm{T}\mathrm{HN}}}{mV_{\mathrm{T} }}\right) $$ (4) $$ {I}_{\mathrm{D}\_\mathrm{MN}3}={S}_{\mathrm{MN}3}{I}_{\ mathrm{SQN}}\exp \left(\frac{V_{\mathrm{GS}\_\mathrm{MN}3}-{V}_{\mathrm{T}\mathrm{HN}}}{mV_{ \mathrm{T}}}\right) $$ (5)其中我 SQN 是 NMOS 和 V 的比电流 THN为NMOS的阈值电压。

由于MN2和MN3的纵横比相同并且I D_MN2 =I D_MN3,V GS_MN2 =V GS_MN3 是有保证的。这使得 V GS_MN1 =2V GS_MN2。此外,PMOS晶体管形成电流镜并定义电流比K 1 =S MP1/S MP2 和 K 2 =S MP3/S MP2。 MN1和MN2之间的漏极电流关系可以表示为:

$$ {I}_{\mathrm{D}\_\mathrm{MN}1}={K}_1{I}_{\mathrm{D}\_\mathrm{MN}2} $$ (6)结合方程。 (3)–(6),V GS_MN2 和 I D_MN2 可以由下式给出:

$$ {V}_{\mathrm{GS}\_\mathrm{MN}2}={mV}_{\mathrm{T}}\ln \left(\frac{K_1{S}_{\mathrm{ MN}2}}{S_{\mathrm{MN}1}}\right) $$ (7) $$ {I}_{\mathrm{D}\_\mathrm{MN}2}={S}_ {\mathrm{MN}2}{I}_{\mathrm{SQN}}\exp \left(\ln \frac{K_1{S}_{\mathrm{MN}2}}{S_{\mathrm{MN }1}}-\frac{V_{\mathrm{T}\mathrm{HN}}}{mV_{\mathrm{T}}}\right) $$ (8)为便于分析,方程。 (8) 可简写为:

$$ {I}_{\mathrm{D}\_\mathrm{MN}2}={aT}^{2-{n}_1}\exp \left(b-\frac{V_{\mathrm{T }\mathrm{HN}}}{mV_{\mathrm{T}}}\right) $$ (9)其中a =S MN2μ n 0C OX(m − 1)(k/q ) 2 和 b = ln(K 1S MN2/S MN1) 与温度无关,μ n 0 是载流子迁移率的温度无关因子,n 1是载流子迁移率的绝对温度指数项,通常在1.5左右。

如方程式所示。 (9)、阈值电压V THN 与绝对温度 (CTAT) 互补,而热电压 V T 与绝对温度 (PTAT) 成正比。随着温度升高,V THN/(mV T)减小,从而增强偏置电流的正电流特性。

通过这种方法,通过MOSFET-only结构实现了正TC偏置电流,该结构承载了NMOS阈值电压的特性。

V REF产生电路

V REF产生电路如图1右半部分所示,它仅由两个晶体管MP3和MP4构成。由于亚阈值区域操作,I D_MP4 可以写成:

$$ {I}_{\mathrm{D}\_\mathrm{MP}4}={S}_{\mathrm{MN}4}{I}_{\mathrm{SQP}}\exp \left( \frac{\mid {V}_{\mathrm{GS}\_\mathrm{MP}4}\mid -\mid {V}_{\mathrm{T}\mathrm{HP}}\mid }{mV_ {\mathrm{T}}}\right) $$ (10)其中我 SQP 是 PMOS 和 V 的比电流 THP 是 V PMOS的TH。

由于我 D_MP4 =K 2我 D_MN2,NMOS阈值电压特性,V THN,可以转移到输出节点,与PMOS阈值电压的特性叠加,V THP。从方程。 (8) 和 (10), V REF 可以写成:

$$ {V}_{\mathrm{REF}}=\mid {V}_{\mathrm{T}\mathrm{HP}}\mid -{V}_{\mathrm{T}\mathrm{HN} }+{mV}_{\mathrm{T}}\ln \left(\frac{K_2{S}_{\mathrm{MN}2}{I}_{\mathrm{SQn}}}{S_{\ mathrm{MP}4}{I}_{\mathrm{SQP}}}\right)+{mV}_{\mathrm{T}}\ln \left(\frac{K_1{S}_{\mathrm{ MN}2}}{S_{\mathrm{MN}1}}\right) $$ (11)如方程的前两项所示。 (11) 实现了增量阈值电压。由于 V TH =V TH0 − βT , 其中 V TH0 是 0 K 和 β 处的阈值电压 是阈值电压的 TC,产生的增量阈值电压与绝对温度 (CTAT) 电压互补,TC 大大缩小,|βV THP|> βV 天。此外,两个额外的 PTAT 电压同时实现并显示在等式的最后两项中。 (11),用于抵消增量阈值电压降低的TC。因此,无需复杂的结构即可实现紧凑的温度稳定参考电压,稳定在|V THP0| − V THN0.

基于前面的分析,本文实现了只需要三个分支的低功率 MOSFET 电压基准。利用自偏置电流源的独特特性,采用一个二极管连接的PMOS,实现了同时具有收缩TC、PTAT电压发生器和加权求和的CTAT电压。更重要的是,所提出的结构仅由 MOSFET 构成,产生的参考电压与 delta 阈值电压成正比。因此,所提出的电压基准更适合采用纳米级技术的低功耗应用,可以进一步扩展到更先进的技术。

建议参考电压的 PSRR

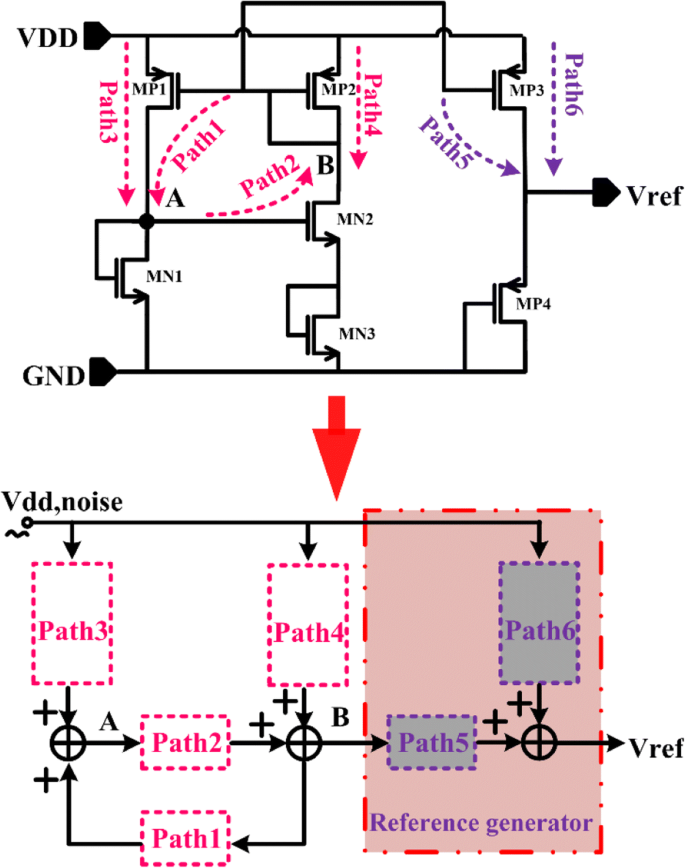

为了说明 PSRR 性能,从电源电压噪声到 V 的路径 REF及对应的等效功能图如图2所示。

<图片>

电源电压噪声的路径

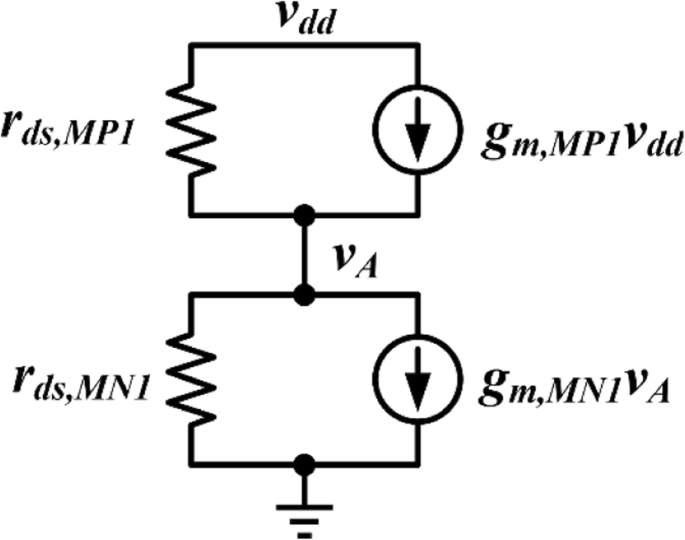

基于图2,路径3的小信号模型如图3所示,可得如下方程:

$$ \frac{v_{\mathrm{dd}}-{v}_{\mathrm{A}}}{r_{\mathrm{ds},\mathrm{MP}1}}+{g}_{\ mathrm{m},\mathrm{MP}1}{v}_{\mathrm{dd}}=\frac{v_{\mathrm{A}}}{r_{\mathrm{ds},\mathrm{MN} 1}}+{g}_{\mathrm{m},\mathrm{MN}1}{v}_{\mathrm{A}} $$ (12)

路径3小信号模型

从方程。 (12),通过路径3到达节点A的电源噪声表达式为:

$$ {Av}_{\mathrm{path}3}=\frac{v_{\mathrm{A}}}{v_{\mathrm{dd}}}=\frac{r_{\mathrm{ds},\ mathrm{MN}1}+{g}_{\mathrm{m},\mathrm{MP}1}{r}_{\mathrm{ds},\mathrm{MN}1}{r}_{\mathrm {ds},\mathrm{MP}1}}{r_{\mathrm{ds},\mathrm{MP}1}+{r}_{\mathrm{ds},\mathrm{MN}1}+{g }_{\mathrm{m},\mathrm{MN}1}{r}_{\mathrm{ds},\mathrm{MN}1}{r}_{\mathrm{ds},\mathrm{MP} 1}} $$ (13)在亚阈值区工作的晶体管的跨导为g m =I D/mV T. 因此,g 之间的关系 m、MP1 和 g m,MN1 具有相同的电流可以给定为 g m,MP1 =g 米,MN1。然后,方程。 (13)可以简化为:

$$ {Av}_{\mathrm{path}3}\approx 1 $$ (14)节点B也通过路径1对节点A产生影响,但作用与路径3相反,可以表示为:

$$ {Av}_{\mathrm{path}1}\approx -1 $$ (15)对于 V A =2V GS,MN2,路径2的增益为:

$$ {Av}_{\mathrm{path}2}=-\frac{1}{2}{g}_{\mathrm{m},\mathrm{MN}2}\left(2{r}_ {\mathrm{ds},\mathrm{MN}2}\Big\Vert \frac{1}{g_{\mathrm{m},\mathrm{MP}2}}\right)\approx -\frac{1 {2} $$ (16)v 的效果 通过路径4在节点B上的dd可以写成:

$$ {Av}_{\mathrm{path}4}=\frac{2{r}_{\mathrm{ds},\mathrm{MN}2}}{\left(1/{g}_{\ mathrm{m},\mathrm{MP}2}\right)+2{r}_{\mathrm{ds},\mathrm{MN}2}}=\frac{2{g}_{\mathrm{m },\mathrm{MP}2}{r}_{\mathrm{ds},\mathrm{MN}2}}{1+2{g}_{\mathrm{m},\mathrm{MP}2} {r}_{\mathrm{ds},\mathrm{MN}2}} $$ (17)从图 2 中的节点 A 到节点 B,可以得到两个额外的方程,它们是:

$$ {Av}_{\mathrm{path}4}{v}_{\mathrm{dd}}+{Av}_{\mathrm{path}2}{V}_{\mathrm{A}}={V}_{\mathrm{B}} $$ (18) $$ {Av}_{\mathrm{path}3}{v}_{\mathrm{dd}}+{Av}_{\mathrm{ path}1}{V}_{\mathrm{B}}={V}_{\mathrm{A}} $$ (19)根据方程(18)和(19),V处的噪声 B 可以通过以下方式给出:

$$ {V}_{\mathrm{B}}=\frac{2{g}_{\mathrm{m},\mathrm{MP}2}{r}_{\mathrm{ds},\mathrm{ MN}2}-1}{1+2{g}_{\mathrm{m},\mathrm{MP}2}{r}_{\mathrm{ds},\mathrm{MN}2}}{v }_{\mathrm{dd}}\approx {v}_{\mathrm{dd}} $$ (20)借助所提出的自偏置电流源,电流发生器部分 B 的输出节点可以跟踪电源电压的小信号变化,这有利于整个电压基准的 PSRR 改善。

使用类似的方法,路径 5 和路径 6 的电源噪声增益可以由方程表示。 (21) 和 (22) 分别为:

$$ {Av}_{\mathrm{path}5}={g}_{\mathrm{m},\mathrm{MP}3}\left({r}_{\mathrm{ds},\mathrm{ MP}3}\Big\Vert \frac{1}{g_{\mathrm{m},\mathrm{MP}4}}\right) $$ (21) $$ {Av}_{\mathrm{path} 6}\约 1 $$ (22)考虑到图 2 所示参考发生器的噪声路径连接关系,电源噪声对参考电压 V 的影响 REF,可以通过路径5和路径6确定:

$$ {v}_{\mathrm{REF}}={Av}_{\mathrm{path}5}{V}_{\mathrm{B}}+{Av}_{\mathrm{path}6} {v}_{\mathrm{dd}}=\frac{1}{1+{g}_{\mathrm{m},\mathrm{MP}4}{r}_{\mathrm{ds},\ mathrm{MP}3}}{v}_{\mathrm{dd}}=\frac{1}{1+\frac{\exp \left({V}_{\mathrm{DS},\mathrm{MP }3}/{V}_{\mathrm{T}}\right)-1}{m}}{v}_{\mathrm{dd}} $$ (23)对于 V DS> 4V T,方程中的指数项。 (23) 非常大。这使得 V 大大提高了 PSRR 性能 DS,MP3 增加。在建议的设计中,最小 V DS,MP3 超过 200 mV,这意味着电源电压的变化对 V 的影响很小 参考。因此,所提出的结构具有良好的PSRR性能。

结果与讨论

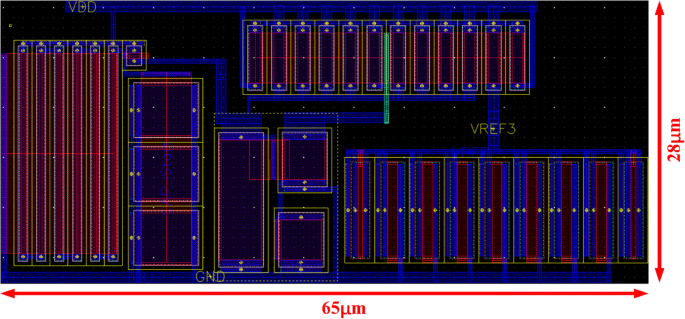

电压基准采用 65 纳米 CMOS 工艺实现,其布局如图 4 所示,占据 0.00182 毫米 2 活动区域。

<图片>

建议电路布局

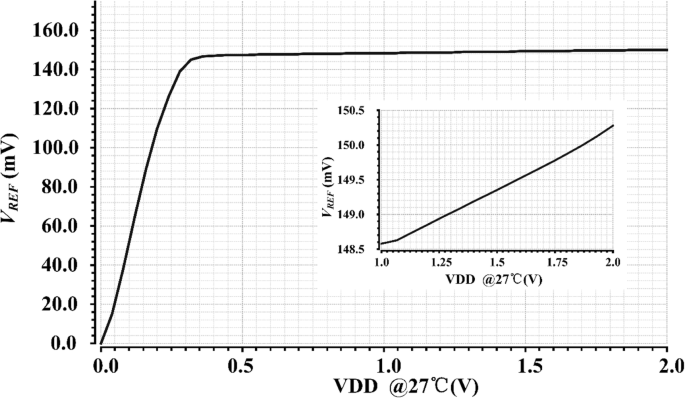

图 5 显示了建议的参考电压在 27 °C 时的线路调整率。如图 5 所示,最小电源电压可低至 350 mV,产生的参考电压 V REF,约为 148 mV。 线路灵敏度(LS)为1.8 mV/V。

<图片>

V的波形 REF 与电源电压的关系

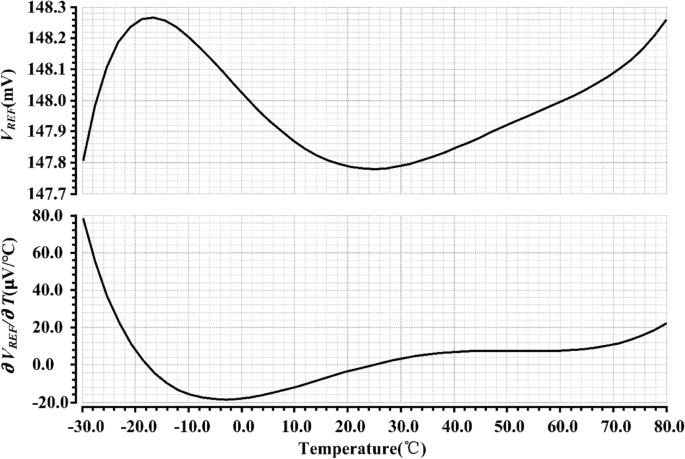

V的温度性能 REF 与 350 mV 电源电压如图 6 所示。V 的 TC 从 - 30 到 80 °C,REF 为 28 ppm/°C。 V REF在− 15 °C以下和25 °C以上呈现正温度特性,而在中温区呈现负温度特性。

<图片>

V 的温度依赖性 参考

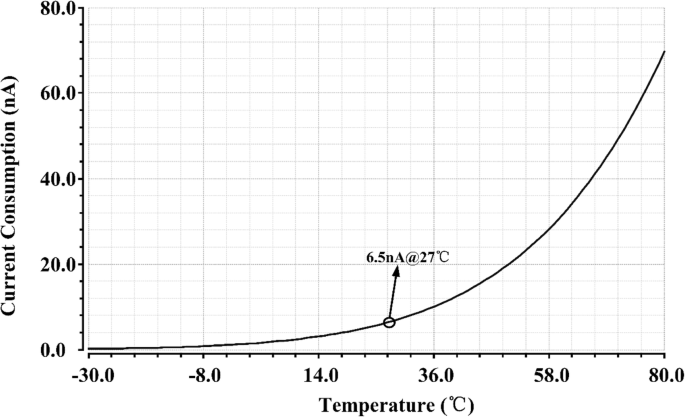

图 7 显示了在 350 mV 电源电压下电流消耗与温度的关系。电流显示正 TC。室温下的功耗约为 2.28 nW。

<图片>

电流消耗与温度的关系

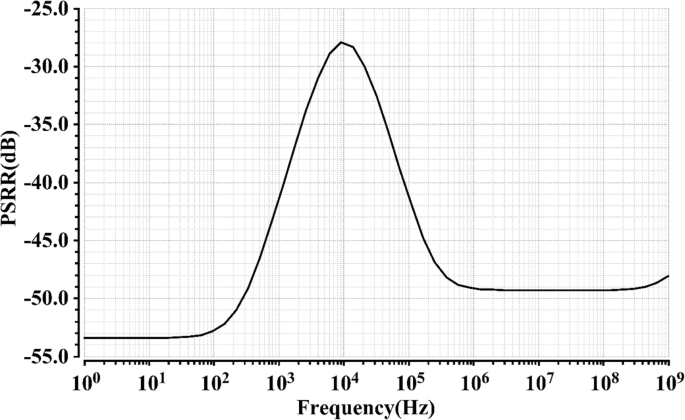

图 8 显示了在 27 °C 和 350 mV 电源电压下的 PSRR 结果,其中没有任何输出滤波电容器的 PSRR 在高达 100 Hz 时超过 53 dB。如上所述,PSRR 性能可以随着电源电压的增加而进一步提高,这意味着图 8 中所示的 PSRR 是所提出的参考电压的最差情况。

<图片>

建议参考电压的 PSRR

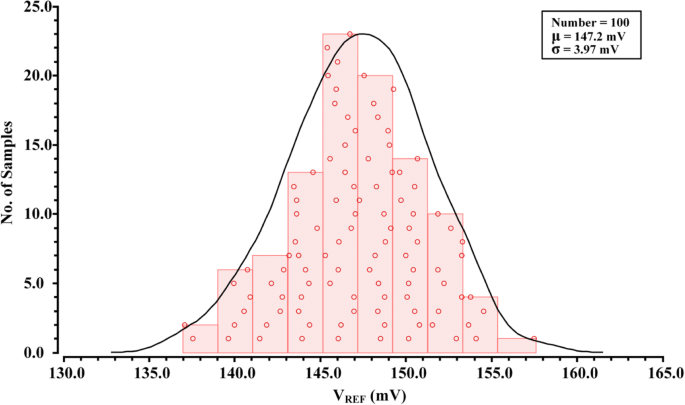

未修剪的 V 的分布 图 9 显示了 27 °C 下 100 个样品的 REF。V 的平均值和标准偏差 REF 分别为 147 mV 和 3.97 mV,导致分布 (σ/μ) 为 2.7%。

<图片>

未修剪的 V 的分布 参考

表 1 总结了建议的电压参考的特性,并将其与之前报告的一些电压参考进行了比较。

结论

本文提出了一种具有高 PSRR 的无电阻低功率电压基准,它适用于纳米级应用,并可扩展到更先进的工艺。借助基于MOSFET分压器的自偏置电流源,可以在紧凑的结构中同时实现所需的CTAT电压、PTAT电压和加权求和。更重要的是,选择delta阈值电压作为CTAT电压,大大降低了负TC。这也使得所需的 PTAT 电压值缩小。因此,可以降低电源电压和电流消耗。所有部件仅由MOSFET构建,优先用于功率敏感的高度集成应用,如SOC。

缩写

- BGR:

-

带隙参考

- CTAT:

-

与绝对温度互补

- hvt:

-

高阈值电压

- LS:

-

线灵敏度

- mvt:

-

中等阈值电压

- PSRR:

-

电源抑制比

- PTAT:

-

与绝对温度成正比

- TC:

-

温度系数

纳米材料