具有非晶 Si 钝化的高迁移率 Ge pMOSFET:表面取向的影响

摘要

我们报告了在 (001)-、(011)- 和 (111)-取向表面上制造的 Ge pMOSFET 的非晶硅钝化,用于高级 CMOS 和薄膜晶体管应用。 Ge的非晶Si钝化通过磁控溅射在室温下进行。随着 Si t 的固定厚度 Si, (001) 取向的 Ge pMOSFET 实现了更高的导通电流 I ON和有效空穴迁移率μ eff 与其他方向的设备相比。在反转电荷密度 Q inv of 3.5 × 10 12 cm −2 , Ge(001) 晶体管具有 0.9 nm t Si表现出峰值μ 278 cm 2 的效果 /V × s,是Si通用迁移率的2.97倍。随着t的减小 西,我 由于电容有效厚度的减少,Ge晶体管的ON增加,但由于midgap D的增加,亚阈值摆动和漏电底特性劣化

背景

与 Si 相比,锗 (Ge) 具有更高的空穴迁移率和更低的热预算处理,因此在高级 CMOS 和薄膜晶体管应用方面引起了巨大的研究兴趣 [1,2,3,4,5,6]。为了实现高沟道迁移率,需要在栅极堆叠形成之前进行表面钝化工艺以获得高界面质量。已经开发了多种表面钝化技术来在 Ge 金属氧化物半导体场效应晶体管 (MOSFET) [1, 2, 7,8,9,10] 中提供载流子迁移率优势。在这些技术中,Ge 上钝化的硅 (Si) 帽由于其有效抑制界面态和良好的热稳定性和可靠性等优点而成为近年来的热点[11]。使用化学气相沉积 (CVD) 和 SiH4 [1]、Si2H6 [4]、Si3H8 [12] 和电子束蒸发 [13] 的前体,已广泛研究了 Si 钝化帽的形成。尽管 CVD 方法可以在物理气相沉积 (PVD) 上提供更均匀的钝化层,但其钝化率与通道表面取向和工艺温度有很强的相关性。 PVD技术即使在室温下也能提供更高的钝化率,具有低热预算和低成本的优点,使其更适合薄膜晶体管和后端3D集成应用。在这封信中,我们利用磁控溅射的非晶硅钝化在 (001)-、(011)- 和 (111) 取向的表面上制造了高迁移率 Ge pMOSFET。显着提高有效空穴迁移率μ 与 Si 通用迁移率相比,在 Ge 晶体管中实现了 eff。非晶Si t 表面取向和厚度的影响 Si对非晶Si钝化对μ的提升作用 eff 进行了研究。

方法

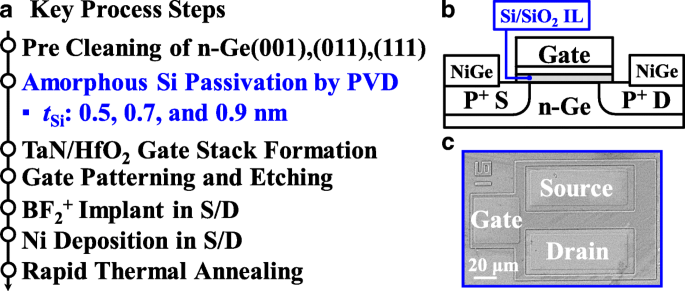

图 1a 显示了在 (001)-、(011)- 和 (111) 取向表面上制造 Ge pMOSFET 的关键工艺步骤。在稀释的 HF (1:50) 溶液中进行栅极预清洗后,通过磁控溅射在 50 W 的靶功率下在 n-Ge 衬底上沉积超薄非晶硅钝化层。三个钝化持续时间分别为 60 s、80 s 和 100 s 用于对应于 0.5、0.7 和 0.9 nm t 的沉积 si,分别。之后,分别使用 TDMAHf 和 H2O 作为 Hf 和 O 的前体,通过原子层沉积在 250 °C 下沉积 5 纳米厚的 HfO2 栅极电介质。通过反应溅射沉积 50 nm TaN 栅电极。接下来,对栅电极进行图形化和蚀刻,然后是 BF2 + 以 1 × 10 15 的剂量以 30KeV 注入源/漏 (S/D) 区 cm − 2 .通过剥离工艺形成 15 纳米镍的非自对准 S/D 金属。最后,在 400 °C 下进行快速热退火以激活掺杂剂和 S/D 金属化。图 1b 显示了具有 Si/SiO2 界面层 (IL) 的 Ge pMOSFET 的横截面示意图。图 1c 显示了制造的 Ge pMOSFET 的俯视显微镜图像。

<图片>

一 工艺顺序显示了用于制造具有不同 t 的 Ge pMOSFET 的关键步骤 西。 b 具有 SiO2 IL 的 Ge pMOSFET 的横截面示意图。 c 制备的Ge pMOSFET的俯视显微镜图像

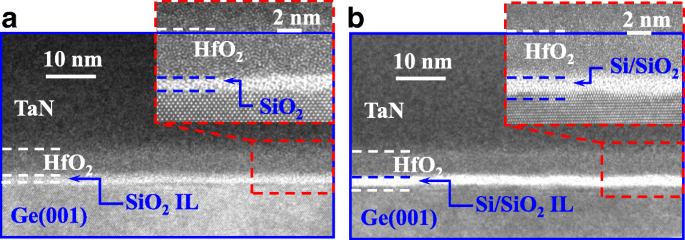

图 2a、b 显示了具有 t 的 Ge(001) 沟道上具有 SiO2/Si 界面层 (IL) 的高 κ/金属栅叠层的透射电子显微镜 (TEM) 图像 Si 分别为 0.5 和 0.9 nm。插图显示了样品的高分辨率 TEM (HRTEM) 图像。对于带有 t 的设备 0.5 nm的Si,非晶Si层被完全氧化,而0.9 nm的器件t Si,经过后续的退火步骤后,大约剩下两个 Si 单层。

<图片>

具有 a 的 Ge pMOSFET 栅极堆叠的横截面 TEM 图像 0.5 nm t Si 和 b 0.9 nm t 西。插图中的 HRTEM 图像显示 HfO2 和 Ge 通道之间形成了 Si/SiO2 IL

结果与讨论

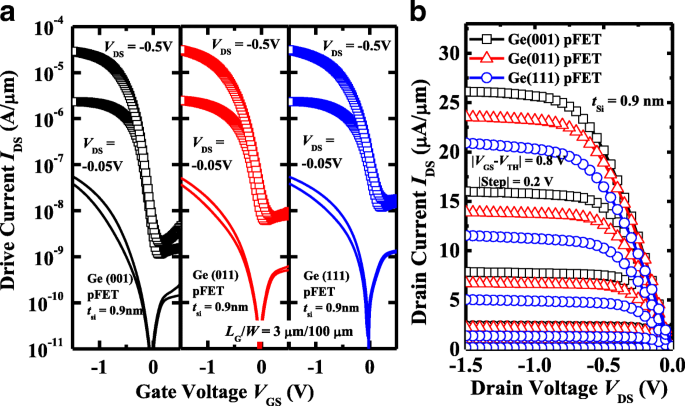

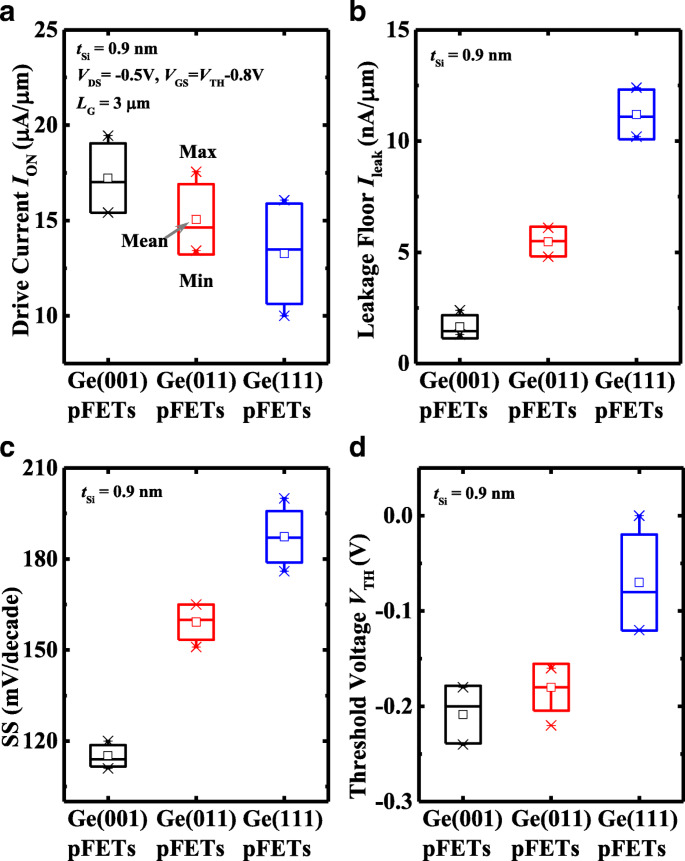

图 3a 绘制了测量的 I DS-V GS 和 I G-V 典型 Ge pMOSFET 在 (001)-、(011)- 和 (111) 取向表面上的 GS 曲线,具有 0.9 nm t Si,表现出优异的转移特性。所有晶体管的栅极长度为 L 3 μm的G和栅极宽度W 100 μm。对于所有方向,通道方向都是 [110]。 我 DS-V 在不同的栅极过驱动 V 下测量的器件的 DS 曲线 GS-V TH如图3b所示。这里,阈值电压V TH 定义为 V I 处的 GS DS 为 10 −7 A/微米。观察到 Ge(001) pMOSFET 实现了更高的驱动电流 I 与固定 V 下 (011) 和 (111) 表面上的晶体管相比,ON GS-V 泰。稍后,我们将证明这归因于 Ge(001) pMOSFET 具有更高的有效空穴迁移率 μ eff 与其他两个表面方向上的设备相比。我们对具有固定 t 的设备的电气性能进行了全面比较 0.9 nm的Si,包括I ON,漏电层I 泄漏、亚阈值摆幅 (SS) 和 V TH特性。 我 泄漏定义为最小I V 处的 DS DS of − 0.05 V. 图 4a 显示了 I 的统计图 各种方向的 Ge pMOSFET 导通,以及 I ON 被定义为 I V 处的 DS DS of − 0.5 V 和 V GS-V TH of − 0.8 V。该图中的所有晶体管都具有 L G 3 μm 和 W 100 μm。 (001) 导向装置表现出改进的均值 I ON 与 (011) 和 (111) 方向上的那些相比,这归因于更高的 μ 效果图 4b 比较了 I 器件泄漏,表明 Ge(001) 晶体管具有最低的 I 它们的泄漏,并且 Ge(011) pMOSFET 具有较低的 I 泄漏比(111)导向的设备。需要注意的是,I 泄漏由 p + 的反向电流决定 /n结在漏区,受Ge衬底中背景n型掺杂浓度和注入p + 激活的影响 掺杂剂。不同取向的晶圆中的n型掺杂浓度并不完全相同。表面取向影响 S/D 区的掺杂激活速率和再结晶质量。此外,虽然 I G 低于 I DS 在晶体管导通之前,它会影响 I 泄漏。类似地,与其他两种取向相比,(001) 取向的 Ge pMOSFET 展示了改进的 SS 特性,这是由于 (001) 表面上的晶体管具有较低的界面态中隙密度 D 它与其他设备相比。图 4d 显示了不同方向的设备具有不同的 V 泰。基于图 4 的结果,可以得出结论,在固定 t 0.9 nm的Si,(001)取向的Ge pMOSFETs获得了最好的电学特性。

<图片>

一 测量 I DS-V GS 和 I G-V 具有 0.9 nm t 的 (001)-、(011)- 和 (111) 取向的 Ge pMOSFET 的 GS 曲线 Si表现出优异的转移特性。 b 我 DS-V 在不同 V 下测得的 DS 曲线 GS-V 设备的 TH

<图片>

a 的比较 我 开,b 我 泄漏,c SS 和 d V 具有 t 的 (001)-、(011)- 和 (111) 取向的 Ge pMOSFET 的 TH 0.9 nm的Si

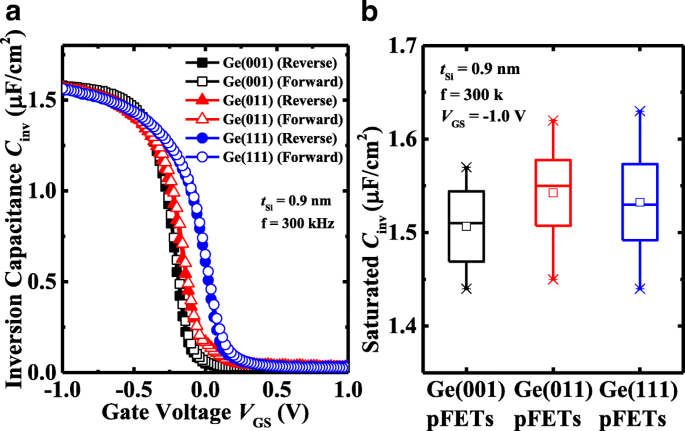

0.9 nm t晶体管中Si/SiO2 IL的厚度 利用反转电容C研究不同表面取向的Si inv 与 V GS 测量,如图 5 所示。正向和反向扫描测量显示器件中的滞后小到可以忽略不计。晶体管表现出类似的C幅度 inv, ~ 1.56 μF/cm 2 ,对应于 2.2 nm 的电容有效厚度 (CET)。图5b显示了饱和C的统计结果 inv 用于设备,这表明 C 中的差异很小 inv 在不同表面方向的晶体管中。这表明磁控溅射对非晶硅的钝化率与表面取向无关。 C的左右移动规则 inv-V GS曲线与V的曲线非常一致 图 4d 中器件的 TH,可能是由于不同取向衬底的掺杂浓度略有不同所致。

<图片>

一 反演比较C inv-V Ge pMOSFETs 之间的 GS 曲线具有 0.9 nm t Si 在不同的方向上。显示了正向和反向扫描。 b 饱和 C 的统计图 设备的 inv 显示 C 中的差异可以忽略不计 inv 在反转机制中

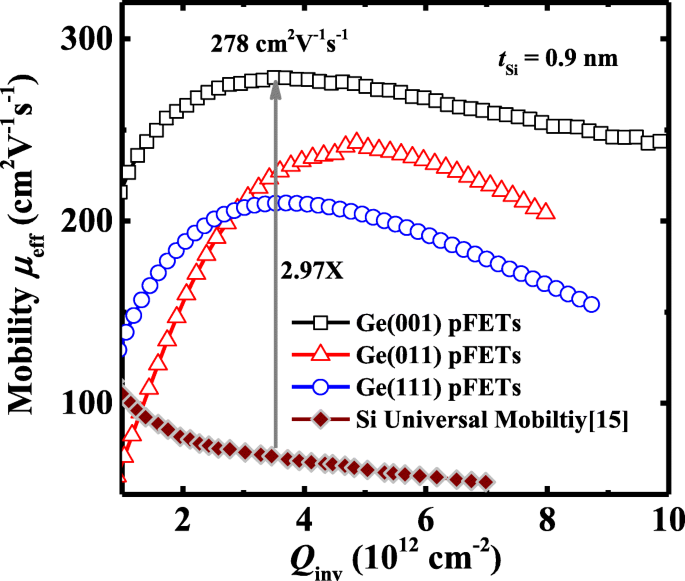

图 6 比较了 0.9 nm t 晶体管的迁移率特性 Si 在各种表面取向上。 μ eff 是使用基于总阻力斜率的方法提取的 [14]。与 (011) 和 (111) 方向上的器件相比,Ge(001) pMOSFET 表现出更高的沟道迁移率。 (001) 衬底上的晶体管达到峰值 μ 278 cm 2 的效果 /V·s 在反型电荷密度 Q ~ 3.5 × 10 12 的inv cm −2 ,比 Si 通用迁移率高 2.97 倍。 Si/Ge 界面的表面粗糙度和界面态密度 (D it) 会影响 μ 器件在高反转载流子密度下的效率。商业购买的各种表面取向的Ge晶片表面粗糙度不太可能有明显差异。因此,推测(001)取向器件的迁移率增强主要是由于界面态贡献的载流子散射减少。在这项工作中,我们评估 midgap D 它的设备,并具有固定的 t Si 为 0.9 nm,(001) 取向的 Ge pMOSFET 确实具有较低的中隙 D 与其他方向相比。

<图片>

μ 的图 eff 与 Q 具有 0.9 nm t 的 Ge pMOSFET 的 inv Si 在 (001)-、(011)- 和 (111) 取向的衬底上。 Ge(001) pMOSFET 在 μ 中实现了 2.97 倍的增强 Q 处的 eff inv of 3.5 × 10 12 cm −2 与 Si 通用迁移率相比。 μ 使用基于总阻力斜率的方法提取 eff [17]

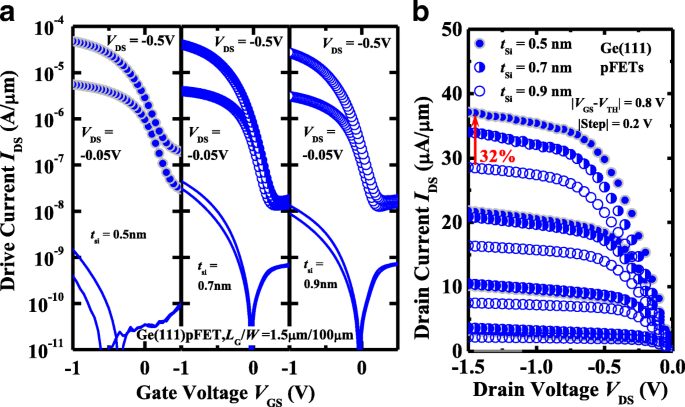

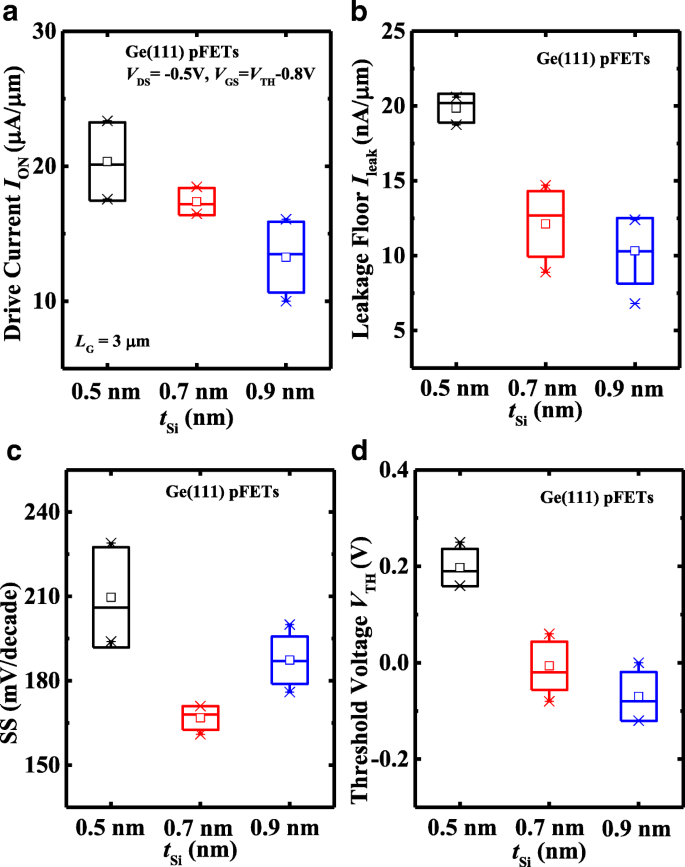

t 的影响 还研究了 Si 对 Ge pMOSFET 电性能的影响。图 7a、b 显示了测量的 I DS-V GS 和 I DS-V 分别具有 t 的 (111) 取向 Ge pMOSFET 的 DS 曲线 在 V 下,Si 为 0.5、0.7 和 0.9 nm DS 为 − 0.05 和 − 0.5 V。晶体管具有 L G 为 1.5 μm。据观察,Ge pMOSFETs 具有 0.9 nm t 与具有更薄 t 的器件相比,Si 表现出更好的传输特性 Si,但是我 器件的ON随着t的增加而减小 西。在 V DS of − 1.5 V 和 V GS-V - 0.8 V 的 TH,具有 0.5 nm t 的 Ge(111) pMOSFET Si 在 I 方面表现出 32% 的改进 与具有 0.9 nm t 的器件相比,ON 西。图 8 绘制了 I 的统计结果 开,我 泄漏、SS 和 V 具有不同 t 的 (111) 取向上的 Ge pMOSFET 的 TH 西。从图 8a 中,我们看到具有 0.5 nm t 的晶体管 Si实现改进的I 与具有较厚 t 的设备相比,ON Si,这是由于晶体管具有 0.5 nm t 具有较小 CET 的 Si,导致较高的 C 投资注意到 I 泄漏随着t的增加而减少 Si(图 8b),以及具有 0.5 nm t 的晶体管 与具有 0.7 和 0.9 纳米非晶硅钝化层的器件相比,Si 的 SS 特性较差(图 8c)。这可能是由于那些具有 0.5 nm t 的晶体管 Si具有更高的中隙D 它。 SS与midgap D的关系 Ge pMOSFET 的它可以表示为 SS =ln(10) ⋅ (kT /q) ⋅ [1 + (C it + C d )/C 牛 ],其中 C 牛,C d 和 C 它分别是氧化物电容、耗尽层电容和界面陷阱的电容。 C 它可以通过 q 计算 × D 它,是 D 它是界面陷阱密度。虽然晶体管具有 0.5 nm t Si 有较大的 C 与其他两种设备相比,ox 具有更高的 midgap D 它会导致较厚的 t 设备的劣质 SS 西。表面钝化也会影响I 从漏到源。随着V的扫荡 GS 从位置到负,通道从累积模式转换到反转模式。但是,如果 D 高,通道表面的一些点被界面陷阱钉住,可以形成泄漏路径,增加I 从漏到源。如图 8d 所示,Ge(111) pMOSFET 显示了 V 的位移 TH 到负 V GS 方向随着 t 的增加 Si,这归因于增加的 CET。此外,对于较薄的 t,下半带隙中的陷阱密度似乎增加 Si,这可能导致 V 的偏移 [2].

<图片>

一 我 DS-V GS 和 I G-V GS 和 b 我 DS-V 不同 t 的 Ge(111) pMOSFET 的 DS 曲线 西。具有 0.5 nm t 的晶体管 Si 在 I 方面表现出 32% 的改进 与具有 0.9 nm t 的器件相比,ON V 处的硅 DS of − 1.5 V 和 V GS-V - 0.8 V的TH

<图片>

a 的比较 我 开,b 我 泄漏,c SS 和 d V 具有 0.5、0.7 和 0.9 nm t 的 (111) 取向 Ge pMOSFET 的 TH Si 显示具有 0.5 nm t 的晶体管 Si有更好的我 ON,但更糟的是 SS 和 I 与具有较厚 t 的设备相比的泄漏特性 硅

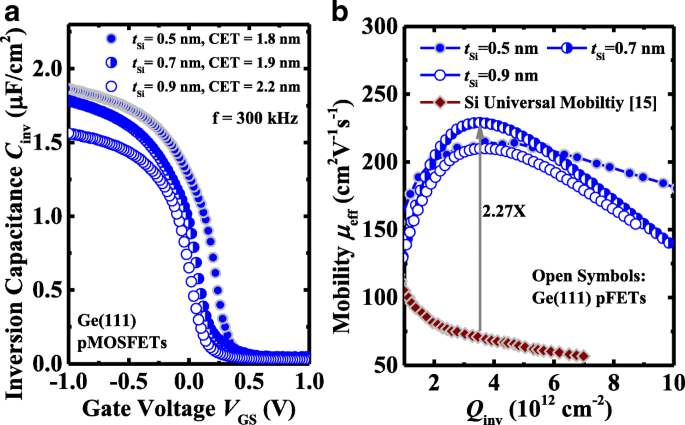

图 9a 显示了 C inv 作为 V 的函数 具有 t 的 (111) 取向表面上 Ge pMOSFET 的 GS 曲线 在 300 kHz 的频率下测量的 Si 为 0.5、0.7 和 0.9 nm。对于具有 0.5、0.7 和 0.9 nm t 的器件,反转区域的 CET 值被提取为 1.8、1.9 和 2.2 nm si,分别。 μ eff 作为 Q 的函数 设备的 inv 特性被提取出来并显示在图 9b 中。具有 0.7 nm t 的 (111) 取向 Ge pMOSFET si 达到最高峰值迁移率 229 cm 2 /V s,与 Si 通用迁移率相比高 2.27 倍。需要注意的是,具有 0.5 nm t 的器件 Si表现出显着改善的μ 具有较厚 t 的晶体管的 eff Si 处于高 Q inv(例如 10 13 cm −2 )。这也导致更高的I 在高 V 时开启 GS-V 器件中的 TH 具有 0.5 nm t Si 与具有 0.7 和 0.9 nm t 的器件相比 西。 μ 高 Q 时的 eff inv 随着 t 减少 Si从0.5 nm增加到0.7~0.9 nm,这是由于表面粗糙度越大导致载流子表面粗糙度散射越强。在室温下使用磁控溅射钝化Ge表面的过程中,表面原子的扩散被大大抑制。所以随着t的增加 Si,表面粗糙度较大,从图 2 中的 HRTEM 图像可以看出。

<图片>

一 C inv-V 对于具有 0.5、0.7 和 0.9 nm t 的 (111) 定向器件,在 300 kHz 下测量的 G 特性 西。 b μ eff 作为 Q 的函数 用于 Ge pMOSFET 的 inv [17]

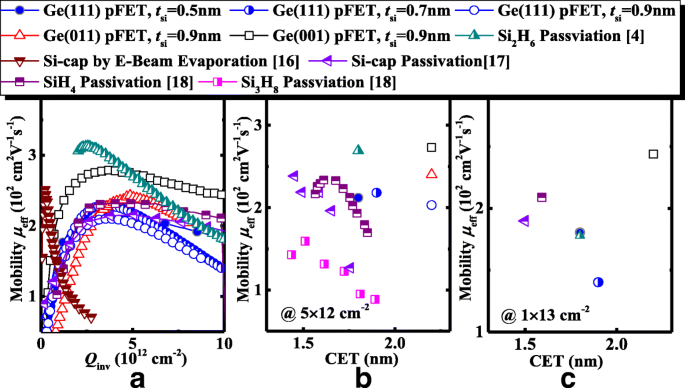

在图 10 中,我们对 μ 在这项工作中的 Ge pMOSFET 的 eff 与报道的通过电子束蒸发、SiH4、Si2H6 和 Si3H8 钝化使用 Si 的弛豫 Ge 晶体管的效果。与参考文献中通过电子束蒸发的非晶硅相比。 [15],这项工作中的 Ge pMOSFETs 表现出显着改善的 μ 效果可以看出,在类似的 CET 下,利用磁控溅射非晶 Si 钝化的 Ge pMOSFETs 具有较低的 μ eff 与采用 Si2H6 钝化的器件相比。需要进一步优化非晶Si钝化工艺以提高载流子迁移率。

<图片>

一 μ 本工作中 Ge pMOSFET 的 eff 与松弛 Ge pMOSFET 的已发布结果的比较。 b , c μ 的基准测试 在 Q 处提取的 eff inv =5 × 10 12 和 1 × 10 13 cm −2 , 分别为具有不同 CET 值的 Ge pMOSFET [18, 19]

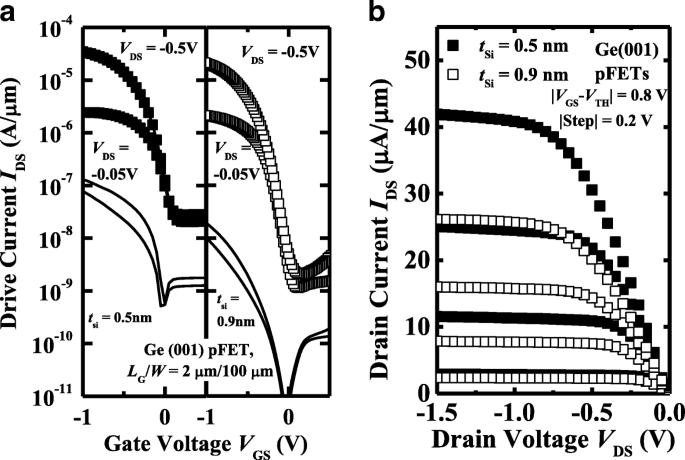

具有不同 t 的 Ge pMOSFET (001)取向表面上的Si也被表征。图 11a、b 说明了测得的 I DS-V GS 和 I DS-V 分别具有 0.5 和 0.9 nm t 的一对 Ge(001) pMOSFET 的 DS 曲线 西。与 (111) 导向器件类似,Ge(001) pMOSFET 具有 0.5 nm t Si在I上得到改进 ON 但 I 中的退化 与具有 0.9 nm t 的晶体管相比泄漏 硅。

<图片>

一 测量 I DS-V GS 和 I G-V 具有 0.5 和 0.9 nm t 的 (001) 取向 Ge pMOSFET 的 GS 曲线 西。 b 我 DS-V 器件的GS曲线

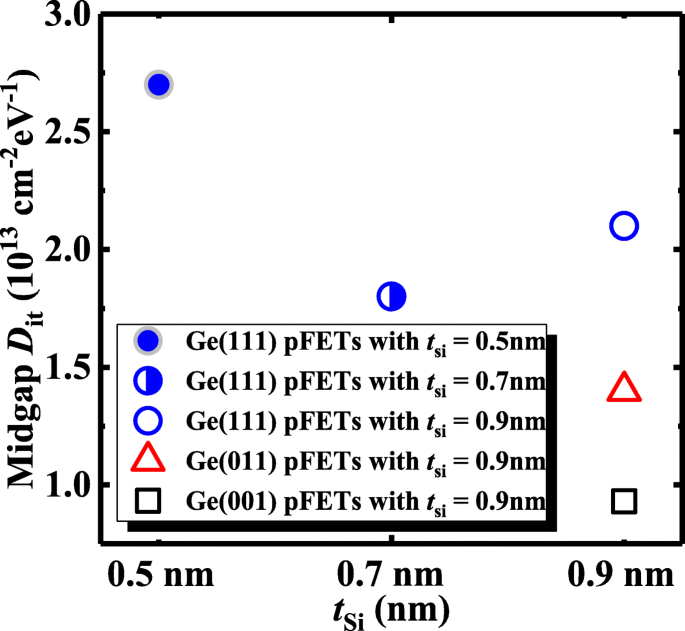

中间差距 D 用文献[16]中的方法研究了Ge pMOSFETs的特性,D的值 它由 D 计算 it =[SSlog(e)/(kT /q ) − 1]C G/q , [16] 其中 q 是电子电荷,k 是玻尔兹曼常数,T 是绝对温度,C G 是每单位面积测得的栅极电容。图 12 显示了 D 它是具有各种 Ge 表面取向的非晶硅厚度的函数。对于 (111) 取向的表面,具有 0.7-nm t 的器件 si 具有最低的 D 它的价值。随着 0.9 nm t Si,(001) 导向器件具有较低的 D 与其他方向的晶体管相比。

<图片>

D 它与不同Ge表面取向的非晶Si厚度的关系

最后,我们比较了表 1 中不同方向的 Ge pMOSFET 的关键电气特性。t 与其他两种取向相比,Si、Ge(001) pMOSFET 具有改进的电气性能。可以通过降低t来提高驱动电流 Si 从 0.9 nm 到 0.5 nm,这是由于 t 更薄 Si 提供显着降低的 CET,而不会导致 μ 的退化 效果

结论

在 (001)-、(011)- 和 (111) 取向的衬底上演示了由非晶 Si 钝化的 Ge pMOSFET。随着 t Si为0.9 nm,改善了I 与 (011) 和 (111) 取向的器件相比,在 (001) 取向的 Ge pMOSFET 中获得了导通和 SS 特性,因为 μ eff 和下中间隙 D 它。 Ge(001) pMOSFET 具有 0.9 nm t Si达到278 cm 2 的峰值迁移率 /V s 在 Q inv of 3.5 × 10 12 cm −2 ,比 Si 通用迁移率高 2.97 倍。证明 I 随着t的减小,器件的ON得到改善 Si由于CET的减少。但是具有较厚 t 的 Ge pMOSFET 由于中间间隙 D,Si 表现出优越的亚阈值摆动和漏电底限 它可以通过增加 t 来减少 硅。

缩写

- ALD:

-

原子层沉积

- BF2 + :

-

硼氟离子

- CET:

-

电容有效厚度

- 哥:

-

锗

- GeOx :

-

氧化锗

- 高频:

-

氢氟酸

- HfO2 :

-

二氧化铪

- HRTEM:

-

高分辨透射电子显微镜

- IL:

-

界面层

- MOSFET:

-

金属氧化物半导体场效应晶体管

- Ni:

-

镍

- Si:

-

硅

- SS:

-

亚阈值摆动

- TaN:

-

氮化钽

- TDMAHf:

-

四(二甲基酰胺基)铪

纳米材料

- KUHMUTE 通过 SLS 3D 打印重新设计移动性

- 使用 AFPM 进行高速 3D 打印

- 使用 AION500MK3 进行高速 3D 打印

- 基于带 AgNWs 电极的纹理表面的 PEDOT:PSS/n-Si 太阳能电池的高性能

- 基于混合全介电-石墨烯超表面的可控双折射偏振转换器

- 具有改良表面结构的高性能有机-纳米结构硅混合太阳能电池

- 具有高 PSRR 的纳米级低功耗无电阻电压基准

- 具有部分表面改性的 ZnO 多孔纳米片,可在太阳辐射下增强电荷分离和高光催化活性

- 具有由臭氧和等离子体后氧化形成的 GeOx 钝化的 Ge pMOSFET

- 关于限制具有高霍尔迁移率的非常薄的非晶态 Sn 掺杂 In2O3 薄膜中载流子传输的因素的新见解

- 具有 ZrO2 电介质的高迁移率 Ge pMOSFET:后退火的影响

- 在 SiNx 钝化层中注入氟离子的高击穿电压和低动态导通电阻 AlGaN/GaN HEMT