CMOS 栅极电路

到目前为止,我们对晶体管逻辑电路的分析仅限于 TTL 设计范式,其中使用双极晶体管,并且浮动输入等效于“高”(连接到 Vcc)输入的一般策略 - 以及相应地,“集电极开路”输出级的允许 - 得以维持。然而,这并不是我们构建逻辑门的唯一方法。

场效应晶体管

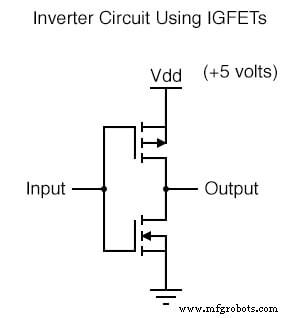

场效应晶体管,尤其是绝缘栅晶体管,可用于门电路的设计。作为电压控制而不是电流控制的器件,IGFET 倾向于允许非常简单的电路设计。以以下使用 P 和 N 沟道 IGFET 构建的逆变器电路为例:

请注意正极电源端子上的“Vdd”标签。该标签遵循与 TTL 电路中的“Vcc”相同的约定:它代表施加到场效应晶体管漏极的恒定电压,以地为基准。

栅极电路中的场效应晶体管

低输入

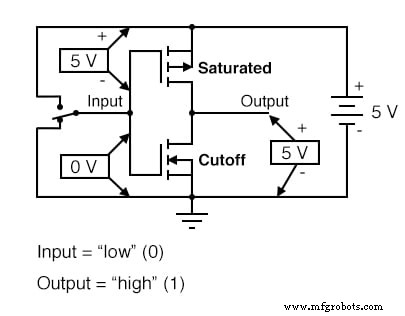

让我们将此门电路连接到电源和输入开关,并检查其操作。请注意,这些 IGFET 晶体管是 E 型(增强模式),因此常关 设备。

需要在栅极和漏极之间(实际上,在栅极和衬底之间)施加正确极性的电压来使它们导通 .

上部晶体管是 P 沟道 IGFET。当沟道(衬底)比栅极(栅极相对于衬底为负)更正时,沟道增强,源漏之间允许电流。

因此,在上图中,顶部的晶体管是导通的。栅极和衬底(源极)之间的电压为零的下部晶体管处于正常模式:off .

因此,这两个晶体管的作用是使门电路的输出端子与 Vdd 牢固连接,并具有非常高的接地电阻。这使得输入的“低”(0) 状态的输出“高”(1)。

高投入

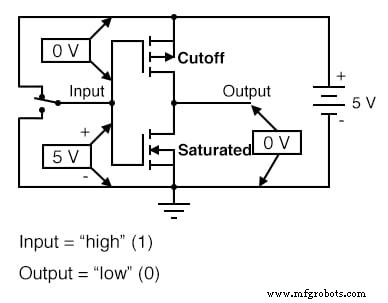

接下来,我们将把输入开关移到另一个位置,看看会发生什么:

现在较低的晶体管(N 沟道)饱和,因为它在栅极和衬底(通道)之间施加了足够的正确极性的电压以将其打开(栅极为正,通道为负)。在其栅极和衬底之间施加零电压的上部晶体管处于正常模式:off .

因此,该门电路的输出现在为“低”(0)。显然,该电路表现出反相器或非门的行为。

互补金属氧化物半导体 (CMOS)

使用场效应晶体管代替双极晶体管大大简化了反相器门的设计。请注意,该门的输出永远不会像最简单的 TTL 电路那样浮动:它具有自然的“图腾柱”配置,能够提供和吸收负载电流。

这个门电路优雅设计的关键是互补 使用 P 沟道和 N 沟道 IGFET。由于 IGFET 通常被称为 MOSFET (M etal-O xide-S 半导体 F 字段 E 效果 T 电阻器),并且该电路同时使用 P 沟道和 N 沟道晶体管,因此对这种栅极电路的一般分类是 CMOS :C 补充 M 等 O xide S 半导体。

CMOS 门:挑战和解决方案

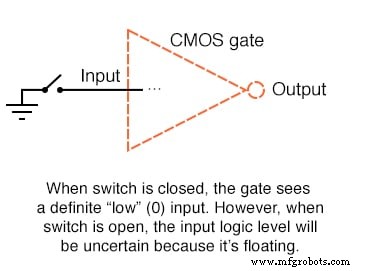

CMOS 电路不受场效应晶体管固有非线性的困扰,因为作为数字电路,它们的晶体管总是在 饱和 或截止 模式,从不处于活动 模式。然而,它们的输入对静电(静电)源产生的高电压敏感,如果悬空,它们甚至可能被寄生电压源激活为“高”(1)或“低”(0)状态。

因此,在任何情况下都不允许 CMOS 逻辑门输入浮动。请注意,这与 TTL 门的行为非常不同,TTL 门将浮动输入安全地解释为“高”(1) 逻辑电平。

浮动输入的 CMOS 问题

如果 CMOS 逻辑门的输入由单掷开关驱动,则这可能会导致问题,其中一种状态的输入牢固地连接到 Vdd 或地,而另一种状态的输入浮动(不连接任何东西):

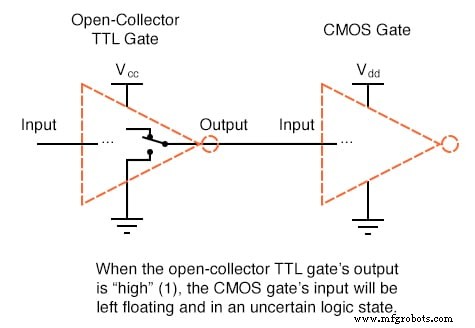

此外,如果 CMOS 栅极输入由集电极开路驱动,则会出现此问题 TTL 门。因为这样的 TTL 门的输出在变为“高”时会浮动 (1),因此 CMOS 门的输入将处于不确定状态:

浮动输入的解决方案

上拉电阻

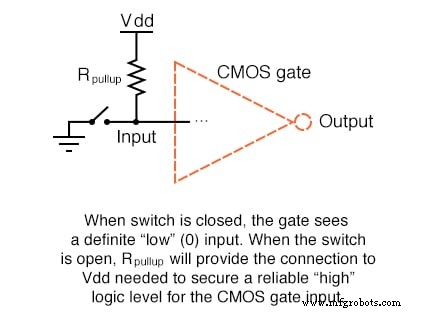

幸运的是,有一个简单的解决方案可以解决这个难题,它在 CMOS 逻辑电路中经常使用。每当一个单掷开关(或任何其他类型的门输出不能两者 源和吸收电流)用于驱动 CMOS 输入,连接到 Vdd 或地的电阻可用于为驱动设备的输出浮动状态提供稳定的逻辑电平。

该电阻器的值并不重要:通常 10 kΩ 就足够了。当用于在浮动信号源的情况下提供“高”(1) 逻辑电平时,该电阻器称为上拉电阻器 :

下拉电阻

当这种电阻用于在浮动信号源的情况下提供“低”(0) 逻辑电平时,它被称为下拉电阻 .同样,下拉电阻的值并不重要:

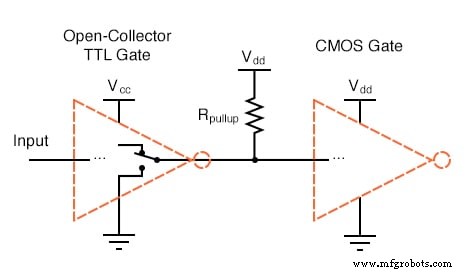

因为集电极开路的 TTL 输出总是下沉,从不拉出,电流,上拉 将此类输出连接到 CMOS 栅极输入时需要电阻器:

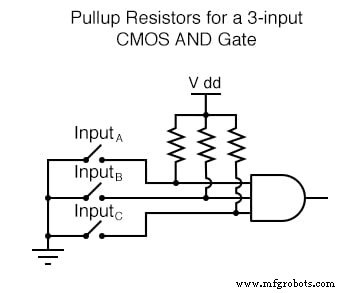

多个上拉和下拉电阻

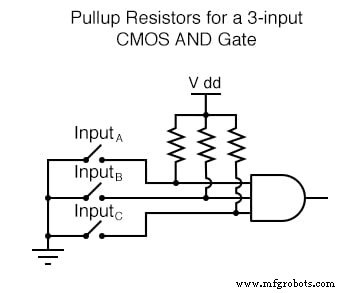

虽然前面例子中使用的 CMOS 门都是反相器(单输入),但上拉和下拉电阻的相同原理适用于多输入 CMOS 门。当然,每个门输入都需要单独的上拉或下拉电阻:

这就引出了下一个问题:我们如何设计多输入 CMOS 门,例如 AND、NAND、OR 和 NOR?毫不奇怪,这个问题的答案揭示了设计的简单性,与 TTL 等效的 CMOS 反相器非常相似。

CMOS 与非门

例如,这里是CMOS NAND门的示意图:

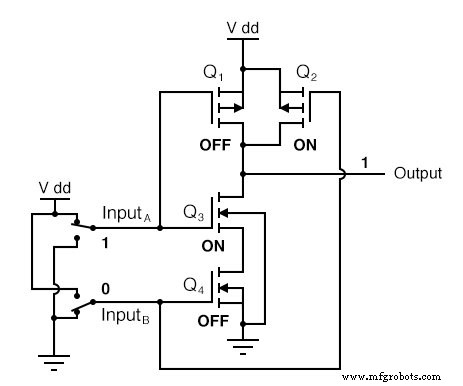

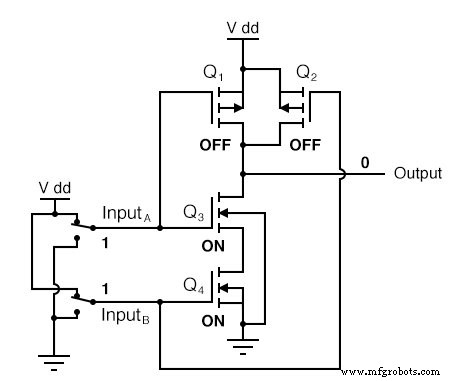

请注意晶体管 Q1 和 Q3 与逆变器电路中的串联互补对的相似之处。两者均由相同的输入信号(输入A)控制,当输入为“高”(1)时,上晶体管关闭,下晶体管导通,反之亦然。

还要注意晶体管 Q2 和 Q4 如何由相同的输入信号(输入 B)类似地控制,以及它们如何对于相同的输入逻辑电平也表现出相同的开/关行为。两对(Q1和Q2)的上方晶体管的源极和漏极端子并联,而下方的晶体管(Q3和Q4)串联。

这意味着如果任一,输出将变“高”(1) 顶部晶体管饱和,只有在两者时才会变“低”(0) 下晶体管饱和。

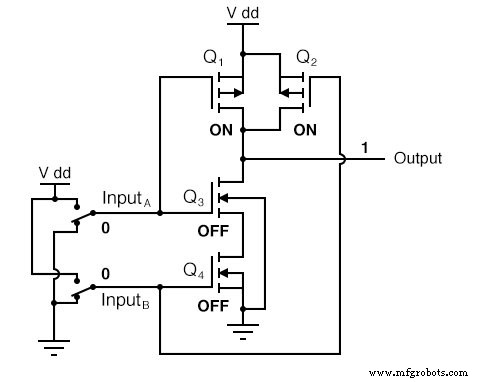

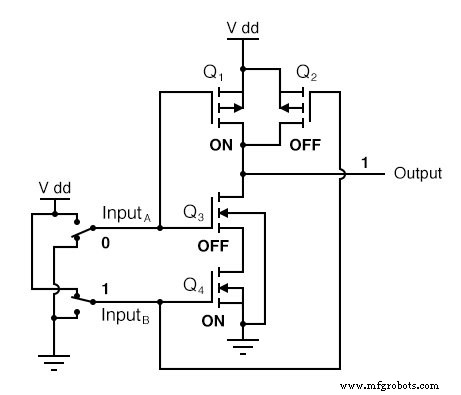

所有逻辑输入的 CMOS 电路行为

以下插图序列显示了该与非门对于所有四种可能的输入逻辑电平(00、01、10 和 11)的行为:

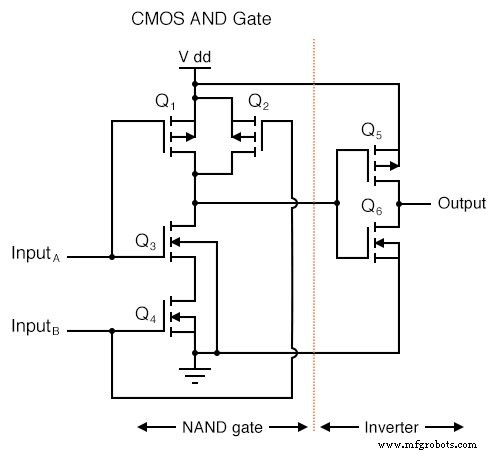

CMOS 与门

与 TTL 与非门一样,CMOS 与非门电路可用作创建与门的起点。所有需要添加的是另一级晶体管来反转输出信号:

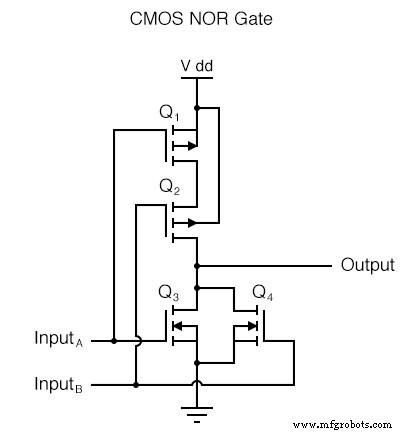

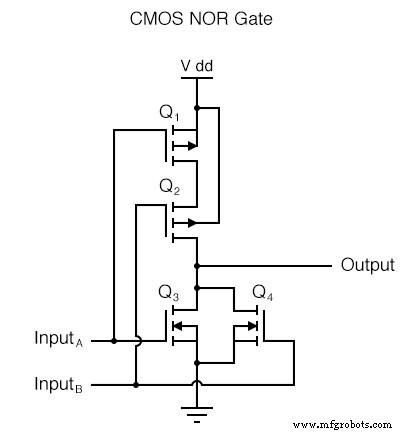

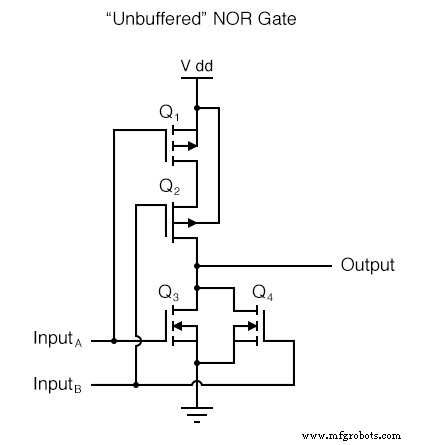

CMOS 或非门

CMOS 或非门电路与与非门一样使用四个 MOSFET,不同之处在于其晶体管的排列方式不同。而不是两个平行的采购 (上)晶体管连接到 Vdd 和两个串联的 sinking (下)晶体管接地,或非门使用两个串联的源极晶体管和两个并联的漏极晶体管,如下所示:

与与非门一样,晶体管 Q1 和 Q3 作为互补对工作,晶体管 Q2 和 Q4 也是如此。每对由单个输入信号控制。如果或者 输入 A 或 输入 B 为“高”(1),至少一个较低的晶体管(Q3 或 Q4)将饱和,从而使输出为“低”(0)。

仅在两者的情况下 输入为“低”(0) 将使两个下晶体管处于截止模式并且两个上晶体管都饱和,这是输出变为“高”(1) 所必需的条件。当然,这种行为定义了 NOR 逻辑功能。

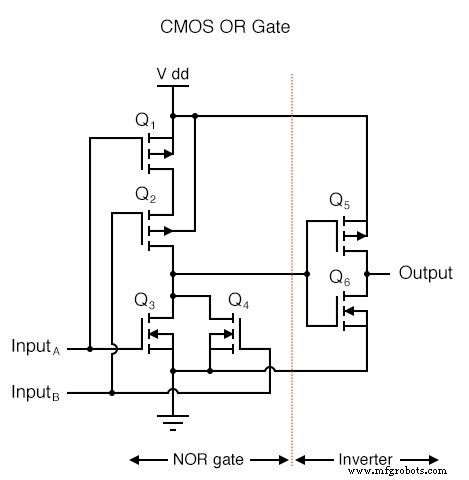

CMOS 或门

OR 功能可以由基本的 NOR 门构建,并在输出端添加一个反相器级:

TTL 与 CMOS:优缺点

既然似乎可以使用 TTL 技术构建的任何门都可以在 CMOS 中复制,为什么这两个逻辑设计“家族”仍然共存?答案是TTL和CMOS都有各自独特的优势。

TTL 和 CMOS 之间的比较列表首先是功耗问题。在这一性能衡量标准中,CMOS 是无可争议的胜利者。由于 CMOS 栅极电路的互补 P 和 N 沟道 MOSFET 对(理想情况下)永远不会同时导通,因此电路从 Vdd 电源汲取的电流很少或没有,除了需要提供的电流负载的电流。另一方面,由于制造它的双极晶体管的偏置要求,TTL 在任何时候都不能在没有一些电流的情况下工作。

不过,这个优势有一个警告。虽然 TTL 门的功耗无论其工作状态如何都保持相当恒定,但 CMOS 门会随着其输入信号频率的升高而消耗更多的功率。如果 CMOS 门在静态(不变)条件下工作,则其耗散功率为零(理想情况下)。

然而,CMOS 门电路在每次输出状态从“低”切换到“高”时吸收瞬态电流,反之亦然。因此,CMOS 栅极切换模式的频率越高,它从 Vdd 电源汲取电流的频率就越高,因此在更高的频率下功耗更大。

CMOS的优势

与 TTL 门相比,CMOS 门从驱动门输出吸收的电流也少得多,因为 MOSFET 是电压控制而非电流控制的器件。这意味着一个门可以驱动比 TTL 输入多得多的 CMOS 输入。衡量单个门输出可以驱动多少门输入的方法称为扇出 .

与 TTL 相比,CMOS 栅极设计的另一个优点是允许的电源电压范围要宽得多。 TTL 门限只能使用 4.75 到 5.25 伏之间的电源 (Vcc) 电压,而 CMOS 门通常能够在 3 到 15 伏之间的任何电压下运行!

电源电压差异背后的原因是 MOSFET 与双极结型晶体管各自的偏置要求。 MOSFET 仅由栅极电压(相对于衬底)控制,而 BJT 受电流控制 设备。

TTL 门电路电阻是为适当的偏置电流精确计算的,假设是 5 伏稳压电源。该电源电压的任何显着变化都会导致晶体管偏置电流不正确,从而导致不可靠(不可预测)的操作。

电源电压变化对 CMOS 栅极的唯一影响是“高”(1) 状态的电压定义。对于在 15 伏电源电压 (Vdd) 下工作的 CMOS 栅极,输入信号必须接近 15 伏才能被视为“高”(1)。 “低”(0) 信号的电压阈值保持不变:接近 0 伏。

CMOS的缺点

与 TTL 相比,CMOS 的一个明显缺点是速度慢。由于使用的是 MOSFET 而不是 BJT,因此 CMOS 门的输入电容比类似的 TTL 门的输入电容大得多,因此 CMOS 门对信号转换(低到高)的响应会更慢反之亦然)比TTL门,所有其他因素都相同。

由电路电阻和栅极输入电容形成的RC时间常数往往会阻碍数字逻辑电平的快速上升和下降时间,从而降低高频性能。

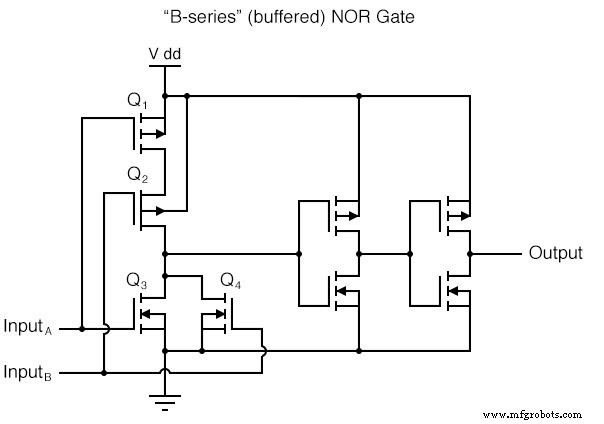

克服劣势的策略

最大限度地减少 CMOS 门电路的这种固有缺点的一种策略是使用额外的晶体管级“缓冲”输出信号,以增加器件的整体电压增益。这为从一种逻辑状态缓慢变化到另一种逻辑状态的输入电压提供了更快的转换输出电压(从高到低或从低到高)。

考虑这个例子,“无缓冲”或非门与“缓冲”或B 系列 , 或非门:

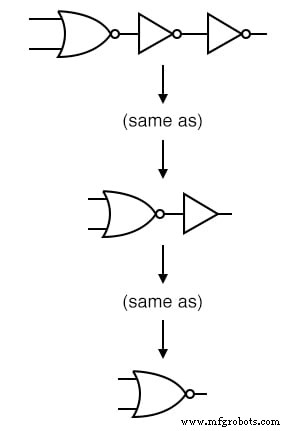

本质上,B 系列设计增强在简单的 NOR 电路的输出端增加了两个反相器。就数字逻辑而言,这没有任何意义,因为两个级联反相器简单地取消了:

然而,将这些反相器级添加到电路中确实有助于提高整体电压增益,使输出对输入状态的变化更加敏感,从而克服 CMOS 栅极输入电容引起的固有缓慢。

评论:

- CMOS 逻辑门由 IGFET (MOSFET) 晶体管而非双极结型晶体管制成。

- CMOS 栅极输入对静电敏感。它们可能会被高压损坏,如果悬空,它们可能会呈现任何逻辑电平。

- 上拉 和下拉 如果由只能提供或吸收电流的信号源驱动,则使用电阻器来防止 CMOS 栅极输入浮动。

- CMOS 门的功耗远低于等效的 TTL 门,但它们的功耗随信号频率而增加,而 TTL 门的功耗在很宽的工作条件范围内大致保持不变。

- CMOS 栅极输入消耗的电流远低于 TTL 输入,因为 MOSFET 是电压控制而非电流控制的设备。

- CMOS 门能够在比 TTL 更宽的电源电压范围内工作:通常为 3 到 15 伏,而 TTL 为 4.75 到 5.25 伏。

- 由于 MOSFET 栅极引起的输入电容,CMOS 栅极的最大工作频率往往比 TTL 栅极低得多。

- B 系列 CMOS 门具有“缓冲”输出,以增加从输入到输出的电压增益,从而加快输出对输入信号变化的响应。这有助于克服 CMOS 门由于 MOSFET 输入电容和由此产生的 RC 时间常数而导致的固有缓慢。

相关工作表:

-

绝缘栅场效应晶体管工作表

-

CMOS 逻辑门工作表

工业技术