嵌入式应用系统中的高速PCB设计研究

现代电子系统正朝着小封装、大规模、高速化的趋势发展,随着SLSI(超大规模集成)芯片密度越来越大,如何分析和处理等问题不可避免。与高速电路设计中的互连和堆叠问题。目前,电子产品的射频频率达到数百或数千MHz,上升沿和下降沿都变得非常陡峭,PCB布局规则和基板材料的介电常数在工艺设计中对系统的电气性能至关重要。这样的产品。

高速PCB设计作为目前大多数电子产品研究中的一个重要过程和步骤,其主要问题包括时序问题、噪声干扰和EMI(电磁干扰),其解决方案关系到系统设计的正常运行。

目前,传统的设计方法导致产品的可靠性和成功率较低,这为嵌入式应用系统中高速PCB设计的研究提供了较高的实用价值和广阔的市场预期。

系统方案设计

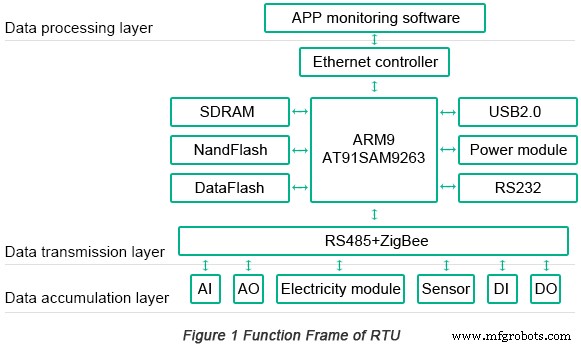

图1为嵌入式RTU(远程终端单元)的功能框架。

从图 1 可以看出,该系统是一个垂直通信结构,由包含电能单元、传感器单元和模拟量测量单元的数据累积层,包含网关的数据传输层组成,通过网关对数据累积层中的数据进行调整。来自互联网接收工程师中心的命令和APP监控软件实现的数据处理层,实时存储和分析数据,使数据曲线面向用户界面,提高数据积累的灵活性和管理效率。

RTU 系统硬件框架

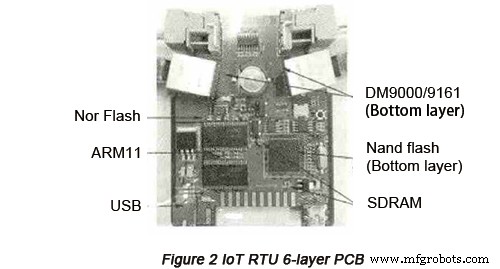

该嵌入式IoT RTU系统硬件主要由USB2.0、AT91SAM9263处理器、CAN、SDRAM、Nand Flash、Data Flash、以太网控制器、时钟芯片、RS232/485接口、电源管理和数据存储部分组成。

本设计采用Linux操作系统,具有更高的内存和设备管理能力,实现了包含复杂算法和通信协议的多任务实时调度,负责网络连接、数据通信和配置积累。图2是本文设计的RTU电路板。

本系统支持IPv6和IPv4双栈,具备及时性和实时性。在数据存储方面,在通信阻塞的情况下可以满足本地存储的要求。通讯接口方面,具有RS485、RS232、CAN等多种现场数据通讯接口,支持Modbus RTU通讯协议,满足不同接口、不同通讯速率的需求。

RTU系统PCB设计

• 系统PCB堆叠设计

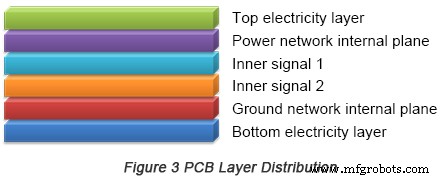

根据设计的难易程度,PCB 的层数通常在 2 到 32 之间。本设计中的 6 层 PCB 是根据元件封装密度、小布局布线空间和高信号频率来确定的。这种 PCB 层分布如下图 3 所示。

本系统对FLASH和SDRAM进行带状线配置,在Inner Signal 1和Inner Signal 2上实现布线。

• 本系统PCB约束规则

在高速 PCB 设计过程中,阻抗连续性和 EMI 受间距、导线长度和宽度以及环路相邻处理的影响很大。元件布局和布线的质量关系到最终设计的成功与否,因此必须合理制定PCB约束规则。

Hyper Lynx 具有干扰图表分析功能,IBIS 模型可用于精确模拟随频率变化的损耗传输、差分信号和通孔模型。在布线前通过Line对主网络进行仿真,改进PCB堆叠结构和布线阻抗,并在仿真结果前设计高速PCB网络布线约束规则,提高设计效率。

• 本系统的PCB仿真

在高速PCB设计过程中,采用理想的传输线模型进行前端仿真,只仿真一次有限的信号线。然而,PCB 后端的传输线实际上是受通孔和平面移位影响的 PCB 布线。在这种情况下,得到的仿真结果非常可靠。

在系统核心电路设计过程中,要求单端信号的端匹配电阻在40~60Ω范围内,信号线间串扰阈值为165mV。另外,为了使DM9000和DM9161的网络控制器能够自适应100Mbps的通信速率,差分阻抗必须在100±5Ω的范围内。 PCB仿真由Mentor Graphic开发的Hyper Lynx仿真软件在SDRAM、以太网差分线、电源完整性和EMC上实现。

一个。 SDRAM设计

在带状线设计过程中,串扰和过孔是导致时延的主要原因。尽管PCB是按照Line仿真工具确定的布线规则完成的,但还是不可避免地会出现一些问题,例如元件引脚过多和PCB尺寸有限。因此,有必要通过Board仿真工具对多个网络进行适当的仿真。

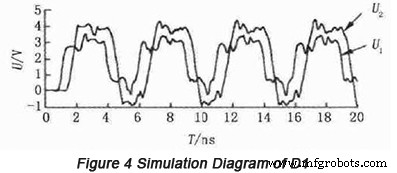

根据仿真结果,模拟网络EBI_D0和EBI_D2的串扰强度超过165mV。两个网络对 EBI_D1 进行攻击并搜索耦合位置,因为黄色标记区域中的蛇形线之间的间距不合适。可以说明,增加走线间距将有助于消除此类问题。然而,我们真正关心的是为什么黑客网络会受到如此强烈的干扰。原因可能在于电阻选择不合适导致阻抗不匹配。至此,终端电阻确定的阻值为43.1Ω。在220MHz激励条件下,网络EBI_D1的分析仿真波形如下图4所示。

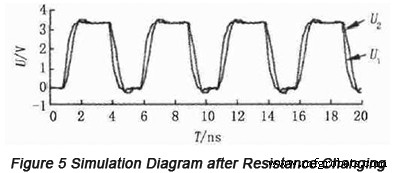

根据图 4,EMI_D1 传输线上发生阻抗不连续,信号波发生变形。虽然不能造成系统启动故障,但产品运行的稳定性很难得到保证。 Back to Board 仿真,通孔和损坏仿真,使 EBI_D0 和 EBI_D1 的终端电阻变为 46.9Ω。因此,电阻变化后的串扰仿真图如下图5所示。

由该图可以说明网络信号得到了改善,对EBI_D1产生的干扰强度明显降低。

湾。互联网差分总线设计

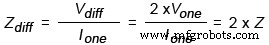

Hyper Lynx开发的Board Simulation模块具有高速和3GIO互连的特性,采用基于差分信号总线的超高速串行数据通路和源同步技术,为高速PCB设计提供便捷高效的解决方案。本系统中的DM9000和DM9161都有两对高速信号差分总线:TX+、TX-和RX+、RX-,差分阻抗为100Ω。由于传输理论,差分阻抗可以根据公式计算:  。

。

在这个公式中,Z 是指每条信号线的传输阻抗,对通信距离和抗噪声能力有至关重要的影响。此处选择 DM9000 将差分传输到网络 TP_E_TX+ 和 TP_E_TX-。为了减少反射的影响,在信号线上平行放置了一个100Ω的电阻,并带有通孔。

C。本系统的电源完整性设计

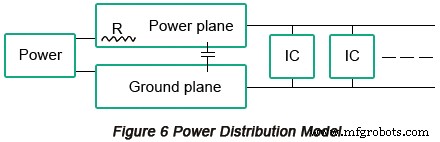

图6是一个基本的配电模型,其中电流通过电源层传输到每个载波,然后到地层。

在高速PCB设计过程中,必须计算电路系统中各单元的能耗,正确分配电网宽度并适当放大。

6层的电源完整性可以总结为:最大压降2.1mV,接近0.06%;最大电流密度为16.3mA/m²;在合适的范围内,如果电流密度超过 50 mA/m²,PCB 的温度会升高,影响主芯片和信号线在工作过程中的运行。铜宽的增加可以降低电流密度,增加信号引线的厚度有利于PCB温度的降低。

d。系统电磁兼容分析

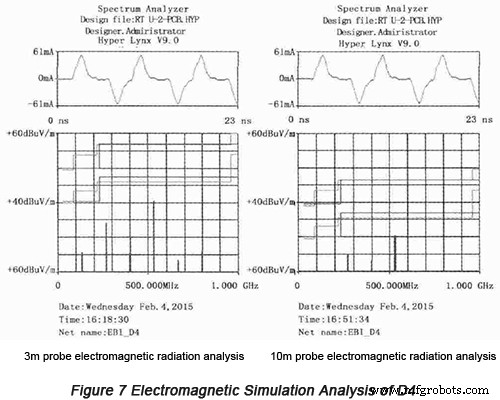

电磁干扰通常以耦合方式与有用信号作为载体传输。在本设计中,采用 Hyper Lynx 仿真软件对初步设计后的 PCB 辐射强度进行分析。关键信号线 D4 位于 ARM9 和 SDRAM 之间,探针位置分别为 3m 和 10m。在220MHz激励源的情况下,可以获得FCC和CISPR国际标准的仿真数据,如下图7所示。

根据仿真结果,与PCB的短距离导致电路板的高辐射,并且辐射随信号频率的变化而变化。在高速电路设计过程中,可以优化PCB抗干扰,同时降低噪声辐射。

有用的资源

• 高速布局技巧

• 减少 EMI 影响的高速 PCB 布线技术

• 对高速 PCB 设计的误解和策略

• 元件嵌入PCB 制造技术

• 嵌入式技术和元件嵌入式 PCB 组装程序

• PCBCart 的全功能 PCB 制造服务 - 多种增值选项

• PCBCart 的高级 PCB 组装服务 - 从 1 件开始

工业技术