高密度FDR互连开关板的设计与实现

如今,应用高速串行传输的高性能计算机互连网络的传输速率已经发展到从初级SDR(单数据速率,2.5Gb/s)到第四代FDR(十四数据速率,14Gb/s)。 s)、DDR(双倍数据速率,5Gb/s)和 QDR(四倍数据速率,10Gb/s)。互联互通的PCB(印刷电路板)设计以及形成互联网必不可少的开关板和接口卡,已进入FDR高速高频领域。由于 FDR 信号的上升时间已大幅降低到 10ps 量级,一系列与信号完整性有关的问题已成为决定功能实现和可靠运行可能性的关键特征,如衰减、串扰、反射、电磁干扰等. 基于FDR互连芯片多端口、多通道、多功率类别和高能耗的特点,为了提高吞吐率,总是需要在单个互连板上集成多个互连芯片。在空间有限的板上,一方面要满足一些要求,包括元件布局和散热、高密度布线、跨板背长距离传输以及各种信号的完整性。另一方面,必须考虑一些因素,包括 PCB 设计周期、PCB 制造技术限制和成本控制。因此,设计实现和仿真验证难度极大。本文以FDR互连和开关板的PCB设计实例为基础,从基板选材、叠层设计、布线规则和抗干扰设计等方面提出一些优化方法,以解决各种信号的完整性问题。 FDR高速PCB设计过程。

衰减属性和基材选择

对于 FDR 高频信号,传输线损耗是涉及信号完整性的问题。当FDR信号沿互连通道从发射端传输到接收端时,由于高频衰减远大于低频衰减,到达接收端的信号波形发生了严重变形。变形主要分为两个方面:信号的电压摆幅大幅度下降,信号上升沿出现劣化。前者限制了信号的传输距离,而后者则导致码间干扰。传输线损耗A可以看作是导体损耗Acond和介质损耗Adiel之和,如公式(1)所示:A =Adiel + Acond。

导体损耗是指信号路径和返回路径之间的铜导体上的串联电阻引起的损耗。在高频情况下,趋肤效应使电流在周围的铜导体表面流动。随着铜导体等效串联电阻的增加,导体损耗会随着频率的增加而增加,与频率的平方根成正比,如公式(2)所示:  。

。

介电损耗是指基板材料的介质产生的损耗,主要由材料属性决定,与导体宽度等几何结构无关,与频率成正比,如式(3)所示:  。

。

根据公式(2),线宽的增加能够降低导体损耗。然而,在实际的PCB设计中,由于管脚间距、板子间距、信号层数和阻抗等因素的限制,导体的宽度永远不可能无限宽。 FDR设计中常用的导体宽度/间距/宽度通常为7mil/7mil/7mil或8mil/10mil/8mil。当导体宽度相同时,导体损耗与导体长度成正比,与材料无关。因此,要降低整体传输损耗,只需考虑介电损耗即可。由式(3)可知,介电损耗与损耗因数成正比,应用较小的损耗因数有助于降低介电损耗,导致整体传输损耗。

表1列出了传输速率为14Gb/s,导体宽度为8mil,阻抗为50Ω时,三种普通高速板材料的属性参数和根据公式(1)、(2)和(3)计算的损耗值。

| 板料参数 | FR4 | Nelco4000-13SI | Megtron6 |

| [email protected] | 0.02 | 0.008 | 0.004 |

| [email protected] | 4.10 | 3.200 | 3.600 |

| Acond@7GHz/in | 0.24 | 0.240 | 0.240 |

| Adiel@7GHz/in | 0.65 | 0.230 | 0.120 |

| [email protected]/in | 0.89 | 0.470 | 0.360 |

| [email protected]/30in | 27.00 | 14.000 | 11.000 |

| 相对成本 | 1.00 | 3.500 | 8.000 |

可以看出,在传输速率为14Gb/s,传输长度为30inch的情况下,Nelco4000-13SI的整体传输损耗约为14dB,而典型FDR芯片所能承受的电压摆幅衰减在20dB到20dB之间。 25分贝。因此,这种板材可以应用于传输距离小于30英寸的FDR互连开关板设计。但FR4的整体传输衰减约为27dB,FR4不能用于长距离设计的FDR设计,但允许传输距离短的FDR互连接口卡选择FR4以降低成本。至于整体传输衰减最小的 Megtron6,其成本最高,在 FDR 中的应用导致系统架构费用增加。综上所述,对于高频PCB,板材是基础,板材的选择决定了信号的传输长度。

布局和堆栈设计

对于PCB设计,必须首先考虑电路板结构和堆栈。通常,电路板的图案和形状已经确定,堆叠数量的确定在于信号频率、电路板引脚密度、PCB制造成本、制造周期和可靠性要求。 FDR互连开关板具有较高的频率和密度,多层板的应用是减少干扰的必要步骤。另外,栈数的确定也很关键。

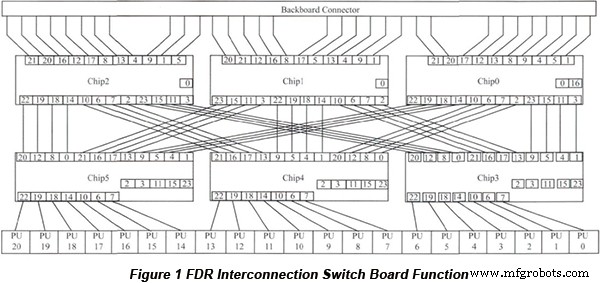

FDR互连芯片上有24个端口,在互耦的操作方法中,每个端口具有8个Tx通道和8个Rx通道。 FDR互连板采用6个互连芯片和3个下行芯片,通过背板连接器接入32个端口。 3 个上行芯片通过 QSFP(Quad Small Form-factor Pluggable)光纤接入 21 个端口。上行芯片和下行芯片通过4个端口相互连接,如图1所示。

FDR采用BGA(Ball Grid Array)封装,面积50mmx50mm,1157个引脚,间距1.0mm,Tx和Rx端口的P/N引脚按3个同心圆分布。理论上,可以应用3个信号层将所有端口的所有引脚引出BGA。考虑到以下两个元素,可以使用两个信号层来访问一组同心圆引脚。

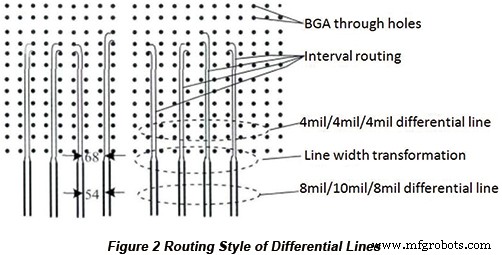

a.由于间距的限制,差分线的线宽/间距/宽度为4mil/4mil/4mil,从BGA出来后扩展成8mil/10mil/8mil,差分线对之间的距离不小于5000万。因此,一对差分线必须占据2mm的宽度,48对信号沿着密度最大的边缘。所以这个方法很难实现。

b. BGA 引脚间距为 1mm。如果应用一个信号层接入一组同心圆信号,BGA下差分线对之间的间距只有14mil,与要求的50mil相差甚远。而且最大并行走线长度只有20mm,会产生一定的串扰。

为避免上述不利因素,采用两个信号层接入一组同心圆信号,每个信号层的差分信号必须按照50mil间距引出BGA。因此,FDR互连板至少需要6层才能将差分信号全部引出BGA。考虑到板子的连通性和布线量以及足够的板面交换耦合电容,采用8个内部信号和22层堆叠。

串扰分析和减少措施

串扰是高速高密度电路设计的首要考虑因素。当攻击线中的电压和电流发生变化时,攻击线和受害线之间会通过互电容和互感发生电磁耦合。沿受扰线流向发送端的串扰称为近端串扰,而沿受扰线流向接收端的串扰称为远端串扰。一般来说,受害线上的整体噪声电压应控制在信号电压的 5% 以下。考虑其他噪声源和受害线两侧的进攻线,单边进攻线的串扰预算最好控制在1%以内。

在减少串扰方面要遵循的关键点包括:

a.应加大进攻线与受害线的间距,减少平行走线长度。

b.集成地被用作信号的返回路径。根据经验法则,对于50Ω的带状线,当间距为线宽的3倍时,近端串扰约为0.5%。对于 50Ω 的微带线,当间距为线宽的 3 倍时,近端串扰约为 1%。带状线或全嵌入式微带线的远端串扰几乎为零,微带传输线的远端串扰极性为负,幅度较大,因为电感耦合的影响大于电容耦合。

• 间隔路由

在本设计中,高速差分线的差分阻抗为 100Ω。基于Si9000场求解器,线宽/间距/线宽计算为8mil/10mil/8mil。线越宽衰减越小,10mil的间距是为了保持100Ω的差分阻抗。这种差分线应用在 BGA 芯片区域之外。为了减少串扰,两对差分线之间的间距不小于80mil。本文互连芯片的引脚间距为1mm,BGA的通孔尺寸限制使得BGA芯片区域内差分线的线宽/间距/线宽为4mil/4mil/4mil。这种差分线虽然差分阻抗也是100Ω,但是引线损耗大,需要4mil/4mil/4mil的差分线一进入BGA芯片区就变成8mil/10mil/8mil。为了减少串扰,BGA芯片区的4mil/4mil/4mil差分线采用间隔布线的方式,保证两对差分线之间的间距也大于50mil,如图2所示。

• 差分孔

Specific differential holes are set in this design for the application of exchange coupling capacitance on the connection surface layer. Ground holes have to be placed beside differential holes to provide backflow channel for returning path. Design of four ground holes features the best effect and two ground holes can be also applied when the area of board is limited. Besides, measures such as back drilling and internal pad eliminationhave should be taken to differential holes to reduce the impedance change at differential holes in order to decrease crosstalk and reflection.

• Preventing Tx and Rx from being routed in the same layer

In order to reduce crosstalk, Tx differential line should be routed in the different layer from Rx differential line. Here, Tx refers to the source terminal of differential line while Rx refers to the receiving terminal of differential line. If both of them have to be routed in the same layer, the spacing between them has to be over 5mm to ensure safety.

• 20H rule

In the PCB circuit with high frequency and high speed, RF energy is coupled by PCB power layer and ground layer and edge magnetic flux leakage is generated between power layer and ground layer. The radio RF energy can be radiated to the free space. 20H rule indicates that if there are high-speed currents on the board, there are electromagnetic fields associated with them. In the design of this article, the distance between all the routings and board edge should be at least 20 times of line width and the distance between high-speed differential holes and power plane cut-off lines is at least 5mm.

• Routing on the surface layer

In the design of high-frequency PCBs, with the relatively big far-end crosstalk between microstrip lines and strip lines considered, high-speed differential lines are prohibited on the surface layer. In the design of this article, at most 8 internal routing layers are required owing to the limitation of manufacturing craft. Moreover, the terminal arrangement limitation of interconnection chip makes it impossible for internal layers only to implement the connections of the interconnection differential lines between 6 chips inside connection board.

Helpful Resources

• Something You Must Know about HDI

• History of High-Density Packaging Technology

• 3 Keys to Designing a Successful HDI PCB

• Advantages of HDI Printed Circuit Boards

• Full Feature PCB Manufacturing Service from PCBCart - Multiple Value-added options

• Advanced PCB Assembly Service from PCBCart - Start from 1 piece

工业技术