高速PCB设计的误区与策略

就高速电子系统而言,印刷电路板设计的成功直接导致电磁兼容(EMC)系统在理论和实践上的高度解决。为了达到EMC标准,高速PCB设计面临着巨大的挑战,高速PCB设计人员在设计过程中必须摒弃传统的设计理念和方法。本段主要从实践的角度分析高速PCB设计过程中的误区和策略。

高速PCB材料的介电常数

迄今为止,高速PCB设计主要有3种设计技术:噪声和延迟PCB图形设计技术、阻抗和传播延迟时间控制技术和以PCB阻抗为参数的评估技术,其中后两类技术是PCB制造的核心。高速PCB制造传输的技术也很多,常用的基本结构是微带和带状线。对于高速PCB传输线,Z0 即阻抗参数和 tpd 也就是说,传播延迟时间是最重要的变量。实际上,如果微带线的结构与带状线的结构不同,计算公式也会有所不同。然而,无论如何,阻抗始终是传输线的几何结构。在大多数情况下,部分PCB材料的介电常数受频率、面积吸水率、温度和电气特性的影响。对于两层或多层PCB,其介电常数受PCB材料中树脂和硅的比例影响。

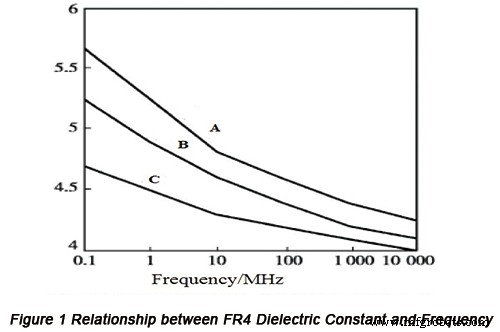

如今,最常用的PCB材料是FR4。通常,PCB 材料供应商会根据项目技术人员将使用该材料的情况来指明介电常数的值。在实际应用中,数值参数通常是在1MHz的情况下得到的,而在高速情况下,介电常数有明显的变化,如图1所示。

图 1 中的三条曲线指的是硅和树脂的不同比例。 3条曲线中,A曲线最高,B曲线中等,C曲线最低。一旦操作者没有注意到差异,计算或仿真结果与实际情况在阻抗和传播延迟时间上可能会出现很大偏差,从而影响高速系统信号完整性设计。

90°角问题

大多数文档中的 PCB 布线应避免 90° 角,因为它可能会导致阻抗不连续和电磁干扰 (EMI) 辐射。从理论上讲,90°角的宽度变化比较大,导致阻抗大,阻抗不连续性严重。从实践来看,电磁功率往往会聚集在走线的拐角处,拐角越尖,聚集的功率就越多。综合以上分析可知,EMI辐射在90°角处最为突出。

但也有研究人员发现,90°角对阻抗的影响在10%以内。对于 6mil 的布线宽度,如果它成为关键长度,那么它将在 THz 范围内。因此,可以估计,在实际情况下,90°角一定会导致阻抗不连续。

因此,在实际的PCB布线中,至少在GHz范围内,没有必要不惜代价避免90°角。

20-H 原则

自 KNG 提出 20-H 原理以来,它已被接受为高速 PCB 设计的主要原理。甚至一些研究人员表示,这一原理能够帮助相关 PCB 层上的环境电磁密度降低约 70%。此外,它还对减少向外的EMI辐射起到了有效的作用。然而,很多实验并不支持研究人员的预期。

一些实验表明,对于两层PCB,20-H原理会导致更严重的辐射,而对于多层PCB,在内部介质层中使用20-H原理并没有带来明显的改善。

滤波电容参数

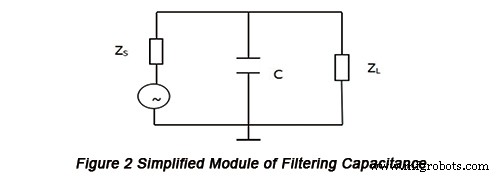

滤波电容是一种经过验证的有效且经济的测量方法,用于解决电子系统中的 EMC 问题。然而,高速电子系统对滤波电容的性能和适用设计提出了新的要求。滤波电容的简化模块如图2所示。

它必须满足以下要求:ZC

然而,在高速电路中,ZS 也不是 ZL 是纯电阻,需要复杂的值。同时,ZC 在高速电路中不是纯电容,必须同时考虑等效串联电阻和等效串联电感。这些都是滤波电容在高速电子系统中应用的难点。一旦设计者忽略了这些方面,计算或仿真结果与实践就会出现明显的差异。

硅封装

PCB设计人员往往最关注PCB布局和PCB上组件之间的互连,而忽略了组件封装的重要性。事实上,这可能会对高速PCB设计产生严重后果。硅封装通过连接线和引线的寄生电感、寄生电阻和寄生电容对硅的性能产生影响。这些参数将产生噪声、通信延迟、边缘速率和频率响应。不同封装的寄生参数可能相差很大。相同电路、不同封装的硅片,其性能表现出不同的特点。

事实上,对于高速电子系统,芯片设计、封装设计和板级设计从来都不是相互独立的。对于硅上的设计流程,必须根据 PCB 选择合适的封装。硅设计的整体布局受技术和板级元素的影响。对于硅封装来说,它与PCB的匹配是一个必须考虑的因素。更重要的是,一个合适的封装对于板级的完整性和EMC/EMI问题有很大帮助。因此,硅封装绝不能被忽视或轻视。

共模电流辐射干扰

在PCB的信号传输引线中,存在传输有用信号的差模电流和无有用信息的共模电流,两者都会产生EMI辐射。

由于其相对较高的电流,差模电流已被电路设计人员强调,并形成了控制差模电流EMI辐射的理论和技术。因此,一些 EDA 工具具有差模电流 EMI 辐射仿真和预测功能。但与差模电流相比,共模电流要小得多,容易导致设计人员对共模电流EMI辐射的忽视。

然而,根据最近的研究,虽然共模电流远小于差模电流,但前者产生的EMI辐射干扰远大于后者。时至今日,共模电流EMI辐射已成为高速先进电路板辐射的主要干扰源之一。更糟糕的是,共模电流EMI辐射的产生原因复杂,既无法模拟,也无法预测。此外,控制共模电流EMI辐射的研究还在进行中。

因此,在设计高速PCB时,仅基于差模电流EMI辐射来模拟和预测EMI辐射是不可靠的。

有用资源

• 高速布局技巧

• 降低EMI影响的高速PCB布线技术

• 嵌入式应用系统中的高速PCB设计研究

•高速PCB设计的差分等距处理和仿真验证

• 如何设计高速PCB的图像平面

• 高速PCB设计对信号完整性的挑战及其解决方案

• 抑制高速 PCB 布局中的信号反射方法

• 高速数模混合电路的信号完整性分析和 PCB 设计

• PCBCart 的全功能 PCB 制造服务 - 多种增值选项

• PCBCart 的高级 PCB 组装服务 - 从 1 件开始

工业技术