最近的论文详细介绍了碳纳米管的可扩展性、集成突破

碳纳米管 (CNT) 对半导体行业很有吸引力,因为与仅 1 纳米厚度的硅相比,它们是优越的电导体。那么为什么我们没有在从大型机到移动设备的所有设备中使用 CNT 芯片呢?晶体管的可扩展性和大规模集成仍然是很大的挑战。但是我和我的同事最近在Science上发表了两篇论文 和自然纳米技术 在这两个对 CNT 芯片现实至关重要的领域显示出有希望的突破。

足迹成就提示纳米级

第一:缩放。我们知道 3D FinFET 硅芯片可能会在 7 纳米达到其功率和性能极限。虽然最近发布的 5nm 硅纳米片晶体管在下一个节点上提升了规模、功率和性能,但我们也知道它的局限性。

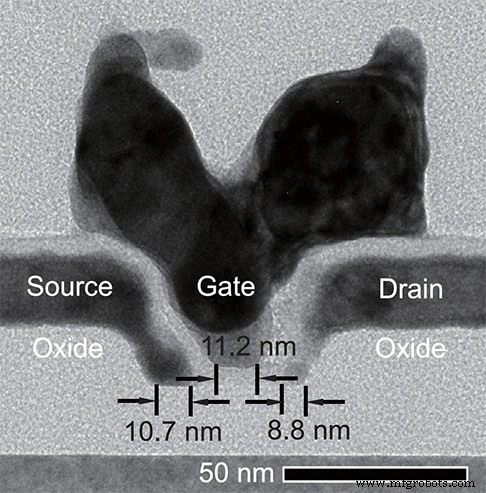

一个晶体管不仅仅是它的门。源极、漏极和间隔物加起来就是一个总占地面积。图为:40nm 封装的 CNT 晶体管。 (“碳纳米管晶体管缩放到 40 纳米足迹”中的图 1B,发表在《科学》杂志上。)

在我们的科学 论文“碳纳米管晶体管缩放到 40 纳米的足迹”,我们将整个 CNT 晶体管缩放到国际半导体技术路线图 (ITRS) 晶体管达到 40 纳米足迹的目标——这是他们设定的目标,自 2015 年以来没有改变. 供参考,今天的顶级14nm晶体管实际上占用了大约90nm的芯片空间。

我们可以潜在地将 CNT 晶体管扩展到比硅更远的地方,主要原因是它们本质上只有 1.2 nm 厚。这种薄 具有将栅极长度减少到 10 nm 的多米诺骨牌效应,因为它提供了更好的栅极静电控制,并有助于最大限度地减少电流泄漏。此外,电子在碳纳米管中的传播速度比硅快,从而提高了器件性能。

但是我们需要一种新方法将 CNT 连接到它们的源极和漏极(如图)。我们必须找到能够在可制造温度下将这些 10 纳米元件“烘焙”在一起的完美材料组合。我们之前工作的源极和 CNT 以及漏极和 CNT 之间的末端键合接触需要如此高的处理温度,大约为 850°C,因此通道不能短于 60-100 nm。切换到钴钼合金用于元件之间的布线有效地将温度降低到可接受的 650°C - 将距离缩小到 10nm。

该论文的第一作者曹庆博士和团队的其他同事证明,在这个新实现的占位面积上,CNT 晶体管的性能可以与当今的晶体管标准相媲美。

CNT 元件在环形振荡器上聚集在一起

展示这样一个极其大规模的单晶体管,即使工艺流程不太容易制造,也让我们有动力解决实际 CNT 技术的集成挑战。在过去的五年里,我的团队一直在开发 CNT 技术的各个元素。我们知道如何分离半导体碳纳米管,使碳纳米管在晶片上“自组装”,并使用各种技术制造可靠的 n 沟道 CNT 场效应晶体管或“FET”(通常会因接触金属氧化而迅速降解)。

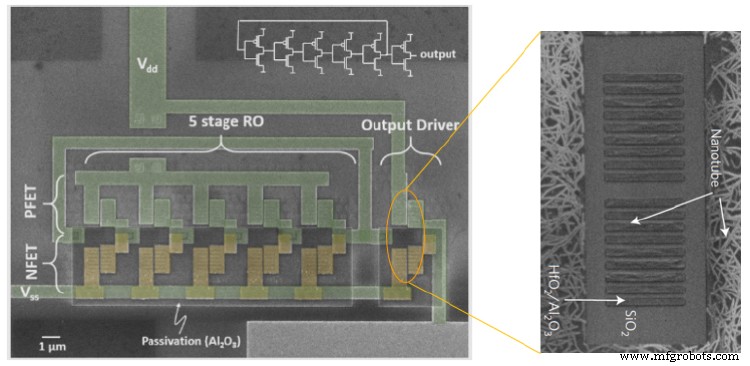

所有元素必须在功能环形振荡器中同时工作.图示:5 级 CNT 环形振荡器和 CNT 放置的沟槽的俯视扫描电子显微镜图像。 (图 1B 中“具有溶液处理自组装碳纳米管的高速逻辑集成电路”,发表在 Nature Nanotechnology 上。)

开发颠覆性的早期技术的挑战在于,用于解决一个问题的某些技术最终可能会破坏设备和电路的其他元件。这就是为什么所有基于纳米技术的演示(如使用 CNT 的演示)仅限于非常低的集成水平的根本原因。并且对实际使用它们的可行性产生了怀疑。

但是我们在解决自然纳米技术中的这一集成挑战方面向前迈出了一大步 论文,“具有解决方案处理的自组装碳纳米管的高速逻辑集成电路”,我们展示了如何将所有部件放在一起以制作任何逻辑技术中的标准基准电路 - CMOS 环形振荡器。

汤建士博士和我的其他团队成员结合我们之前开发的方法来纯化和放置 CNTs(单独来看,它们看起来像漂浮在溶液中的通心粉),但通过添加侧壁氧化物来保护 n-FET 通道进行了一个关键的调整避免制造过程中的退化(侧壁导致成品率提高三倍,进一步确保满足环形振荡器上所有元件同时工作的要求)。

论文中描述的功能性 5 级 CMOS 环形振荡器(如上图所示)已经可以在 1 V(行业标准)下工作。尽管通道中的 CNT 密度较低(您可以在同一张图片中看到六个 CNT)并且参数放宽,但级开关频率达到 2.8 GHz(355 皮秒)——这是打破任何基于纳米技术的演示的 GHz 障碍的第一个例子。预计,凭借每微米超过 100 个碳纳米管的密度和适当缩放的器件尺寸,我们可以实现亚皮秒级延迟,明显快于当今的硅芯片。

正如我们在论文中所写:

<块引用>由于CMOS环形振荡器直接反映了技术的成熟度,人们期待已久的证据表明,将这种有前途的材料转变为真正的技术的重要问题正在得到大力解决。

保存

纳米材料