高速数字电路PCB设计中的阻抗控制

阻抗控制技术在高速数字电路设计中非常重要,必须采用有效的方法来保证高速PCB的优异性能。

PCB上高速电路传输线的阻抗计算与阻抗控制

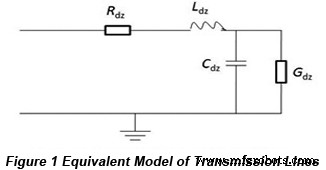

• 输电线路等效模型

图1显示了传输线在PCB上的等效效应,是一种包括串联和多个电容、电阻和电感的结构(RLGC模型)。

串联电阻的典型值在 0.25 到 0.55ohms/foot 的范围内,多个电阻的电阻值通常保持很高。加上PCB传输线上的寄生电阻、电容和电感,传输线上的总阻抗称为特性阻抗(Z0)。线径大、靠近电源/地或介电常数高的情况下,特性阻抗值相对较小。图 3 为长度为 dz 的传输线的等效模型,据此可推导出传输线的特性阻抗为:  。式中,L为传输线上各单位长度的电感,C为传输线上各单位长度的电容。

。式中,L为传输线上各单位长度的电感,C为传输线上各单位长度的电容。

• PCB上传输线的阻抗和延迟计算公式

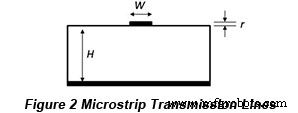

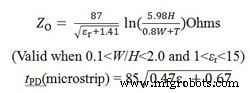

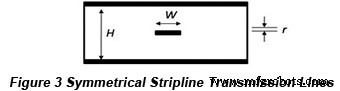

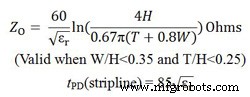

| PCB 上的传输线 | 阻抗和延迟计算公式 |

|  |

|  |

上式中,Z0指阻抗(欧姆),W指线宽(英寸),T指线粗(英寸),H指到地的距离(英寸),指基板的相对介电常数,tPD指的是延迟时间(ps/inch)。

• 输电线路阻抗控制布局规则

综合以上分析,阻抗和信号的单位延迟与信号频率无关,但与电路板结构、电路板材料的相对介电常数、走线的物理属性有关。这个结论对于理解高速PCB和高速PCB设计极为重要。此外,外层信号传输线的传输速度比内层快得多,因此在关键线路布局的安排上必须考虑到这些因素。

阻抗控制是实现信号传输的重要前提。但是,根据传输线的板结构和阻抗计算公式,阻抗仅取决于PCB材料和PCB层结构,同一条线的线宽和布线特征不变。因此,一条线路的阻抗在PCB的不同层上不会发生变化,这在高速电路设计中是不允许的。

本文设计了一种高密度的高速PCB,板上的大部分信号都有阻抗要求。例如,CPCI信号线的阻抗应为65Ω,差分信号为100Ω,其他信号均为50Ω。根据PCB布线空间,至少要使用10层布线,并确定16层PCB设计方案。

由于板子的整体厚度不能超过2mm,因此在叠放方面存在一些困难,考虑到一些问题:

1)。每个信号层都有相邻的图像平面,以保护阻抗和信号质量。

2)。每个电源层旁边都有完整的接地层,可以很好地保证电源的性能。

3)。板子叠放需要平衡,避免板子翘曲。

介质的介电常数设为 4.3。基于上面的堆叠设计,线宽和线间距要根据计算结果来设置,以保证信号阻抗的要求。线宽得到如下结果:

1)。表层信号线宽度5mils,阻抗58.7Ohms。

2)。表层CPCI信号线宽度4.5mils,阻抗61.7Ohms。

3)。内层信号线宽度4.5mils,阻抗50.2Ohms。

4)。内层和表层BGA区线宽4mil,表层阻抗64.6Ohms,内层阻抗52.7Ohms。

5)。内层微带差分线宽5mil,线间距6mil,阻抗100.54Ohms。

6)。内层带状线差分线宽4.5mil,线间距10mil,阻抗96.6Ohms。

线间距设置如下:

1)。表层信号线间距(5mils)为5.0mils。

2)。表层CPCI信号线(4.5mils)间距为9.0mils。

3)..内层信号线(4.5mils)之间的距离为7.0mils。

4)。表层与内层线间距为4.0mils。

5)。内层差分信号线之间以及与其他信号线之间的距离至少要保持25mils。

6)。表层差分信号线之间以及与其他信号线之间的距离至少要保持20mils。

PCB印刷后,用POLAR-Cits500阻抗测试仪测试测试板的阻抗,结果如下表。数据表明,在高速PCB设计制造过程中,阻抗必须控制在50Ohm0%、60Ohm0%和100Ohm0%的范围内。

| 预设阻抗(欧姆) | 实际阻抗(欧姆) |

| 50 | 47.52-52.33 |

| 60 | 57.65-61.35 |

| 100 | 93.65-106.35 |

LVDS 及其对 PCB 的阻抗控制

• LVDS

LVDS是一种高速串行信号传输电平,具有传输速度快、功耗低、抗干扰能力强、传输距离远、匹配可行等优点。 LVDS的应用领域包括计算机、通信和消费。

• LVDS的阻抗设计

LVDS电压摆幅仅为350MV,最长传输距离超过10米。为了保证信号在传输线中传输过程中不受反射信号的影响,传输线的阻抗必须控制在单线阻抗50Ω,差分阻抗100Ω。在实际应用中,可以通过设置合理的叠层厚度和介质参数,调整线宽和线间距,借助一些高速仿真分析工具计算单线和差分线的阻抗来控制阻抗。

然而,大多数时候,要满足单线阻抗和差分阻抗的要求是比较困难的。一方面,线宽W和线间距S的调整范围受物理设计空间的控制。例如,带有 BGA 或 DIP 的边缘连接器中的布线和线宽受焊盘尺寸和距离的影响。另一方面,W和S的变化会影响单线和差分阻抗的结果。到现在为止,搞清楚预设线宽和线距之间的关系已经很容易了。

• LVDS 路由规则

一般来说,差分信号走线是按照阻抗设计规则来实现的,这样可以保证LVDS的质量。在实际布线中,LVDS应符合以下规则:

1)。差分对应尽可能短,线应直,通孔数量应减少。差分对中信号线之间的距离应相同。所有这些规则都有助于避免长路由和大量关闭。至于关断,应该用45度关断,而不是90度。

2)。差分对之间的距离应保持在 10 倍以上,以减少线路之间的串扰。必要时可在差分对之间放置接地通孔进行隔离。

3)。 LVDS 不能跨表面分割。虽然两个差分信号是相互返回的路径,但信号返回路径并不能因为跨面分裂而被截断。然而,传输线可能会因缺乏像平面而导致阻抗不连续。

4)。避免层之间的差分信号。在PCB制造过程中,层间的堆叠对准精度远低于同层的蚀刻精度,加上堆叠过程中的介质损耗,都会导致差分对之间的差分阻抗发生变化。

5)。在阻抗设计中,应采用耦合法。

6)。应设置合适的 PCB 堆叠结构,以确保电压电平信号与 LVDS 之间的隔离。在可能的情况下,可以将高速 TTL/CMOS 等信号设置在不同的层上,通过接地层和电源层与 LVDS 布线隔离。

7)。差分信号对应与走线长度相适应。

有用的资源

• 影响 PCB 特性阻抗的元素和解决方案

• 刚硬 PCB 的阻抗设计注意事项

• 如何分析和禁止高速 PCB 电源的阻抗

•过孔的阻抗控制及其对 PCB 设计中信号完整性的影响

• PCBCart 的全功能 PCB 制造服务 - 多种增值选项

• PCBCart 的高级 PCB 组装服务 - 从 1 件开始

工业技术