基于双栅极 TFET 的无电容 1T DRAM 的编程优化

摘要

较大的电容体积和较高的晶体管漏电流已经成为传统的一晶体管(1T)-一电容(1C)动态随机存取存储器(DRAM)的固有缺点。近来,隧道FET(TFET)由于其低截止电流和高开关比被应用于DRAM单元。具有无电容器结构的双栅极 TFET (DG-TFET) DRAM 单元具有卓越的性能——更高的保留时间 (RT) 和较弱的温度依赖性。但是 TFET DRAM 单元的性能对编程条件很敏感。本文使用仿真工具Silvaco Atlas详细讨论了编程优化的指导原则。 DG-TFET DRAM 的写入和读取操作都依赖于带间隧道 (BTBT)。在写操作期间,来自Gate2 控制的BTBT 的空穴存储在Gate2 下的势阱中。在保持“1”期间,在 Gate2 处施加一个小的负电压以长时间保留空穴。 Gate1控制的BTBT主要影响读取电流。使用优化的编程条件,DG-TFET DRAM 获得更高的读“1”与读“0”的电流比(10 7 ) 和超过 2 秒的 RT。较高的RT降低了DRAM的刷新率和动态功耗。

背景

动态随机存取存储器 (DRAM) 已成为移动和计算系统中不可或缺的存储单元 [1,2,3]。随着器件几何尺寸的缩小,大容量电容成为传统单晶体管(1T)-单电容(1C)DRAM单元的先天不足,限制了其大规模应用。与传统的 1T-1C DRAM 相比,基于浮栅晶体管的无电容器 1T DRAM 单元在存储器的高密度封装方面显示出潜在优势 [4]。在浮栅晶体管中,衬底区的电荷通过福勒-诺德海姆隧穿存储在浮栅区。读取操作取决于热电子发射 [5, 6],这与金属氧化物半导体场效应晶体管 (MOSFET) 相同。因此,带有浮栅晶体管的DRAM的读取电流对温度有很强的依赖性。此外,热电子发射导致晶体管的亚阈值摆幅(SS)高于60 mV/dec,这使得高漏电流和功耗成为主要挑战[7,8,9]。

最近,隧道场效应晶体管 (TFET) 被认为是未来低功率电子器件的有希望的候选者 [10,11,12]。 TFET 的主要传导机制是带间隧穿 (BTBT) 而不是热电子发射,这使其具有低于 60 mV/dec SS、低断态漏电流和弱温度依赖性等优点[13, 14]。迄今为止,关于TFET的大量研究工作主要集中在单个TFET器件性能的研究上,也有一些由TFET组成的简单电路。然而,高I 在/我 关闭 TFET 使其能够用于 DRAM 单元 [15]。尤其是低断态漏电流可以降低读“0”电流和DRAM单元的功耗。研究人员设计了一种具有无电容器结构的双栅极 TFET (DG-TFET) DRAM [16]。在DG-TFET DRAM中,写操作时的电荷存储是基于沟道和漏极之间的BTBT,主要由Gate2产生。同时,电子的隧穿促进了Gate2下方沟道区空穴的积累。 Gate1主要负责读操作。 DGTFET DRAM的读取电流主要依赖于源区和沟道区之间的BTBT。一些研究小组已经证明,DG-TFET DRAM 的读取电流对温度的依赖性很弱。并且 DG-TFET DRAM 可以获得高于目标 (64 ms) [17] 的保留时间。但由于未优化的编程条件,当前读“1”与读“0”的比值和RT并不是最佳值。

TFET DRAM的性能,尤其是读“1”与读“0”的电流比,对编程条件有很大的依赖性。 Gate2主要影响写操作时的BTBT,它支配着Gate2下方电荷和势阱的存储区域。 Gate1在读操作时管控BTBT,主要影响读“1”电流。 Gate1 和 Gate2 的适当偏置可以使 DGTFET DRAM 获得更高的电流比。研究编程条件对阅读电流的影响的文献很少。在本文中,提出了详细的编程优化指南,包括写入、保持和读取操作。通过应用优化的编程条件,DG-TFET DRAM获得最佳性能——读取电流比高达10 7 和超过 2 秒的 RT。并施加优化的编程电压,读数“0”电流远低于参考文献[16, 18]报道的值,有助于降低功耗。

方法

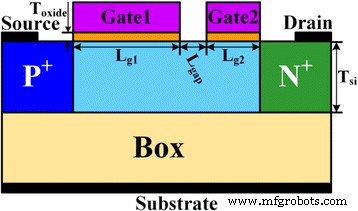

本文研究的 DG-TFET 结构如图 1 所示。 P + 的掺杂浓度 源和 N + 排水管为 1 × 10 20 /cm 3 .本征通道分为两段:Gate1 和Gate 2,Gate1 和Gate2 之间有一个短间隙。 Gate1 和 Gate2 是 N + 多晶硅和 P + 多晶硅,分别。 P + 多晶硅 Gate2 可以创建和维护用于电荷存储的物理阱,并取代使用 P + 的传统基于 TFET 的 DRAM 口袋区域作为存储区域。而对于 N + 多晶硅Gate1,Gate1和Gate2之间的underlap区域空穴浓度低,有利于读操作。因此,一个 P + 选择多晶硅 Gate2 具有更深的存储区域,可以促进更长时间的保留,而 N + 选择多晶硅Gate1来控制读取操作期间的隧穿机制[18]。

<图片>

DG-TFET DRAM 单元示意图。此图显示了双栅极 TFET (DGTFET) DRAM 单元的示意图,包括 Gate1、Gate2、源极、漏极和通道。在本设计中,源区和漏区为 P + 掺杂和 N + 分别掺杂。 Gate1 和 Gate2 是 N + 多晶硅和 P + 多晶硅,分别

模拟中的详细器件参数如下:体硅的厚度(T si) 是 20 纳米; Gate1 (Lg1) 和 Gate2 (Lg2) 的长度分别为 400 nm 和 200 nm;间隙长度 (L Gate1 和 Gate2 之间的间隙)为 50 纳米;栅氧化层厚度 (HfO2) (T 氧化物)为 3 纳米。优化后的编程条件如表1所示。编程条件的优化指导将在后面的章节中详细讨论。

所有的分析都是在 Silvaco-Atlas 工具中使用 Nonlocal BTBT 模型进行的 [19]。 Nonlocal BTBT 考虑了电子和空穴的非局部生成,因此可以更准确地模拟隧道过程。隧道模型参数根据参考文献[20]中的实验数据进行标定。此外,还使用了包括 Shockley-Read-Hall 复合、费米统计以及掺杂和电场相关迁移率在内的物理模型。根据 [16, 18] 的方法,电子和空穴的寿命设置为 100 ns。默认温度为 300 K。

结果与讨论

DG-TFET DRAM 单元的工作原理与传统 DRAM 不同。写操作和读操作都是基于BTBT,但各自的功能不同。写“1”时的BTBT导致空穴储存在Gate2下方的势阱中,可以提升读“1”的电流。在读操作过程中,漏电流主要取决于源端附近的BTBT。此外,两个门还扮演着不同的角色:Gate1和Gate2分别主要决定读操作和写操作。

写操作

在写“1”时,负偏压的Gate2将提升Gate2下方沟道的能带,从而减小势垒宽度并在沟道和漏极之间产生BTBT。而这种负的 Gate2 偏置也在 Gate2 下方诱发了一个深势阱。由于电子从沟道到漏极的隧穿,Gate2 下方的沟道区完全耗尽,并且在该势阱中积累了大量空穴。在写“0”期间,Gate2 的正偏压使空穴从势阱中排出,势阱在漏极侧复合[21]。

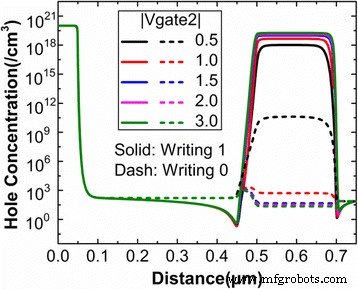

一般来说,写“1”和写“0”时Gate2电压的绝对值保持不变。图2显示了写操作后空穴浓度随Gate2电压的变化。当 Gate2 电压为 0.5 V 时,由于存在势阱,写入“0”后的空穴浓度较高,这对状态“0”不利。当 Gate2 电压的绝对值高于 1 V 时,写入“0”和写入“1”后的空穴浓度没有明显变化。这表明BTBT在写“1”时饱和,写“1”期间所有累积的空穴在写“0”后从势阱中排出。并且写“1”和写“0”的空穴浓度差异非常明显,有利于区分状态“1”和状态“0”。

<图片>

写入操作后通道表面的空穴浓度。该图显示了空穴浓度随不同 Gate2 电压的变化。切割线取自器件表面,从源极区到漏极区。图中实线和虚线分别代表写“1”和“0”后的空穴浓度

但是写操作期间的Gate2偏置不能仅由空穴浓度决定。图 3 表明写操作期间的 Gate2 偏置对保持操作后的漏极电流有显着影响。保持操作期间的编程电压设置将在下一节讨论。图 3 显示,当写电压的绝对值高于 1.3 V 时,保持操作后的漏极电流没有明显变化。因此,-1.3 和 1.3 V 被认为是写“1”期间的最佳 Gate2 电压,分别写“0”。

<图片>

保持“0”和保持“1”后DG-TFET的漏极电流。此图显示了保持“0”和保持“1”后漏极电流相对于写入电压的变化

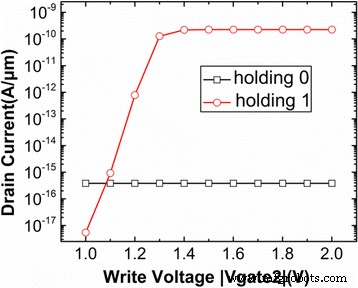

图4a、b分别表示写入电压绝对值为1.3V时写入“1”和写入“0”后的电位等值线。显然,写入后在Gate2下方的沟道区产生了一个非常深的势阱“ 1”,如图 4a 所示。在写入“1”期间,累积的空穴被保留在该势阱中。然而,在写入“0”期间,累积的空穴从该势阱中逸出。

<图片>

a 之后的潜在轮廓 写“1”和b 当 Gate2 电压的绝对值为 1.3 V 时写入“0”。a , b 分别写入“1”和“0”后的电位轮廓。当Gate2电压的绝对值设置为1.3 V时,提取了该图中的电位轮廓

持仓操作

持有过程主要用于修改费用的保留。通常,在保持操作期间使用零偏压以降低功耗[22]。在保持操作过程中,由于势阱深度的减小,势阱中积累的空穴逐渐复合。因此,保持操作优化的主要目的是避免保持“1”时孔的复合。在这个设计中,在Gate2处施加一个小的负偏压以在保持“1”后保持势阱中的空穴,而保持“0”后势阱中的空穴被耗尽。

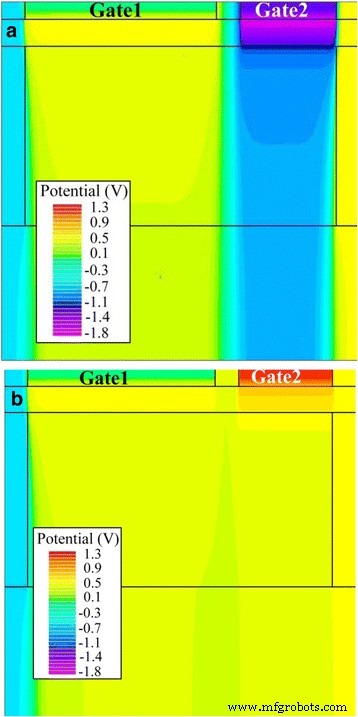

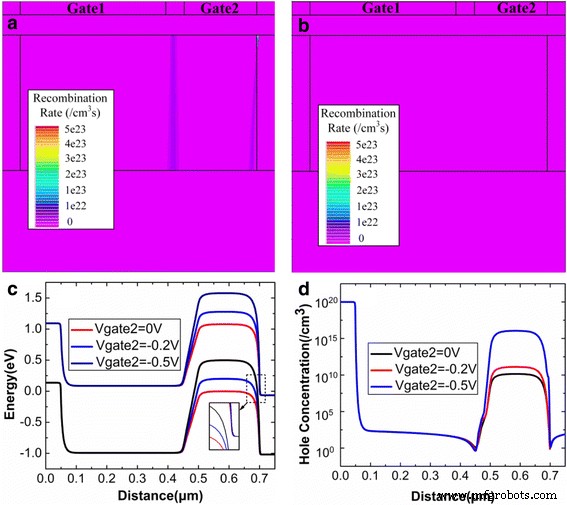

在保持操作期间,随着更负的 Gate2 电压(-0.5 V),保持“1”后空穴的复合被消除,如图 5a、b 所示。孔复合的消除有利于保持“1”时孔的保留。在 Gate2 处施加一个小的负偏压,以提高势阱深度并长时间保留空穴,这有利于 DGTFET DRAM 的保留时间。在保持“0”期间,负的 Gate2 偏置可以拉高 Gate2 下方的沟道区的能带,这可以防止来自源极和沟道之间的 BTBT 的电子流向漏极侧。因此,Gate2 为负值可以减少读取“0”电流。然而,具有更多负电压 (-0.5 V) 的 Gate2 减少了漏极侧附近的隧道距离,如图 5c 所示。这种减小的隧穿距离导致在保持“0”期间靠近漏极侧的 BTBT,这促进了保持“0”期间势阱中空穴的积累,如图 5d 所示。因此,在保持“0”期间更负的 Gate2 电压 (-0.5 V) 会使状态“0”退化。因此,为了分别消除保持“1”和保持“0”期间的空穴复合和BTBT,-0.2 V被认为是保持操作期间的最佳Gate2偏置。

<图片>

当 Gate2 电压为 a 时,保持“1”后 DG-TFET DRAM 单元中的复合率 0 V 和 b −0.5 V; c 能带图和d 保持“0”后的空穴浓度。 一 , b 当 Gate2 电压分别设置为 0 V 和 -0.5 V 时,保持“1”后的复合率。 c 从源区到漏区的器件能带。 d 打孔“0”后器件的空穴浓度。在栅极氧化层下方 3 nm 处提取能带和空穴浓度

阅读操作

随后,还研究了读取操作的优化。读取操作强烈依赖P + 之间的BTBT 来源和渠道。在读“1”时,Gate1主要促进源极侧的BTBT,而高电压的Gate2降低了阻止电子从沟道流向漏极的能垒。但是在读“0”时,需要小电压的Gate2能够阻止电子从沟道流向漏极。因此,Gate1和Gate2电压的优化对于读取操作非常重要。

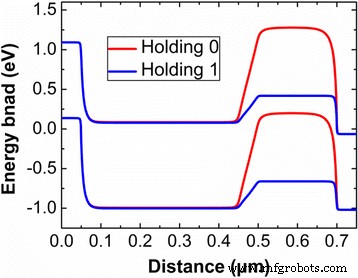

图6显示了保持“1”和保持“0”后的不同能带图。在读取“1”和读取“0”期间,在栅极侧施加相同的电压。由于在读取操作期间将使用正栅极偏置,因此每当读取“1”或“0”时,能量带将被放下。 Gate2下的通道在保持“0”后的能带比保持“1”后高,而且这个能带在读“0”时也比读“1”时高。 Gate2下方的沟道能量较高,会形成有效的势垒来阻止电子流向漏极侧,从而降低读取“0”电流。

<图片>

a 之后的能带图 拿着“1”和b 持有“0”。 一 , b 分别保持“1”和“0”后器件的能带。在栅极氧化物下方 3 nm 处提取能带

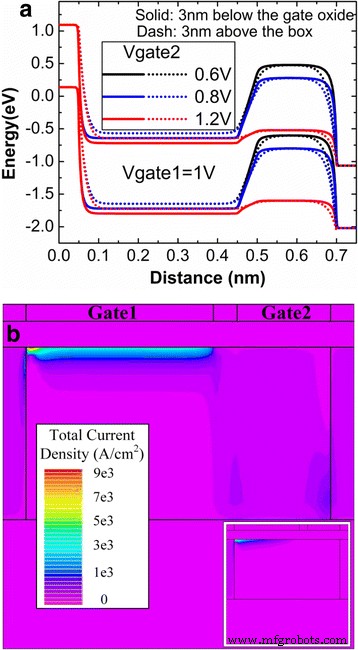

在读取操作期间,漏极偏置设置为 1 V,以便可以在 DG-TFET 中读取漏极电流。首先,保持 Gate1 电压为 1 V,改变 Gate2 的偏置以选择最佳 Gate2 电压。由于Gate2电压主要影响读“0”电流,因此通过读“0”机制分析Gate2电压的优化。图 7a 绘制了读取“0”后能带随 Gate2 电压的变化。当 Gate2 电压较低(0.6 或 0.8 V)时,Gate2 下的通道会完全耗尽。但当 Gate2 电压升至 1.2 V 时,Gate2 下方的沟道下拉能带无法形成有效势垒来阻止电子流向漏极侧。图 7b 及其插图分别显示了当 Gate2 电压为 1V 和 0.8V 时读取“0”后的总电流密度。当 Gate2 电压为 1V 时,在 Gate2 下方的沟道区可以清楚地发现明显的电流密度,这将产生更高的读数“0”电流。所以0.8 V被认为是读取过程的最佳Gate2电压。

<图片>

一 能带图和b 读取“0”后的总电流密度。 一 , b 分别为读“0”后的能带和总电流密度。在栅极氧化物下方 3 nm 处提取能带

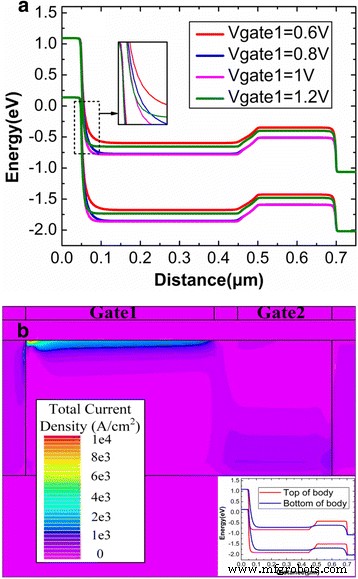

最后,还进行了 Gate1 偏置的优化。图 8a 显示了顶部能带随 Gate1 电压的变化。源极侧的BTBT势垒宽度随着Gate1电压的增加而逐渐减小,但是当Gate1电压高于1V时这种减小趋势开始饱和。而1V的Gate1电压不会对读取“0”带来严重影响”操作,这已由图 7b 证明。因此,在读取操作期间,1 V 被认为是最佳的 Gate1 偏置。

<图片>

一 能带图和b 读“1”后的总电流密度。 一 , b 分别为读“1”后的能带和总电流密度。在栅极氧化物下方 3 nm 处提取能带

通过以上分析,深位势阱仅在写“1”后形成在Gate2下方的沟道顶部。因此,在 Gate2 下方的沟道区中,沟道顶部的能带远高于沟道底部的能带。这表明在读取“1”期间,Gate2 下方的通道顶部将有一个障碍。图 8b 的插图绘制了读取“1”后通道顶部和底部的能带。可以清楚地发现,在通道顶部的Gate1和Gate2之间存在更高的通道势垒,而在通道底部不存在该势垒。因此,在读取“1”时,导通路径在Gate1下方的沟道顶部和Gate2下方的沟道底部,这可以通过图8中的电流密度清楚地证明。

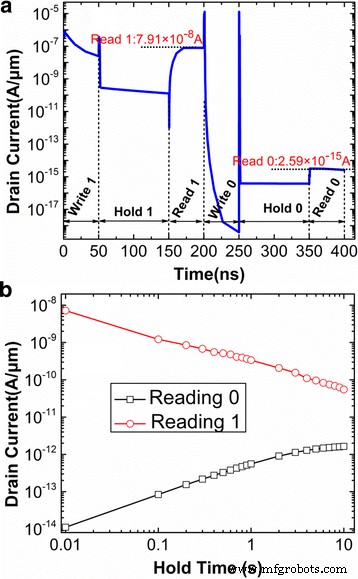

应用上述优化的编程条件,DG-TFET DRAM 单元的瞬态响应如图 9 所示。写入和读取时间均设置为 50 ns,保持时间设置为 100 ns。在图9a中,读“1”与读“0”的电流比高达10 7 ,远高于 10 2 ~10 3 在参考文献 [16, 18, 23] 中。此外,当保持时间增加到10 s时,电流比仍然超过10。在参考文献[16]中,当保持时间增加到2 s时,电流比只有10左右。因此,DG-TFET的RT具有优化编程条件的 DRAM 高于 2 秒。因此,优化的编程条件使DG-TFET DRAM单元不仅获得更高的读取电流比,而且获得更大的RT。更重要的是,优化编程电压的读数“0”电流比参考文献[16,18,22,23]中的要小得多,使其能够满足低功耗应用。

<图片>

一 操作顺序中的瞬态漏极电流; b 读取电流随保持时间的变化。 一 DGTFET DRAM 单元在写入、保持和读取操作期间的瞬态电流。 b 不同开孔时间读“1”和读“0”电流的变化

结论

本文使用 Silvaco-Atlas 仿真工具提出了详细的 DG-TFET DRAM 编程条件优化指南。在写入“1”期间,负电压(-1.3 V)的 Gate2 产生一个势阱,沟道和漏极之间的 BTBT 使空穴在该势阱中积累。在写入“0”期间,具有正电压 (1.3 V) 的 Gate2 使空穴从势阱中逸出。对于保持操作,在 Gate2 处施加小的负电压 (-0.2 V) 以保留空穴,这可以改善读取“1”电流。保持“0”后,Gate2下方的沟道势垒可以阻止电子流向漏极侧,从而减少读取“0”电流。为了优化读取操作,较大的Gate1电压(1V)主要用于在读取“1”时增强源极侧的BTBT,而适当的Gate2电压(0.8V)用于在读取过程中阻止电子流向漏极“0”。优化的编程条件使 DG-TFET DRAM 获得更高的电流比 (10 7 ) 读取“1”到读取“0”并且保留时间超过 2 秒。极低的读数“0”电流有助于降低功耗。

纳米材料