基于双栅极隧道晶体管的无电容 DRAM 间隔工程优化

摘要

基于双栅隧道场效应管(DGTFET)的DRAM具有无电容结构和高保留时间的优点。在本文中,Silvaco-Atlas 工具系统地研究了 DGTFET DRAM 的垫片工程优化,以进一步提高其性能,包括减少读取“0”电流和延长保留时间。仿真结果表明,源极侧和漏极侧的间隔物应分别应用低k和高k电介质,这可以增强读取“1”电流并降低读取“0”电流。应用这种优化的垫片工程,DGTFET DRAM 获得了最佳性能——极低的读取“0”电流(10 -14 A/μm)和较长的保留时间(10s),降低了其静态功耗和动态刷新率。而低读数“0”电流也提高了其电流比(10 7 ) 读取“1”到读取“0”。此外,对可扩展性的分析揭示了其固有的缺点,为DGTFET DRAM提供了进一步的研究方向。

背景

随着器件几何尺寸的缩小,1 个晶体管 (1T)–1 个电容器 (1C) 的动态随机存取存储器 (DRAM) 遇到了按比例缩小的困难,因为电容器很难减小其尺寸 [1,2,3] .存储器行业已经提出了一些用于更高密度存储器封装的有效方法,例如新材料和新器件结构[4, 5]。无电容结构的1T DRAM于90年代初首次报道[6, 7],受到越来越多的关注。在 1T DRAM 中,状态 1(载流子存储)通过四种方式实现:碰撞电离 [8]、双极结型晶体管 [9]、带间隧道 (BTBT) [10] 和栅极隧道 [11]。

由于更高的开关比和极低的关断电流,基于 BTBT 的隧道场效应晶体管 (TFET) 已被视为 MOSFET 的潜在替代品 [12,13,14]。 TFET 的优势——低断态电流和弱温度依赖性——对 DRAM 非常有利。尤其是低断态电流可以降低读“0”电流和静态功耗。目前,有一些小组正在研究 TFET DRAM [15,16,17,18,19,20]。据悉,TFET DRAM具有低读取“0”电流和高保留时间(RT)。在这些 TFET DRAM 中,双栅极 TFET (DGTFET) DRAM 最为突出 [19, 20]。在 DGTFET DRAM 中,写入和读取操作均基于 BTBT。研究表明,DGTFET DRAM 的读取“0”电流可达 1 nA/μm,远低于传统 1T1C DRAM。并且 2 s 的 RT 远优于 64 ms 的目标值,64 ms 通常在计算系统中设置为动态刷新时间 [21]。当温度升高到 85°C 时,DGTFET DRAM 的 RT 仍然大于 300 ms,这证明了其在恶劣条件下的实用性。此外,在DGTFET DRAM中,取消更大尺寸的电容器也展示了其在高密度封装方面的竞争力。这些优势充分说明有必要研究DGTFET DRAM。虽然这些研究已经证明DGTFET比传统的1T1C DRAM具有更优越的性能,但由于DGTFET的器件配置没有优化,结果(RT和读取“0”电流)并不是最佳的。

本文对DGTFET的spacer工程进行优化,使DGTFET获得最佳性能。在 TFET 中,间隔电介质对 BTBT 有很大影响 [22, 23]。在 DGTFET 中,源极和漏极侧的间隔物对隧道结是封闭的,因此它们极大地影响了 DGTFET DRAM 的性能。本文系统地分析了每个隔板中的隔板电介质(低k或高k电介质)对DGTFET DRAM的影响,并提出了优化的隔板工程。通过垫片工程的优化,将读数“0”电流压低至10 -14 A/μm,RT 可达 10 秒。最后,本文还讨论了优化间隔工程的 DGTFET DRAM 的可扩展性。

设备结构及仿真方法

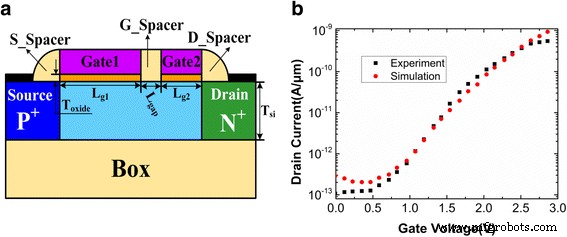

具有 P-I-N 配置的 DGTFET 如图 1a 所示。源漏区为P + 兴奋剂 (10 20 /cm 3 ) 和 N + 兴奋剂 (10 20 /cm 3 ), 分别。本征沟道区分为两部分: Gate1 区与 N + 具有 P + 的多晶硅和 Gate2 区域 多晶硅。 Gate1 和 Gate2 之间有一个短暂的间隙。 P + 多晶硅 Gate2 可以创建和维护用于电荷存储的物理阱,并取代使用 P + 的传统基于 TFET 的 DRAM 口袋区域作为存储区域。而对于 N + 多晶硅Gate1,Gate1和Gate2之间的underlap区域空穴浓度低,有利于读操作。因此,一个 P + 多晶硅 Gate2 选择创建一个更深的存储区域,可以促进更长的保留时间,而 N + 选择多晶硅 Gate1 来控制读取操作期间的隧道机制 [20]。在图 1a 中,S_Spacer 和 D_Spacer 分别是指源极和漏极侧的隔离物。 G_spacer 是指 Gate1 和 Gate2 之间的隔板。垫片的默认材料为 SiO2。默认器件参数如下:硅膜厚度 (Tsi) 为 20 nm,Gate1 长度 (Lg1) 为 400 nm,Gate2 长度 (Lg2) 为 200 nm,栅极间隙长度 (Lgap)为 50 nm,栅极氧化物 HfO2 (Toxide) 的厚度为 3 nm。

<图片>

一 双栅极 TFET (DGTFET) DRAM 单元的示意图。 b SOI TFET的模拟传输特性与实验结果的比较[25]

DGTFET DRAM 的模拟是在 Silvaco Atlas 中使用非本地 BTBT 模型进行的。非局部 BTBT 隧道模型考虑了能带的空间变化和相反载流子类型的产生/复合 [24]。隧道模型的参数根据SOI TFET的实验结果进行校准[25]。电子和空穴隧道质量分别调整为 0.22m0 和 0.52m0,其中 m0 是电子的静止质量。 SOI TFET 的模拟传输特性与实验结果一致,如图 1b 所示,验证了本文中应用的模型。由于源漏区的重掺杂,还考虑了带隙变窄模型和 Fermi-Dirac 统计。此外,还应用了 Shockley-Read-Hall 复合以及掺杂和电场相关迁移率模型。所有模型参数与[19, 20]中的参数一致。因为载流子寿命在保持操作期间控制载流子的生成/复合,所以它会影响 DGTFTET DRAM 的 RT。根据 [26,27,28] 中在 1 μs 和 10 ns 之间变化的不同载流子寿命,电子和空穴寿命设置为 100 ns。 Scharfetter 关系和 Schenk 模型分别包括掺杂和寿命的温度依赖性。

结果与讨论

运行机制

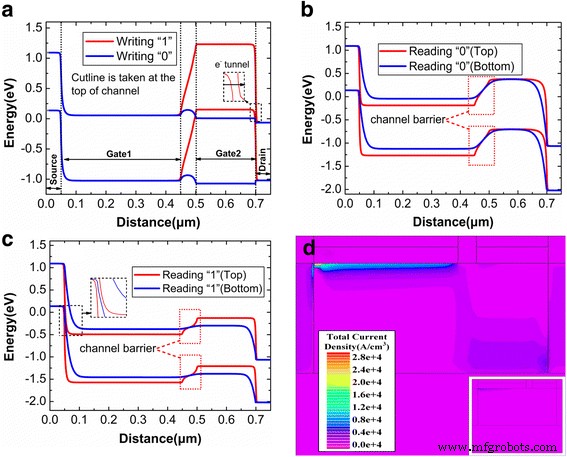

在 DGTFET DRAM 中,写入和读取操作分别由漏极和源极隧道结处的 BTBT 控制。图 2 显示了不同操作期间的能带。如图 2a 所示,在写入“1”期间,具有负偏压的 Gate2 显着提升了 Gate2 下方的沟道能带,从而在漏极侧产生了极小的隧道势垒。因此,电子向漏极侧隧穿,空穴累积到深势阱 (1.2 V) 中,如图 3a 所示。在写入“0”期间,具有正偏置的 Gate2 使空穴从该势阱中排出并在漏极侧重新组合 [29]。图 2b、c 分别显示了读取“1”和“0”后的能带。图 2b 说明 Gate1 和 Gate2 之间存在通道屏障,但在通道底部不存在。此外,通道顶部源侧的隧穿距离更小。这表明在读取“1”期间形成了倾斜的传导路径(从 Gate1 的前界面到 Gate2 的后界面),这也可以通过图 2d 的电流密度来证明。在读取“0”期间,可以在图 2c 中发现明显的沟道势垒,这抑制了读取“0”电流。图2d的插图表明从源区隧穿的电子不能穿过该沟道势垒形成更高的读数“0”电流。

<图片>

从源极到漏极的能带。 一 使用负 Gate2 偏置写入“1”后和使用正 Gate2 偏置写入“0”后的能带。 b 读取“1”后通道顶部和底部的能带。 c 读取“0”后通道顶部和底部的能带。 d 读“1”后的总电流密度

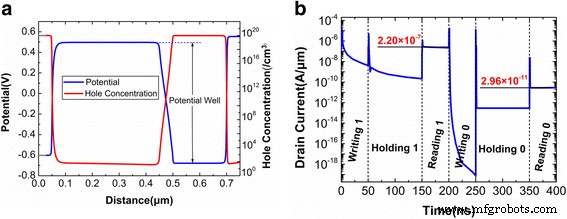

<图片>

一 写入“1”后沟道表面的电位和空穴浓度。 b DGTFET DRAM的漏极电流瞬态响应见表1

适当的编程条件对于 DGTFET DRAM 很重要。应在 Gate2 处施加更大的负偏压,以便在写入“1”期间感应饱和 BTBT。在保持“1”期间,在 Gate2 处施加一个小的负偏压以长时间保留势阱中的空穴。对于读取操作,较高的 Gate1 偏置会在读取“1”期间加强 BTBT,但不利于读取“0”电流。适当偏置的Gate2不仅可以增强读数“1”电流,还可以减弱读数“0”电流。应用表 1 中优化的编程条件,具有默认参数的 DGTFET DRAM 的瞬态响应如图 3b 所示。写入和读取以及保持时间分别设置为 50 ns 和 100 ns。得到的读“1”与读“0”的电流比约为10 4 , 与 [17, 19, 20] 相同。

间隔电介质的影响

在 DGTFET DRAM 中,在三个垫片(S_Spacer、G_Spacer 和 D_Spacer)中使用低 k 或高 k 电介质将影响其性能。在此设计中,低 k 和高 k 电介质分别选择 SiO2 和 HfO2。如果每个垫片都使用 SiO2 或 HfO2,则总共有八种垫片工程组合。为了更全面的分析,每种组合的 DGTFET DRAM 的性能属性,包括读取“1”(I 1) 和“0”(I 0) 电流以及电流比 (I 1/ 我 0),从瞬态响应中提取,如表 2 所示。为了评估 RT,当保持时间增加到 2 秒时,这些参数也被提取,这将在以下部分讨论。表2中字母“S”和“H”分别代表SiO2和HfO2,每个缩写的三个字母分别代表S_Spacer、G_Spacer和D_Spacer。

从表 2 中,可以选择最佳的垫片工程。 我 1 大约是 10 −7 A/μm 和 10 −9 S_Spacer 中分别使用 SiO2 和 HfO2 时的 A/μm。当 D_Spacer 应用 HfO2 时,I 0 低到大约 10 −14 A/微米。因此,DGTFET DRAM 的最佳间隔配置是在源极和漏极侧应使用低 k 和高 k 电介质。具体原因将在以下部分进行系统分析。

S_Spacer Dielectric 的影响

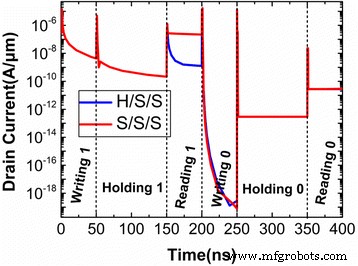

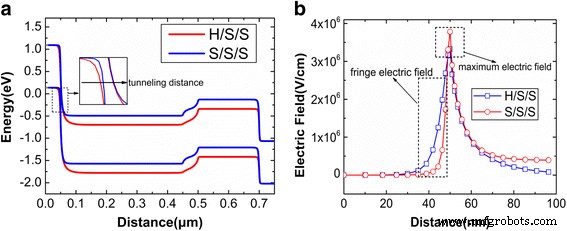

为了分析 S_Spacer 的影响,图 4 比较了 H/S/S 和 S/S/S 漏极电流的瞬态响应。可以观察到,读数“1”电流提高了约 2选择SiO2作为S_Spacer电介质时的数量级。

<图片>

表1中H/S/S和S/S/S的漏极电流瞬态响应

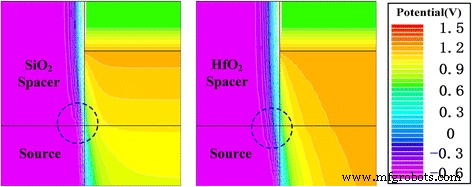

图 5 显示了 S/S/S 和 H/S/S 的潜在轮廓。在源极隧穿结处,H/S/S 的表面耗尽区较 S/S/S 明显扩展,如图 5 中圆圈所示。扩展的表面耗尽区增加了隧穿势垒宽度。图 6a 显示了读取“1”后的能带。如图中局部放大区域所示,H/S/S 的隧穿距离(见箭头)明显大于 S/S/S,这是由扩展的表面耗尽区引起的。此外,读取“1”后,源隧道结顶部的电场如图6b所示。可以发现H/S/S的边缘电场大于S/S/S的边缘电场,这是表面耗尽区扩展的主要原因。总之,具有高k(HfO2)电介质的S_Spacer产生更大的边缘电场,使源极隧穿结的表面耗尽区扩大,从而增加了电子的隧穿距离并降低了读数“1”电流。此外,从图 6b 还可以发现,S/S/S 的最大电场大于 H/S/S 的最大电场。 BTBT 速率与电场之间的指数关系使得 S/S/S 的隧道电流远大于 H/S/S [30]。因此,具有低k电介质(SiO2)的S_Spacer有利于读取“1”电流。

<图片>

读“1”后S/S/S(左)和H/S/S(右)的潜在轮廓

<图片>

一 从源极到漏极和 b 的能带 源隧穿结顶部电场

在图 6a 中,S_Spacer 电介质也带来了对沟道区能带的影响。在图 6b 中,S/S/S 的电场在沟道区较大,因此其沟道电位小于 H/S/S。因此,可以在 S/S/S 中找到更高的能级。但这不会对隧道势垒和读取“1”电流产生影响。

D_Spacer Dielectric 的影响

随后,本文还研究了 D_Spacer。保持恒定的 S_Spacer 和 G_Spacer(这两个 Spacer 中使用 SiO2),由不同的 D_Spacer 电介质引起的不同瞬态漏极电流如图 7 所示。除了读“1”和写“0”外,其他操作对 D_Spacer 电介质有明显的依赖性。这是因为 D_Spacer 远离读取“1”传导路径(Gate2 下方的通道底部)。由前面的操作机制可知,写和保持操作是由Gate2控制的,因此D_Spacer电介质会对这两个操作带来影响。

<图片>

S/S/H和S/S/S的漏极电流瞬态响应见表1

在保持操作期间,在写入“1”期间积累的空穴从势阱中移除并在漏极侧重新组合。所以保持“1”电流主要来自SRH复合电流。由于S/S/S 中Gate2 对通道的可控性更强,因此S/S/S 具有更大的复合率和保持“1”电流。但在读“1”时比BTBT电流小很多,所以较高的保持“1”电流不能反映在读“1”电流上。

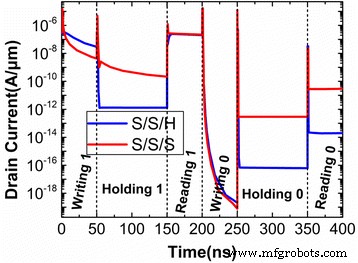

在写入“1”期间,D_Spacer 电介质显着影响势阱深度。图 8a 中的电位等值线表明,带有 HfO2 电介质的 D_Spacer 创建了一个更深的势阱。这意味着漏极和沟道之间的有效 BTBT 扩展到更深的沟道区域。因此,S/S/H的写“1”电流要高于S/S/S。在保持“0”期间,虽然在 Gate2 上施加了一个小的负偏压(- 0.2 V),但它也可以在 Gate2 下建立通道的能带,从而在漏极侧感应出 BTBT。通过前面的分析可以了解到,在保持“0”期间,带有 SiO2 电介质的 D_Spacer 增强了漏极隧道结处的 BTBT,这可以通过 S/S/S 的更高空穴浓度来证明,如图 8b 所示.因此,带有SiO2电介质的D_Spacer导致更高的保持“0”电流。

<图片>

一 写入“1”后的电位轮廓。 b 保持“0”后的空穴浓度

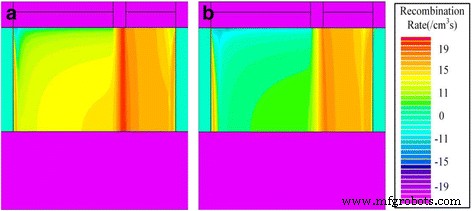

在读“0”时,由于Gate1和Gate2之间的沟道势垒阻止了电子流向漏极侧,S/S/H和S/S/S读“0”电流的差异主要是由复合电流引起的. S/S/S在保持“0”时积累的空穴越多,所以下降的能带使得S/S/S在读“0”时的复合率大于S/H/S的复合率,如图在图 9. 因此,当 D_Spacer 使用 SiO2 时,较高的读取“0”电流应归因于较高的复合电流,这是由于保持“0”期间积累的空穴越多。

<图片>

a的重组率 S/S/S 和 b 读“0”后的 S/S/H

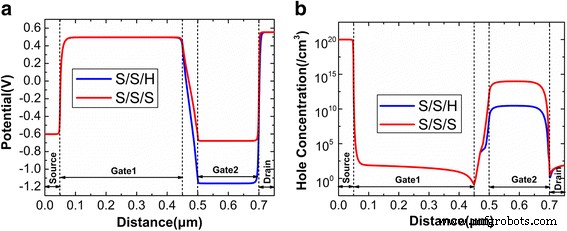

总而言之,DGTFET DRAM 的最佳隔离器工程是源极和漏极侧的隔离器应分别应用低 k 和高 k 电介质。从表2可以看出,G_Spacer在其他spacer不变的情况下对DGTFET DRAM没有影响。这是因为主导读写操作的BTBT不受G_Spacer的影响。

保留时间

如前所述,保持“1”和“0”期间的空穴复合和产生分别使状态“1”和“0”退化。因此,有必要研究DGTFET DRAM在较长保持时间下的性能下降。在表 2 中,I 1 和 I 0随着保持时间的增加而大大降低。在所有设备中,I 1/我 0 仍然大于 10 4 当保持时间上升到 2 秒时,具有最佳间隔工程(S/S/H 和 S/H/H)的器件。

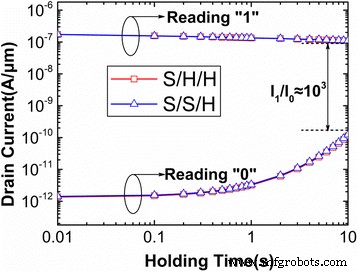

通常,减少最大检测裕量所需的保持时间(I 1 和 I 0) 50% 被评估为 RT。在这个设计中,一个更严格的 RT 被定义为当 I 1/我 0 高于 10 3 .图 10 显示了 S/S/H 和 S/H/H 的读取电流随保持时间的变化。可以发现S/H/S和S/H/H的流动比率高达10 3 当保持时间上升到 10 秒时。因此,具有最佳间隔工程的 DGTFET DRAM 的 RT 可以达到 10 秒。这远高于 64 毫秒的目标值。表 3 比较了这项工作与 [17,18,19,20] 中的性能属性。在[19, 20]中,流动比率只有10 2 ,并且 RT 远小于 10 秒。此外,这项工作中的读数“0”电流比 [19, 20] 中的低两个数量级。 FD-SOI TFET DRAM的实验结果也表明,它们的读取“0”电流和RT都比本工作差。这种优越的性能表明 DGTFET 是低功耗 DRAM 的替代品。间隔工程的优化使DGTFET DRAM获得低读“0”电流和高RT,有助于降低静态和动态功耗。

<图片>

读数电流随S/S/H和S/H/H保持时间的变化

DGTFET DRAM 的可扩展性

虽然 DGTFET DRAM 解决了由于消除大尺寸电容器导致的存储单元密度问题,但有必要研究其可扩展性。可扩展性的目标是保持 RT 高于 2 秒。表 4 提取了随 L 减小的 S/S/H 性能特性 g1, L g2 和 L 差距。表4中每个缩写的三个数字代表L g1, L 间隙和 L g2.

从表 4 可以看出,I 当 Lg1 从 200 nm 减小到 100 nm 时,1 会显着降低。 Lg1 超过 100 nm 的缩放缩小了 n 型诱导势垒,导致栅极可控性降低和 I 退化 1. 我 0随着L的减小而显着增加 g1 和 L g2. L 的减少 g2 减小了 Gate1 和 Gate2 之间的沟道势垒宽度,促使部分电子越过势垒形成更高的 I 0.另外,L的不断缩小 g1减弱了Gate1在读“0”时限制沟道表面隧穿电子的能力。在表 4 中,L gap 对 I 没有明显影响 1,但是 I 0 随着 L 的减小而略有增加 差距。减少 L 低于 20 nm 的间隙允许更高的隧道通向 Gate2,从而降低状态“0”,从而减少保留时间。

为了确保I 1/我 0 且保留时间大于 10 2 和 2 秒,分别是最小 L g1, L g2 和 L 间隙分别被视为 200、150 和 20 nm。该最小器件尺寸略小于 [17,18,19,20] 中的尺寸,如表 3 所示。但是,DGTFET DRAM 的最小尺寸仍然大于 20 nm/18 nm 节点 1T1C DRAM [31 ],这是DGTFET DRAM的固有缺点。但其无电容、低功耗、高RT等优势在隔板工程优化的帮助下也不容忽视。将 DGTFET DRAM 的尺寸缩小到 100 纳米以上将是我们未来工作的重点。

结论

在本文中,使用 Silvaco-Atlas 工具研究了 DGTFET DRAM 的垫片工程优化。源极和漏极侧的隔离物对 DGTFET DRAM 的性能有主要影响。带有 HfO2 的源极间隔物扩大的边缘电场使源极隧道结处的表面耗尽区扩展,从而降低了读取“1”电流。当 SiO2 电介质用于漏极隔离物时,更强的 BTBT 在保持“0”时会产生更多的空穴,从而增强读取“0”时的复合电流。因此,最佳的隔板工程是在漏和源隔板中分别使用低k和高k电介质。通过对垫片工程的优化,DGTFET DRAM与其他相关工作相比,获得了显着的优势——极低的读取“0”电流和更高的保留时间(10s)。此外,关于可扩展性的分析表明,其最小器件尺寸仍大于最新的 20 nm/18 nm node 1T1C DRAM。这一固有的缺点表明,将 DGTFET DRAM 的尺寸减小到 100 nm 以上将是我们未来 DGTFET DRAM 的工作重点。

缩写

- DGTFET:

-

双栅隧穿场效应晶体管

- DRAM:

-

动态随机存取存储器

纳米材料