FinFET Cu BEOL 工艺中等离子对金属间电介质的损伤的测试模式设计

摘要

由先进的 CMOS Cu BEOL 技术实现的高密度互连,可实现紧密放置的金属层。高纵横比金属线需要大量的等离子蚀刻工艺,这可能会导致金属间介电 (IMD) 层的可靠性问题。这项研究提出了新提出的测试模式,用于评估等离子体诱导充电效应对紧密放置的金属线之间 IMD 完整性的影响。发现并综合分析了等离子体充电强度与IMD层中发现的损伤之间的强相关性。

介绍

随着技术迁移到亚 100 nm 范围,基于铜的生产线后端 (BEOL) 工艺已被广泛使用。紧密封装的互连由高深宽比的通孔和金属线组成,这通过一系列等离子体增强蚀刻工艺 [1,2,3] 成为可能。众所周知,高能等离子体处理会导致晶体管栅极电介质堆栈的显着退化和潜在损坏,这被认为是工艺引起的充电事件期间的主要放电路径。为了防止栅极介电质量的可靠性问题,IC 制造商通常会提供设计人员规则和指南,以限制互连金属层的尺寸和长度 [4, 5]。随着复杂布线系统中金属层数量的增加,在工艺引起的充电过程中很难避免通过金属间介电膜的放电路径。随着在 BEOL 工艺中引入低 k 材料 [6, 7],缓解了恶化的 RC 延迟问题,隔离膜可能更容易受到充电应力的影响 [8, 9]。由等离子体充电引起的应力对负责实现复杂 BEOL 布线的紧凑互连结构造成的损坏会极大地影响先进 CMOS IC 的产量和可靠性。在这项研究中,我们结合了先前报道的原位 PID 记录器 [10,11,12],以及新提出的差分测试模式,用于在先进的 Cu BEOL 工艺下额外的放电路径成为可能时监测其可能的 IMD 损坏。通过新的测试模式,记录器在晶圆上不同位置报告的等离子体充电水平可以与 IMD 薄膜上的等离子体充电损坏相关联。然后可以通过这些测试模式轻松揭示 IMD 结构上的应力引起的故障行为,这些测试模式可用于标准测试结构中,用于对新故障模式和可能的 IMD 可靠性问题进行例行监控。

设备结构和方法

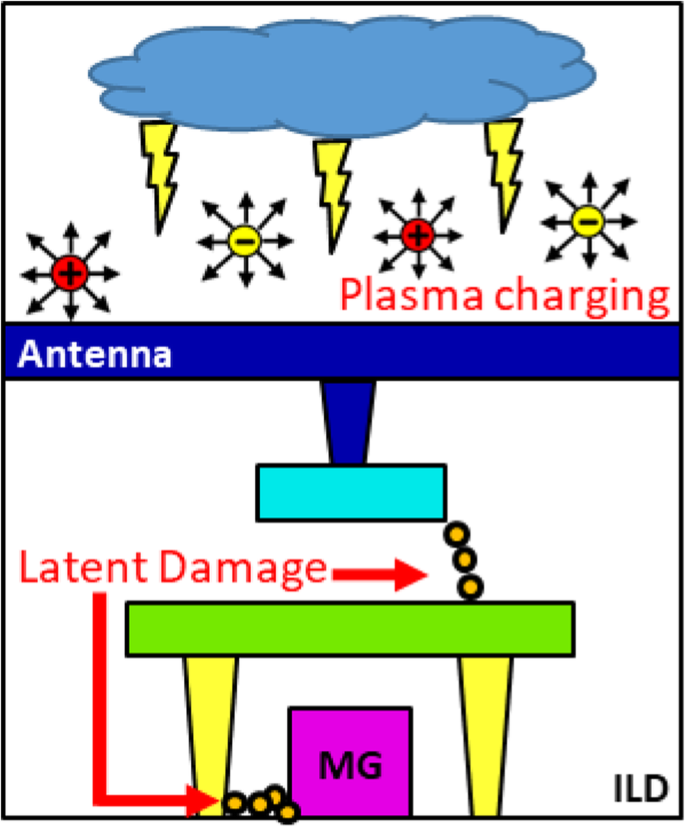

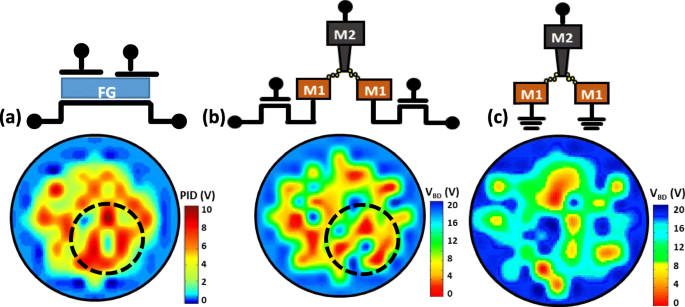

FinFET 集成电路的故障分析结果表明,两个紧密放置的隔离互连结构之间的金属间介电层内可能发生陷阱态增加的潜在损坏,如图 1 所示。作为通孔和金属互连之间的线宽和间距提前大幅减少 CMOS BEOL 工艺,在大金属线上收集的电荷用作天线,可能会通过 IMD 放电穿过金属和通孔/栅极和金属线,从而在这些介电薄膜上产生高场和/或高电流应力。通过将原位 PID 记录器 [10,11,12] 放置在每个芯片上的两个差分测试图案旁边,可以首先建立 12 英寸晶圆上的参考等离子体充电水平。

<图片>

紧密封装互连图案之间的金属间介电层中的等离子体引起的损坏可能与其隔离完整性的潜在退化有关

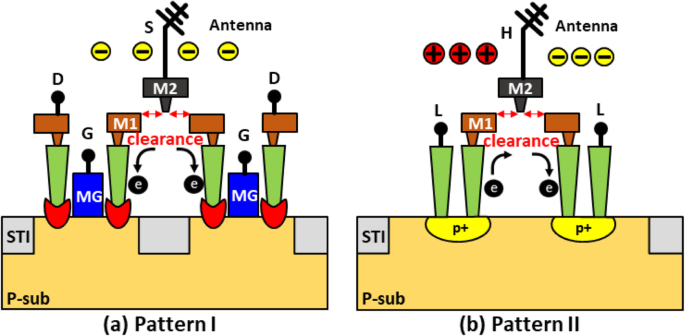

为了保证等离子充电电流通过金属层之间的介电层,在制作天线结构之前,对图2中测试图案上的M2节点进行隔离。两种新的差分测试图案设计旨在增加在等离子充电应力期间引起潜在损坏的可能性,并在图 2a、b 中进行了说明。具有 I 型模式的设备只会在其相应天线上收集电子时承受高电流应力。这是因为放电电流被导电通路上串联的 n+/p 结整流。而具有 II 型图案的器件在两个方向都受到应力 I [13]。即,离子充电和电子充电都将在此监控设备上注册。因此,本研究中的样品采用 16 nm 技术节点的标准 FinFET/Cu BEOL 工艺制造。 PID 记录器上的天线结构以及放置在每个管芯上的 I 型和 II 型图案的器件均采用大型金属 3 结构设计。两种类型的监测装置均采用差分配置设计,可以增强并随后最小化可能导致故障读数对 PID 影响的错位噪声。

<图片>

新提出的差分测试模式的插图,旨在强调由等离子体引起的 a 引起的潜在损伤的影响 否定和b 双向应力,其中金属层之间的间隙设置为 14 nm

实验结果与讨论

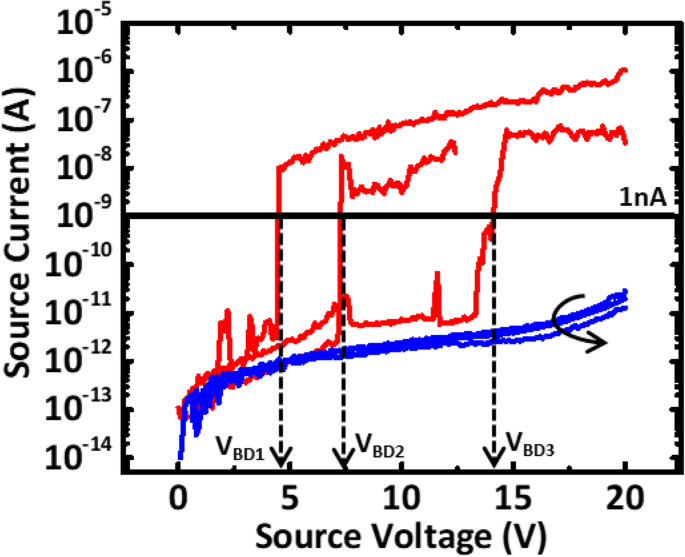

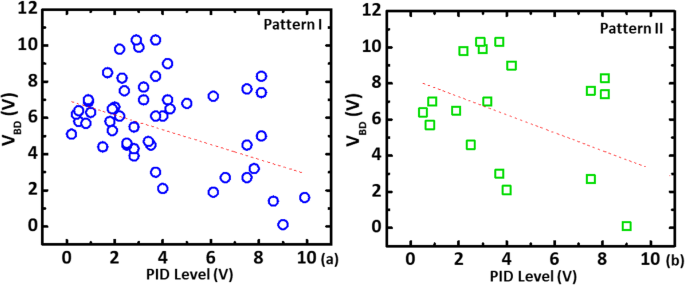

图 3 中的数据是通过以 0.7 V/sec 的扫描速率对金属 2 施加 0-20 V 的电压扫描获得的,而击穿电压和具有测试图案的几个不同器件两侧的 IMD 漏电流然后就可以得到 I 并进行比较。 82000μm大M3天线制作过程 2 ,预计等离子体工艺会引起天线充电。预计累积的电荷将通过电阻最低的通路放电。数据显示,一些样品表现出早期介电击穿,而其他器件上的 IMD 保持相对完整,泄漏率较低。

<图片>

在连接到 82,000 μm 金属 3 天线的差分测试模式设备上测量的泄漏电流 2 . V BD 定义为当通孔长度为 32 nm 时电流达到 1 nA 时的电压

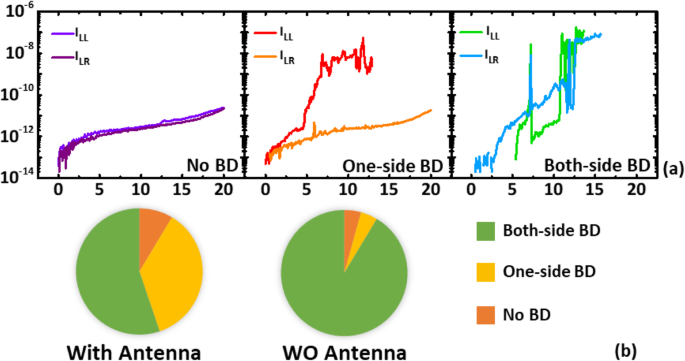

在充电事件中,预计较弱的一侧将服务于主导的放电路径,导致左右损坏程度的不平衡更加突出。因此,只有具有大 V 的设备 左右两侧的 BD 差异更有可能是由等离子充电引起的。因此,较小的 V 一对 IMD 故障中的 BD 被注册为与 PID 应力水平相关的水平。图 4a 显示了在晶圆上不同芯片上的样品上发现的三种典型特征。这些样本可分为任一侧无击穿、一侧击穿或两侧击穿组。显示每组特定特征的设备部分显示在图 4b 的饼图中。我们发现,在没有天线的样品上,单侧击穿特性的变化要小得多。在大多数未经历等离子充电应力的设备中发现了两侧的对称行为。这些进一步表明,差分对中的大部分不对称特性来自天线结构连接时的充电应力。

<图片>

一 晶圆和 b 上测试对的不同类型击穿特性 比较在超过 60 个芯片的器件对上表现出不同类型击穿特性的样品的百分比

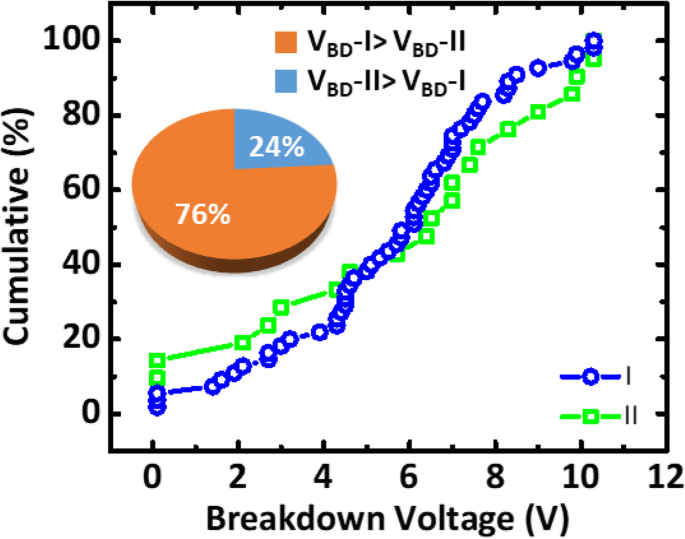

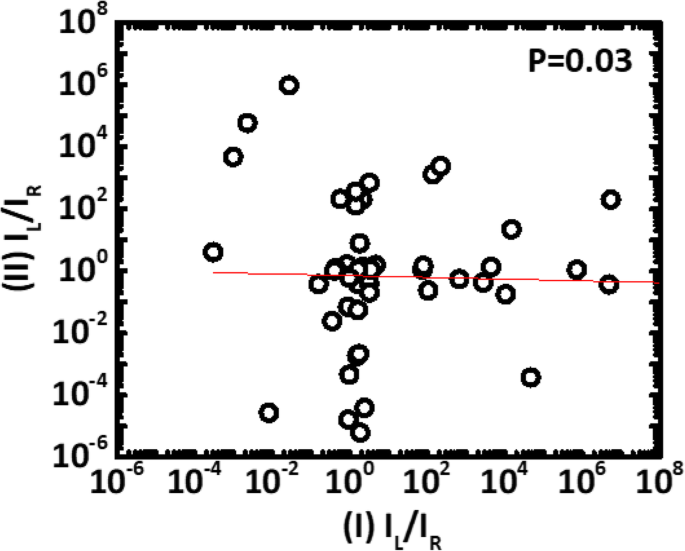

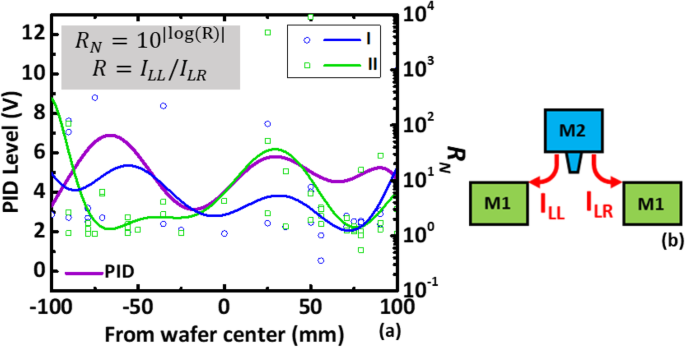

使用 V 上述方法得到的BD,PID电平和V的晶圆图 图 5 比较了 I 型和 II 型器件的 BD。V 的晶圆图之间的高度相似性 来自两种类型的监测设备的 BD 和相应的参考充电水平是从 PID 记录器获得的,见图 5a。 PID 电压被认为可以记录金属加工过程中的电子和离子充电事件 [14]。然而,发现晶片上的样品主要受到比离子充电更多的电子充电 [14]。我们认为在图 5a、b 中的晶片之间可以看到一些区域相关性。而图 5c 中的晶圆图来自模式 II,与图 5a 中的没有明显相似之处,表明双向应力 [15] 可能会导致对介电层的二次影响,这需要进一步研究。图 6 中比较新测试模式与参考 PID 电平的测量击穿电压进一步表明,芯片上的 PID 电平越高,其 V 越低 BD 新的测试模式。此外,V 之间显着负相关 可以建立 BD 和等离子充电水平。为了研究单向和双向应力对 IMD 损伤的影响,V 图 7 总结并比较了设计的 I 型和 II 型图案所测量的 BD。V 从跨晶圆的 60 个芯片上的器件获得的 BD 分布表明,经受双向充电应力的器件更可能在较低电压下显示出 IMD 击穿。这可以通过不对称应力水平来解释,因为跨 IMD 的极性发生变化 [16]。此外,在介电层上以 10 V 测量的应力引起的漏电流 (SILC) 是 IMD 膜内陷阱态 [17] 增加的另一个指标。为了进一步减少由工艺变化引起的die-to-die变化影响,每对漏电率被用作进一步评估IMD损坏的指标。图 8 显示,同一芯片上两种类型器件的漏电流比之间基本上没有相关性。也就是说,金属 1 和通孔 2 层之间的未对准对两种图案的影响都很小。注意到流动比率,R , 定义为 I LR/I LL 是一个更好的指标,可以从这些模式的芯片到芯片的变化中消除噪声。在完全无偏的器件上,主要的充电应力发生在应该完全随机的右侧或左侧。此处,在电流比上发现了一些偏置效应,其分布介质不是 1。为了确保仅考虑等离子体充电效应造成的损坏,R 是归一化的电流比,如图 9 所示。在晶片中心的分布图中,R 来自 I 型设备的 N 与来自 PID 记录器的等离子体应力水平相当接近。另一方面,R 记录的 PID 级别无法完全解释来自易受双向应力影响的设备的 N。这可能是由显着更高的 R 引起的 模式 II 器件中的 N 级,这是由于晶圆上的附加离子充电事件造成的。

<图片>

示意图和晶圆图显示 (a ) PID 电压和 VBD 来自 (b ) 测试模式 I 和 (c ) II,显示了可归因于区域等离子体充电水平的等离子体诱导的后端介电层损伤在圆圈区域内的区域效应

<图片>

a PID 级别的 VBD 之间的相关性 模式 I 和 b 模式II样本,分别为[10,11,12]

<图片>

V的累积分布比较 晶片上 60 个裸片的 BD 以及部分样品显示来自模式 I 的击穿电压高于来自模式 II 的击穿电压

<图片>

图案I和II的左右侧漏电流比表明这些样品没有系统错位效应

<图片>

一 与相应的 PID 水平和 b 相比,晶圆中心的模式 I 和 II 样本的归一化电流比 左边漏电流的定义(I LL) 和右 (I LR)

结论

通过在先进的 FinFET Cu BEOL 平台上新提出的差分测试模式,研究了等离子体引起的充电对 IMD 薄膜完整性的影响。研究发现,IMD 层中早期击穿形式的损坏和增加的 SILC 与 12 英寸晶圆上的等离子体充电水平直接相关。

数据和材料的可用性

不适用。

纳米材料