电荷分裂原位记录器 (CSIR),用于实时检查 FinFET BEOL 工艺中的等离子体充电效应

摘要

首次提出并展示了一种具有电荷分裂能力的用于监测生产线后端 (BEOL) 工艺中等离子体诱导损伤的新型装置。这种新颖的电荷分裂原位记录器 (CSIR) 可以在先进的鳍式场效应晶体管 (FinFET) 电路的制造过程中独立追踪等离子体充电效应的数量和极性。它不仅显示天线上的实时和原位等离子体充电水平,而且还分离正负充电效应并提供两个独立读数。随着未来 CMOS 技术推动更精细的金属线,新的电荷分离方案为 BEOL 工艺优化和进一步提高器件可靠性提供了强大的工具。

背景

等离子增强工艺广泛用于鳍式场效应晶体管(FinFET)电路的形成,其由许多高纵横比结构和细金属线组成[1]。在用于实现这些 3D 组合物的制造、蚀刻和沉积步骤期间,FinFET 器件会产生显着的等离子体诱导应力 [2,3,4]。随着 CMOS FinFET 技术的进步,金属线宽和间距比其高度更大幅度地减少,从而推动形成由极细线定义的高纵横比沟槽的需求。不可避免地,这会加剧晶体管的等离子体诱导损坏 (PID),其对电路可靠性的相应影响成为开发 FinFET 技术的关键问题之一 [5,6,7]。在形成小触点、通孔和细金属线时,通常应用强功率和高选择性等离子体[8]。此外,在蚀刻体鳍时,鳍表面上反应离子的溅射会导致体鳍中的缺陷,这对晶体管的特性至关重要 [9]。为了实现鳍状金属栅极和密集互连结构,在先进的 FinFET 技术中更常使用复杂的金属叠层 [10, 11]。此外,高k 先进技术中使用的栅极电介质通常会在等离子体工艺后导致增强的应力诱导捕获 [12,13,14]。在等离子充电期间,通过窄鳍片和基板的放电路径会导致整个晶片上的应力水平更加不均匀 [15]。众所周知,晶体管栅极氧化物上的等离子体引起的应力会导致栅极介电完整性的进一步降低[16, 17]。

由于可靠性故障 [21, 22],等离子体引起的栅极介电膜损坏会导致高度不均匀充电情况下的性能下降,甚至导致产量损失 [18,19,20]。因此,在先进的FinFET技术中,通常使用具有放大天线结构的测试设备来监测PID效应,为进一步的工艺优化提供反馈。

PID 最常用和最广泛使用的度量是具有大型天线结构的测试样本的击穿时间特性。这些 PID 模式的潜在损坏通常通过测量栅极介电层的时间相关退化来反映,因此无法提供等离子体过程的实时反馈 [23]。此外,传统的测试设备无法分辨等离子体感应充电率和/或天线上最大电位的来源和极性。在我们之前的研究[24, 25]中,已经提出了一种带有天线结构耦合的浮动门的PID记录器,它具有原位检测能力。在这项工作中,我们提出了一种具有电荷分离功能的改进型 PID 记录器。通过连接到公共天线结构的正向二极管和反向二极管,新设计为正负电荷提供了单独的路径。因此,可以独立记录两种极性的充电水平。这种新的电荷分裂原位记录器(CSIR)只需要小天线,使未来能够研究生产线中端(MEOL)工艺中的等离子体充电效应。

方法

等离子充电极性

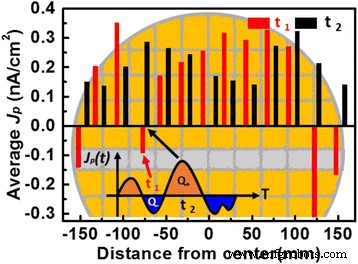

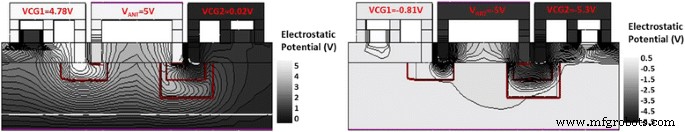

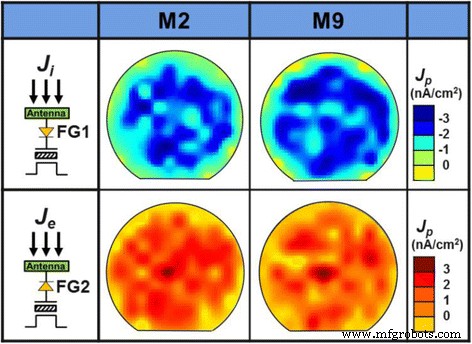

之前的研究表明,在形成多金属层或金属层的蚀刻过程中,等离子体的不均匀性以及天线电位的变化会导致充电速率的巨大差异,甚至不同位置的极性可能会发生变化[24, 25]。等离子体室中的宏观环境和微图案都会影响晶片上充电率的分布 [26]。即,后端 (BEOL) 蚀刻中的等离子体充电速率随空间和时间而变化。在射频 (RF) 等离子体处理过程中,晶片表面收集充电电流,J p,由离子电流J组成 i 和电子流 J e [26]。离子电流随时间几乎恒定,由离子密度J决定 i 和玻姆速度 [26]。由于等离子体电位 V p(t ) 高于栅极电位 V G 在大多数情况下,电子电流仅在等离子体电位接近其最小值的短时间内流动。在Q期间 FG 过程中,栅极电压可能会在许多 RF 周期内增加或减少,具体取决于电流的哪个分量较大,直到隧道电流平衡时达到稳态栅极电压 J p 在天线上。如图1所示,等离子充电率分布,J P (x ,y ,t ),在不同阶段的蚀刻过程中,整个晶片的幅度和极性都会发生变化,其中它可以表示为等式。 (1) 其中 J e 表示电子电流密度,J i代表离子电流密度。

$$ {J}_{\mathrm{p}}={J}_{\mathrm{e}}+{J}_{\mathrm{i}}\dots $$ (1) <图片><来源类型="image/webp" srcset="//media.springernature.com/lw685/springer-static/image/art%3A10.1186%2Fs11671-017-2309-0/MediaObjects/11671_2017_2309_Fig1_HTML">.gif?as=webp

不同时间刻蚀过程中晶片中心线的等离子体诱导充电率分布。特定位置的等离子体充电极性可能会随时间变化

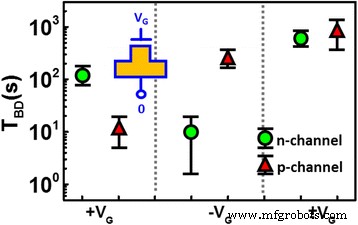

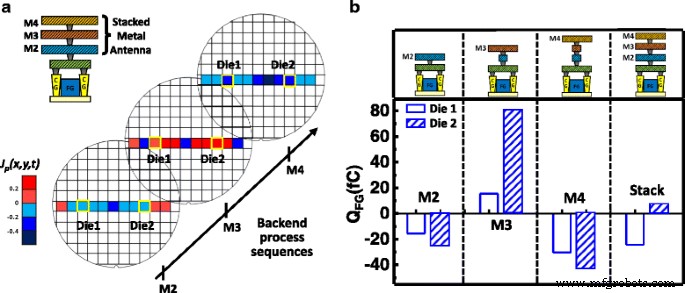

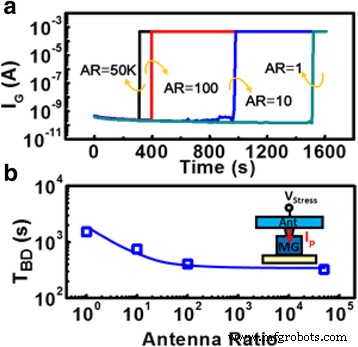

不同的等离子体充电极性导致天线带正电荷或负电荷,Q P,在不同的时间和地点累积。澄清一下,在 t 时间 1、负J p 导致天线负电荷 Q -.在 t 2、正J p 在晶片上的相同位置感应出正天线电荷 Q+,如图 1 所示。因此,在蚀刻过程中,正电荷或负电荷可能会在不同时间积聚在同一天线上。从之前的报告 [27] 中,J 的峰值水平 e 和 J i 大约为 − 0.15 和 0.35 mA/cm 2 , 分别。已经发现 [28, 29] n 沟道和 p 沟道 FinFET 上的 DC 和 AC/双向栅极应力会导致对栅极介电膜的不同潜在损坏。具有正或负直流偏置的高压应力和开关频率为 0.1 Hz 的交流电压分别应用于传统的 FinFET 测试样品。如图 2 所示,击穿时间 (T BD) 的晶体管在两个方向上受到正、负和栅极应力的压力进行了比较。结果表明 DC 栅极应力会对样品造成更严重的损坏,而 AC 栅极应力对这些晶体管的损坏不太严重,正如较长的 T BD 用于承受双向应力的样品。图 2 还表明,氧化物退化不仅取决于充电极性,还取决于 n 沟道和 p 沟道晶体管下方的阱类型,这预计是由这些测试的放电路径差异引起的过程中的设备。因此,使用 T 的传统 PID 检测器 BD 作为损伤严重程度的指标不能反映过程中的等离子体充电水平。另一方面,我们之前工作中提出的等离子体充电记录器通过向/从由电荷收集天线耦合的浮栅(FG)注入或喷射电子来记录应力水平。记录的数据,浮栅电荷(Q FG),随后在制造后读取 [24, 25]。然后通过读取晶体管上的阈值电压偏移来测量记录,其中的通道由同一浮栅控制和引导。 Q 天线上的上升电位 在形成单个金属层期间,来自等离子体充电的 P 可以感应正负天线电压。此外,对于不同的金属层,使用不同的制造参数。例如,蚀刻时间、使用的化学品和腔室温度可能会有所不同。这些参数会影响蚀刻过程中晶片上的天线电荷分布。在其他情况下,连接到多个金属层的晶体管会经历更复杂的等离子体充电序列,如图 3a 所示。

<图片>

击穿时间 (T BD) 的 n 沟道和 p 沟道 FinFET 由栅电极上的正、负和正 + 负充电应力。 T 不同极性应力下器件的BD表明栅介质上累积的损伤不仅取决于充电极性,还取决于相应FinFETs下的阱

<图片>

一 不同金属层的等离子体充电效应在晶片上的不同位置有所不同。 b 堆叠金属层中的正负电荷可以相互补偿

在 BEOL 工艺的不同阶段,特定天线处的等离子体充电电流可以在离子和电子电流之间切换,即净 Q P 也可以从正变为负。图 3b 总结了由金属 2、金属 3、金属 4 和多个金属层组成的天线样品的记录。数据表明单个金属层 [24] 的净电荷在层与层之间的特定变化极性上。此外,在 Q 上发现的平均效应 图 3b 中的测量数据进一步支持了具有多个金属层的天线结构的样品的 FG。带有正负 V G 在天线上,最后的 Q 然后,FG 将通过电子注入和射出到 FG 中/从 FG 中依次发生而被平均。这种补偿效应将限制记录仪揭示设备在等离子体工艺过程中所经历的真实应力条件。修订后的CSIR旨在解决如何在不受干扰的情况下单独记录正负充电效应的问题,并提供有关等离子体室充电情况的更详细数据。

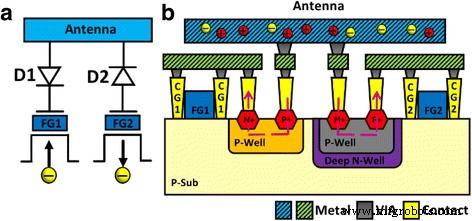

电荷分离测试模式

在这项研究中,天线上的正离子充电和负电子充电可以通过提出的新电荷分裂原位记录器(CSIR)分开,如图 4a 所示。 CSIR 由两个浮栅 FG1 和 FG2 组成,它们分别记录不同类型的充电效应。天线结构分别通过正向二极管 (D1) 和反向二极管 (D2) 连接到两个耦合门。在结构的左半部分,正电荷将通过 D1 流入耦合门 1(CG1)。当CG1充正电时,电压通过两侧的接触槽耦合到浮栅。当电子从衬底注入时,浮栅将带负电。另一方面,该结构的右半部分是负充电路径,允许电流通过 D2 从天线流入耦合门 2 (CG2),从而产生正 Q FG。图 4b 进一步显示了带有片上 pn 二极管的 CSIR 的横截面图,将正负充电路径引导到单独的耦合栅极 CG1 和 CG2,它们将天线上的电位耦合到 FG1 和 FG2,分别。

<图片>

一 通过分别连接到正向二极管 (D1) 和反向二极管 (D2) 来检测电子/离子充电,具有两个独立浮栅的原位电荷分离记录器。 b 带有片上 pn 二极管的新型电荷分裂原位记录器的横截面图,将正负电荷引导至分离的耦合门 CG1 和 CG2

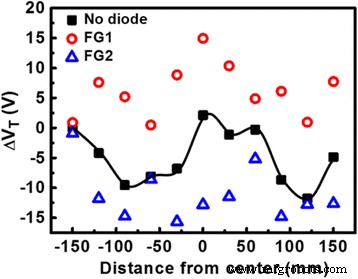

当在带正电的天线下的 CSIR 中启用记录器的左半部分时,右半部分不活动,因为电荷被反向二极管阻挡,反之亦然。两个片上二极管均由 n+/p 阱组成。对于 D2,为了在其 p 阱中维持负电压,p 区需要被深 n 阱包围,从而阻止直接通向衬底的充电路径。图 5a 和 b 分别显示了在天线的正负充电周期下 CSIR 横截面的模拟电位分布。假设天线上的电位达到 5V,通过左边的二极管,正电荷流向左边的控制栅,从而产生高正电压(V CG1)。同时,正电荷被右边的二极管阻挡,导致V接近于零 CG2.图 5a 中的模拟电位轮廓验证了两个控制栅极上的电位差。负电荷对天线的影响如图 5b 所示。模拟电位曲线验证了片上 pn 二极管可以按照设计有效地引导和阻断 CG1 和 CG2 的电位。这样可以独立获得等离子体处理中不同来源对应的正负电荷效应,避免了电荷补偿和探测器干扰问题。

<图片>

具有正负天线栅极电压的 CSIR 中的模拟电位分布。正反向pn二极管成功分离天线电荷极性

结果与讨论

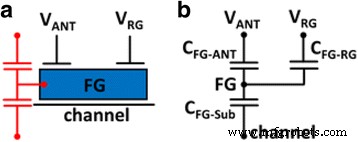

测量的阈值电压偏移 (ΔV 图 6 比较了由带正向二极管的 FG1 和带反向二极管的 FG2 控制的器件上的 T) 和没有二极管的样品。沿晶片中心线的数据显示,具有单个浮栅的记录器确实受到电荷中和甚至在处理单个金属层时。没有二极管的记录器的平均效果证明峰值充电率不会如实反映。另一方面,来自新 CSIR 的读数可以独立提供正负充电水平。为了进一步研究金属 2 (M2) 形成中的等离子体充电效应,每个芯片的 CSIR 的 FG1 和 FG2 上收集的电荷可以通过方程独立计算。 (2),

$$ {Q}_{\mathrm{FG}}={C}_{\mathrm{T}}\times \Delta {V}_{\mathrm{T}}\times {\alpha}_{\mathrm {RG}}\dots $$ (2)其中 Q FG 是浮栅中的电荷。 C T 是浮栅的总电容,如图 7 所示。 ΔV T 是记录器读取门检测到的阈值电压偏移,而 α RG是来自读门的耦合比。

<图片>

delta V 的分布 带正向二极管的FG1和带反向二极管的FG2上的T,以及沿晶片中心线的不带二极管的FG

<图片>

一 CSIR器件中电容网络模型的示意图。 b 浮栅总电容为所有提到的串联电容和并联电容

当浮栅电荷初始为零且 Q 当栅介质层两端的电场减小到零时,FG 达到饱和电平,等离子体工艺结束时的最终天线栅电势可表示为:

$$ {V}_{\mathrm{ANT}}=\frac{V_{\mathrm{FB}}-\frac{Q_{\mathrm{FG}}}{C_{\mathrm{T}}}}{ \alpha_{\mathrm{ANT}}}\dots $$ (3)其中,V ANT 是等离子体充电的天线栅极电位,α ANT 表示从天线门到浮栅的耦合比。 V FB 是从金属栅极到鳍状衬底的平带电压。在给定的工艺时间下,平均等离子体充电电流密度,J p 然后可以通过等式进行投影。 (4).

$$ {J}_{\mathrm{p}}=\frac{V_{\mathrm{ANT}}\times {C}_{\mathrm{ANT}}}{A_{\mathrm{ANT}}\times \Delta t}\dots $$ (4)其中 Δt 是等离子体过程的持续时间 [28, 29] 和 C ANT 是金属天线的总电容,而 A ANT 是天线的充电面积。上述计算中使用的所有参数汇总于表1中。

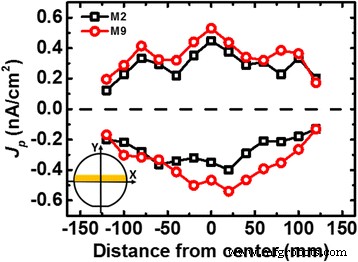

图 8 进一步比较了在处理顶部(金属 9)和底部金属(金属 2)层期间整个晶片的正负充电率分布。这意味着天线结构上的充电在更高金属上更为突出水平(金属 9),因为在金属 9 上,其较高的等离子体能量会导致 J p 大于 J p 金属 2 的数量级。此外,数据表明两种情况下电子和离子充电率均在中心附近达到峰值。正如预期的那样,靠近晶圆中心的芯片会经历高充电水平,这可归因于等离子体处理期间较长的放电路径。发现这种位置效应对于更多电子和离子充电的主导条件是相同的。预计的等离子充电率,J P (x,y ),在形成单个金属层,金属 2 (M2) 和金属 9 (M9) 上的平均值,在图 9 中进一步比较。这些晶片图显示电子充电率似乎处于稳定状态,除了边缘,而离子充电率在晶片的中间部分显示出更高的变化。未来,这些不同处理条件下的晶圆图有望通过更好地补偿充电效应为等离子体室提供见解,或进一步优化指导。

<图片>

金属 2 和金属 9 工艺在晶片中心线的正负充电率比较。充电速率在中心附近达到峰值,这意味着在晶片中心处等离子体引起的损伤更严重

<图片>

投射的电子和离子充电率,J e(x ,y ) 和 J 我(x ,y ) 是通过在金属 2 金属 9 形成过程中穿过蚀刻表面的电荷分裂记录器获得的

天线比效应

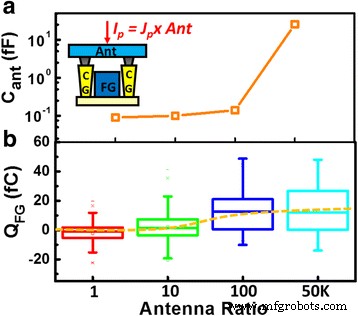

传统的 PID 监控设备通常设计为通过将晶体管的栅极直接连接到大天线来放大 PID 效应,通过增加总 Q 来评估应力水平 P 预计将通过一个小通道区域放电 [30, 31]。天线比 (AR) 与等离子体工艺过程中通过栅极电介质的应力电流密度成正比 [32]。大Q 众所周知,天线上的 P 会在介电层中引起潜在损坏和/或陷阱,最终导致可靠性降低 [33]。正如预期的那样,传统 FinFET 上更高的 AR 确实会显着提高应力水平,导致更严重的 TBD 退化,即在更短的操作时间内出现器件故障,见图 10。另一方面,在 CSIR 中,等离子体充电电平记录为浮栅电荷,Q FG,显示出非常小的天线效应。即,它不会响应增加的天线面积,如图 11 中汇总的数据所示。

<图片>

一 击穿时间特性I 随着天线尺寸的增加,传统 PID 检测器的 G 与时间的关系。 b T AR超过1000时BD急剧下降

<图片>

一 随着天线电容的增加,V CG 变得独立于 AR。 b 问 AR超过100×时FG饱和

在新的基于浮栅的 CSIR 中,天线比 (AR) 将影响等离子体充电期间耦合栅上的峰值电位。在缩放技术中,连接和耦合结构上的寄生电容预计会减少,从而导致记录结果的 AR 灵敏度降低。导致CSIR和传统探测器之间AR效果如此明显差异的原因如下。在这些浮栅记录器中,累积在天线上的电荷 Q P 不会通过沟道区放电。增加Q P 提高 V CG,导致电子注入或弹出浮栅。如图 11a 中的模拟电容所示,天线的电容 C ant,与天线面积成比例增加,A 蚂蚁。由于总充电电流与天线面积成正比,CSIR 中增加的 AR 不会影响天线上的电位。测量数据表明Q AR 超过 100 倍的 SCIR 的 FG 水平保持不变。

此功能不仅可以节省测试图案面积,还可以找到J P (x ,y ) 具有更高的空间分辨率,用于研究模式对 PID 的影响。此外,带有小天线的检测器可以方便地设计用于理解线路中端(MEOL)和接触过程中的PID的测试模式。

最后,表 2 总结了先进 BEOL FinFET 工艺中用于监控 PID 的新型 CSIR 的性能总结。传统检测器的检测范围为 AR,而新型原位记录器的检测范围基于浮栅长度。此外,新的原位记录器的面积可以非常小。最重要的是,新的CSIR可以独立提供等离子体过程的实时反馈以及不同水平的离子充电和电子充电率。

结论

首次提出并展示了一种用于监测等离子体诱导损伤的新型电荷分裂原位记录器 (CSIR)。 CSIR 为同时了解等离子体室中的电子充电和离子充电速率提供了强大的工具。晶圆图有助于进一步研究器件可靠性与这些单独充电效应之间的相关性。

更改历史

纳米材料

- 斑马鱼:一种用于纳米技术介导的神经特异性药物递送的有前景的实时模型系统

- 铝硅酸盐矿物的替代掺杂和优异的水分解性能

- 以叶酸受体为靶点的生物类黄酮染料木素负载壳聚糖纳米颗粒可增强对宫颈癌的抗癌作用

- 接触非平衡等离子体对 Mn Х Fe3 − X О4 尖晶石结构和磁性能的影响

- 原位退火处理对基于 TIPS-并五苯的有机场效应晶体管的迁移率和形态的影响

- 通过反应射频 (RF) 热等离子体原位合成双金属钨铜纳米粒子

- 用于磁热疗的电纺 γ-Fe2O3/聚氨酯纳米纤维的电场辅助原位精确沉积

- 用于抗菌伤口敷料的原位静电纺丝碘基纤维网

- 用于实时呼吸监测的便携式摩擦纳米发电机

- 用于人脸识别应用的 ReS2 电荷捕获突触设备

- FinFET Cu BEOL 工艺中等离子对金属间电介质的损伤的测试模式设计

- 深低温活化处理对用作锂离子电池阳极的大麻茎衍生碳的影响