用于垂直晶体管应用的磷掺杂硅/硅-锗多层结构的生长和选择性蚀刻

摘要

垂直栅环场效应晶体管 (vGAAFET) 被认为是替代 FinFET 的潜在候选者,可用于 3 纳米技术节点/超过 3 纳米技术节点的先进集成电路制造技术。 Si/SiGe/Si 的多层 (ML) 通常生长和处理以形成垂直晶体管。在这项工作中,研究了 Si/SiGe/Si 中的 P 掺入和这些 ML 的垂直蚀刻,然后在横向方向上选择性蚀刻 SiGe 以形成 vGAAFET 结构。提出了几种外延策略,例如氢气吹扫以耗尽 Si 表面上 P 原子的通路,和/或在 P 掺杂的 Si 层两侧插入 Si 或 Si0.93Ge0.07 间隔物,以及用 SiH2Cl2 代替 SiH4 (DCS)。实验结果表明,在P掺杂的Si中加入7%的Ge也可以缓解偏析和自掺杂。该结构具有良好的晶格质量,几乎没有应变松弛。还讨论了使用湿法和干法蚀刻的 P 掺杂 Si(或 P 掺杂 Si0.93Ge0.07)和 SiGe 之间的选择性蚀刻。还比较了不同蚀刻方法的性能和选择性。本文提供了如何应对垂直 GAAFET 结构中 n 型层外延和蚀刻的挑战或困难的知识。

介绍

随着互补金属氧化物半导体 (CMOS) 的缩放达到其物理极限,短沟道效应显着削弱了晶体管的性能。这些问题的解决方案是新的晶体管设计,例如 GAAFET(环栅场效应晶体管),它也被认为是低至 3 纳米技术节点的纳米级晶体管的最有希望的候选者 [1,2,3 ,4,5,6]。根据国际器件和系统路线图 (IRDS) 2020,横向和纵向纳米线/纳米片是替代 FinFET [7] 的主要结构。垂直 GAAFET(或 vGAAFET)在栅极长度上具有自由的灵活性设计,并且具有增加集成密度的巨大潜力 [4, 8]。实现垂直纳米线结构有两大类:自底向上和自顶向下。自下而上的方法引入了金属催化剂,这可能会带来工艺兼容性问题[9, 10]。自顶向下的方法是业界主流,因为它可以更好地控制纳米线配置,并且与 FinFET 兼容 [4, 11,12,13,14]。制造垂直 GAAFET 的自上而下的方法备受关注。具有精确栅极长度控制的自对准栅极是一个关键问题 [15, 16]。为了实现更有效的栅极长度控制或减少变化,栅极长度可以主要由在底部平坦表面上外延生长的沟道材料的厚度决定,例如 Si/SiGe/Si,而 SiGe 是沟道材料 [17, 18,19,20]。此外,另一个关键的集成挑战在于沟道和 S/D 区域之间的掺杂 [16, 20, 21],尤其是尖锐结控制 [20]。与传统的源/漏注入工艺相比,外延工艺简化了制作工艺,减少了表面损伤,并实现了均匀的掺杂分布。然而,由于最常见的 n 型掺杂剂磷的偏析、自掺杂和外扩散现象,P 掺杂的 Si/SiGe/P 掺杂的 Si 夹层结构难以外延生长 [22, 23],化学气相沉积 (CVD) 系统中 Si/SiGe 界面处的砷 [24, 25] 和/或锑 [26, 27]。因此,在Si/SiGe界面和SiGe层处聚集的分离施主原子会被掺杂,这可能会降低晶体管性能并产生高泄漏。

阻止掺杂剂分离的一种策略是应用非常低的生长温度。有一系列报道通过分子束外延 (MBE) [28] 来努力生长 n 型掺杂;同时,该方法尚未应用于 CVD。 MBE设备多为单芯片设计,要求真空度高,吞吐量慢。此外,MBE设备与工业上8英寸以上的晶圆尺寸不兼容。因此,MBE 技术不适合工业大规模生产应用。但RPCVD系统生产能力强,设备结构简单,适用于IC行业[29]。 RPCVD 生长的第一个想法是调节腔室中的氢气流量,因为氢气是载气并且会影响前体气体的动力学。李等人. [23] 报道称,通过在快速热化学气相沉积 (RTCVD) 系统中应用低生长温度,氢改变了表面主体原子的键合结构并降低了偏析能。然而,在减压 CVD (RPCVD) 系统中,尚未在 Si/SiGe 界面探索氢的影响。 Suvar 等人. [30] 在 P 掺杂的 Si 和 SiGe 之间插入 30-nm 未掺杂的 Si 间隔层,以将界面处的 P 浓度降低 4 倍(从 8 × 10 19 厘米 −3 到 2 × 10 19 厘米 −3 ),但不能消除P掺杂峰。 Bennett 等人. [31] 研究了应变对 Si 中 n 型掺杂的影响。通过在 Si 中引入拉伸应变来增加掺杂的固溶度。克里斯滕森等人. [32] 发现 P 扩散率对 Si1-xGex 中的 Ge 含量没有显着依赖性(0 ≤ x ≤ 0.22)。并且P扩散系数在松弛Si和双轴压应变SiGe之间几乎没有差异。 Zangenberg 等人. [33] 观察到在 825°C 下,对于松弛的 Si0.88Ge0.12,扩散系数提高了 2 倍。

在本文中,已经提出了几种方法来使用 RPCVD 提高 Si/SiGe/Si 多层结构中 P 的掺入。在实验中,采用了不同的策略,例如氢气吹扫、插入未掺杂的间隔层、将 Si 前驱体从 SiH4 更改为 SiH2Cl2 (DCS),以及通过在 SiGe 层的两侧引入 Si0.93Ge0.07 牺牲层来调节应变分布。提出了。此外,讨论了 SiGe 的选择性蚀刻以形成薄 SiGe 层(旨在作为沟道层)[6, 34]。还比较了湿法和干法蚀刻工具的蚀刻特性。最终结构将在未来用于亚 10 纳米技术节点的 vGAAFET。

方法

使用 RPCVD (ASM Epsilon 2000) 设备在 200 毫米 Si <100> 晶片上生长 Si/SiGe/Si 多层 (ML)。在插入外延室的负载锁之前,用 H2SO4 和 H2O2 的混合溶液清洁 Si 衬底,然后用稀释的 HF 去除天然氧化物。通过在 1050°C 下退火来原位清洁样品以去除天然氧化物以获得高质量的 Si 表面。 Si、Ge 和 P 的前体是 SiH4(或 SiH2Cl2)、10% GeH4 的 H2 和 2% PH3 的 H2。生长温度为 650 °C,而外延过程中腔室压力保持在 80 Torr。在一些实验中,腔室压力降低到 10 Torr,以在源极/漏极 (S/D) 区域中生长 P 掺杂的 Si0.93Ge0.07 层。 SiGe 通道中的 Ge 含量保持恒定为 0.22。为了研究选择性蚀刻特性,沉积 50 nm 氮化物/30 nm 氧化物作为硬掩模以保护下层 ML。进行光刻和干式各向异性垂直蚀刻以形成单独的长方体图案。使用 HF (6%):H2O2 (30%):CH3COOH (99.8%) =1:2:4 的湿蚀刻工具和 CF4:O2:He =4:1:5 的干蚀刻工具进行选择性蚀刻实验[35].

Si/SiGe/Si MLs 通过高分辨率 (Thermo Scientific Talos F200) 透射电子显微镜 (HRTEM)、能量色散 X 射线光谱 (EDX)、高分辨率 X 射线衍射 (HRXRD) 技术表征, Bruker JV Delta-x 的高分辨率倒易晶格图 (HRRLM)、日立 (日本) 的扫描电子显微镜 (SEM) 和二次离子质谱 (SIMS)。

结果与讨论

P 掺杂 Si/SiGe/Si MLs 的外延

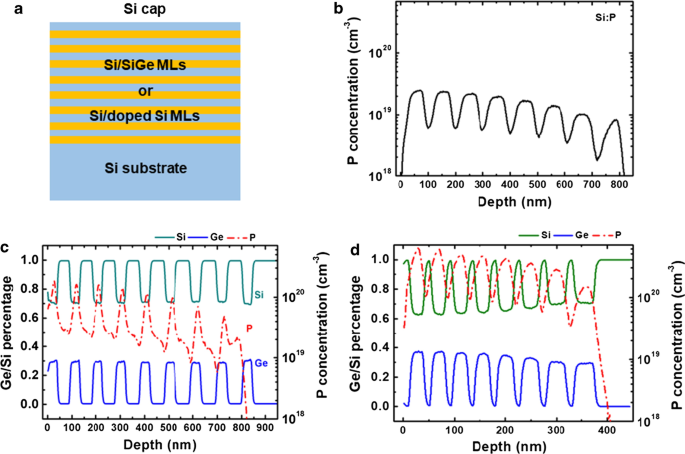

在这项研究中,最初探索了在 Si 和 SiGe 中掺入 P。 ML 结构如图 1a 所示。随着 PH3 流量的增加,生长了 ML 的 P 掺杂的 Si/未掺杂的 Si,层轮廓通过图 1b 中的 SIMS 检查。图中P浓度增加,达到最高水平2.6 × 10 19 厘米 −3 .设计了另外两个具有'P-掺杂的Si/Si0.72Ge0.28/P-掺杂的Si'和'Si/P-掺杂的Si0.72Ge0.28/Si'剖面的样品,P-剖面如图所示. 1c,d,分别。在图 1c 中,在 P 掺杂的 Si/Si0.72Ge0.28 多层的界面处观察到 P 堆积。多层中自下而上随着P浓度的增加,界面P堆积增加,最高浓度为1.6 × 10 20 厘米 −3 ,是图 1b 中浓度的 6 倍(2.6 × 10 19 厘米 −3 )。在掺杂的 Si0.72Ge0.28 层(图 1d)中,P 浓度明显更高,并且界面处没有峰。由于掺杂,Ge百分比略有增加。这种行为与在 PH3 存在下 SiH4 和 GeH4 的吸附增强有关。此外,由于掺杂,图 1c、d 之间的层厚度不同,它们具有相同的生长时间。这意味着 P 掺杂提高了 Si0.72Ge0.28 层的生长速度和 GeH4 的吸收,而 Si 的生长速度由于 P 吸附而延迟。这些现象与参考文献中报告的结果一致。 [36,37,38]。综上所述,Si/SiGe界面处P偏析和自掺杂现象严重。 Si/SiGe 界面处的 P 掺杂峰值会在 SiGe 层中无意掺杂。由于 SiGe 旨在作为晶体管中的沟道层,不均匀的掺杂分布或高背景掺杂水平将限制器件应用 [39]。下面将讨论几种消除 P 峰的方法。为了更好的比较,所有的 SiGe 层都受到了应变,并且在整个实验过程中,SiGe 层的 SiH4 (SiH2Cl2) 和 GeH4 的流量比没有改变。

<图片>

一 P掺杂的Si/SiGe/Si MLs的示意图。 b 未掺杂的 Si/P 掺杂的 Si MLs 的 P 掺杂浓度。 c的Ge/Si百分比和P浓度 未掺杂的 Si0.72Ge0.28/P 掺杂的 Si,d 未掺杂的 Si/P 掺杂 Si0.72Ge0.28 MLs。未考虑清除和未掺杂的间隔层

间隔层的影响

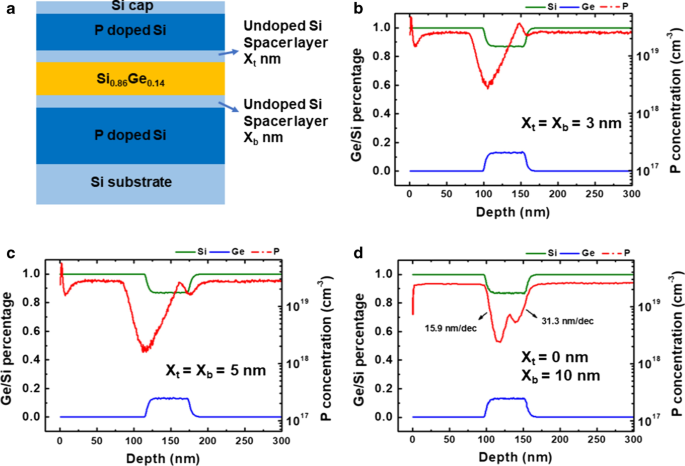

未掺杂的 Si 间隔层插入底部掺杂的 Si 层和未掺杂的 SiGe 层之间,以吸收多余的 P 原子。图 2a 显示了设计结构的示意图,图 2b-d 展示了厚度为 (b) 3 nm、(c) 5 nm 和 (d) 10 nm 的集成硅隔离物的轮廓结果。 P堆积的峰值减少,而Si层中的Si/Ge百分比和P浓度保持恒定,如图2b-d所示。 P堆积水平从4 × 10 19 降低了82% 厘米 −3 在图 2b 到 7 × 10 18 厘米 −3 在图 2d 中,当垫片厚度 X b 从 3 纳米增加到 10 纳米。增加未掺杂的 Si 间隔层的厚度会增加对过量 P 原子的吸收。在图 2d 中,Si0.86Ge0.14/Si 表面的 P 剖面斜率为 15.9 nm/dec,而在 Si/Si0.86Ge0.14 界面的斜率为 31.3 nm/dec。同时,由于薄层电阻增加,太厚的Si间隔层不是合适的解决方案。因此,对于晶体管,必须在薄层电阻和不受控制的 P 剖面之间进行权衡。图 2 还揭示了 Si/Si0.86Ge0.14 层 (X b) 不同于 Si0.86Ge0.14/Si (X t)。在图 2b、c 中,Si0.86Ge0.14/Si 之间的间隔层厚度为 3 纳米和 5 纳米,而在图 2d 中,没有插入间隔层。然而,Si0.86Ge0.14/Si 处的 P 剖面斜率相同(约 15.9 nm/dec),尽管在图 2d 中顶部间隔层被移除,但未观察到对掺杂剖面的影响。由以上结果可知,P峰仅出现在Si/Si0.86Ge0.14界面,可能是由于溶解度限制;过量的 P 原子可能会在表面形成 P-P 二聚体并结合在 SiGe 帽层中。此外,在 P 掺杂 Si 之后的 SiGe 生长过程中存在 P 的自动掺杂。因此,人们一直在寻找清除过量P原子或提高Si溶解度的方法。

<图片>

一 具有不同未掺杂间隔层的实验样品示意图。以及具有 b 的未掺杂 Si 间隔层的 P 掺杂 Si/Si0.86Ge0.14/P 掺杂 Si MLs 的 Ge、Si 和 P 分布 3 nm,在两个接口中,c 5 nm,在两个界面中,d 10 nm,仅与 Si0.86Ge0.14 的一个界面

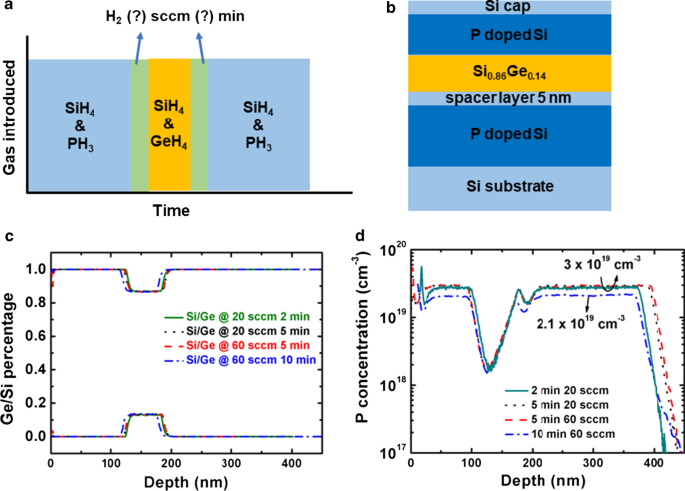

氢清除对 Si/SiGe/Si MLs 界面的影响

在此部分中,Si 间隔层固定在 5 nm,并在 P 掺杂的 Si 生长后引入氢气清除以清除多余的 P 原子。从图 3c、d 可以看出,将氢气流量从 20 增加到 60 sccm,将吹扫时间从 2 增加到 10 分钟,对 P 峰没有明显影响。 Si中的掺杂浓度为3 × 10 19 厘米 −3 ,这与“间隔层的影响”一节中讨论的相同。界面处的 P 峰浓度与图 3d 中的 Si 浓度相同。在不同的净化条件下,层厚是相同的。 P原子不能被氢清除;这可以通过在表面形成稳定的 P 络合物来解释。通过改变温度、压力、吹扫时间等参数会有所帮助 [24, 40],但由于时间成本,过长的吹扫时间不合适,而且高温 (> 950°C) 会导致 Si-Ge 相互扩散 [41] .

<图片>

a示意图 H2吹扫条件的掺杂策略,以及b Si/SiGe/Si MLs 的实验结构。 c Ge/Si 剖面和 d P掺杂Si/Si0.86Ge0.14/P掺杂Si MLs的P浓度

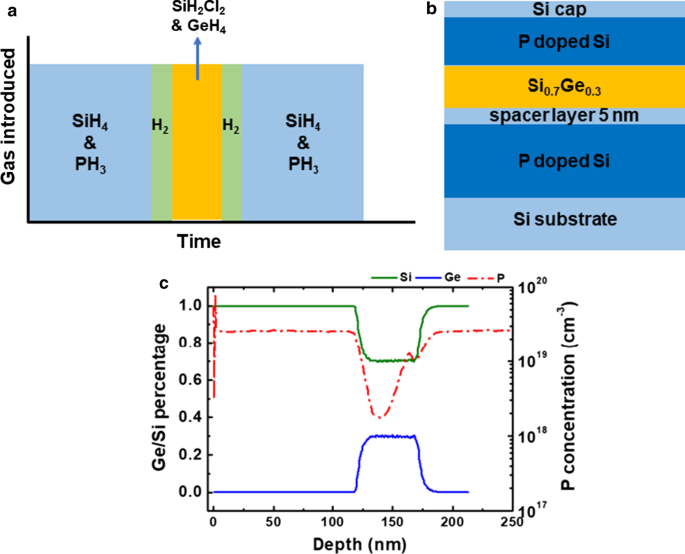

生长化学对 P 掺入的影响

在这些实验中,Si 前体 SiH4 已被替换为 SiH2Cl2 (DCS)。在这些样品中,生长参数与之前相同,结构包含 5 纳米硅间隔层,吹扫时间为 5 分钟,流量为 60 sccm。背后的想法是研究基于 Cl 的化学是否可以通过 Si 表面清除多余的 P 原子,并且可能发生 P-Cl、Si-Cl 或 Ge-Cl 的反应 [42]。从图 4 中,P 峰浓度降低了 2 倍(从 2.6 × 10 19 厘米 −3 到 1.3 × 10 19 厘米 −3 ),Si层中P浓度为2.6 × 10 19 厘米 −3 .估计的 Ge 含量为 30%,高于使用 SiH4 的 SiGe。较高的 Ge 含量表明 Cl 在表面反应中优先去除 Si 原子。这一结果也可以用气体流量比和 Ge 浓度与 SiH4 和 SiH2Cl2 气态前驱体的不同关系来解释 [32, 43]。另一种解释是Ge原子增加了氢解吸,然后增加了自由成核位点[44]。 Si0.7Ge0.3/Si 界面的 P 浓度斜率为 13.2 nm/dec,略高于 Si0.86Ge0.14/Si 界面(15.9 nm/dec)。 Si/Si0.7Ge0.3 界面处的 P 剖面斜率为 20 nm/dec。因此,通过引入更多的 HCl 或增加 SiH2Cl2 和 GeH4 的气体比,掺杂的 Si 表面的分离 P 原子可以被 HCl 蚀刻形成 P-Cl 二聚体,Si/SiGe 处的 P 峰值浓度可能会更低 [38 , 45]。

<图片>

a示意图 改变生长化学的掺杂策略,b Si/SiGe/Si MLs 的实验结构。 SiGe 层是用 DCS 生长的。在掺杂 Si 后,吹扫时间为 5 分钟,流量为 60 sccm。未掺杂的 Si 间隔层在底部掺杂的 Si 和未掺杂的 SiGe 之间为 5nm。 c P掺杂Si/Si0.7Ge0.3/P掺杂Si MLs的Ge/Si分布和P浓度

Ge 含量对 P-profile 的影响

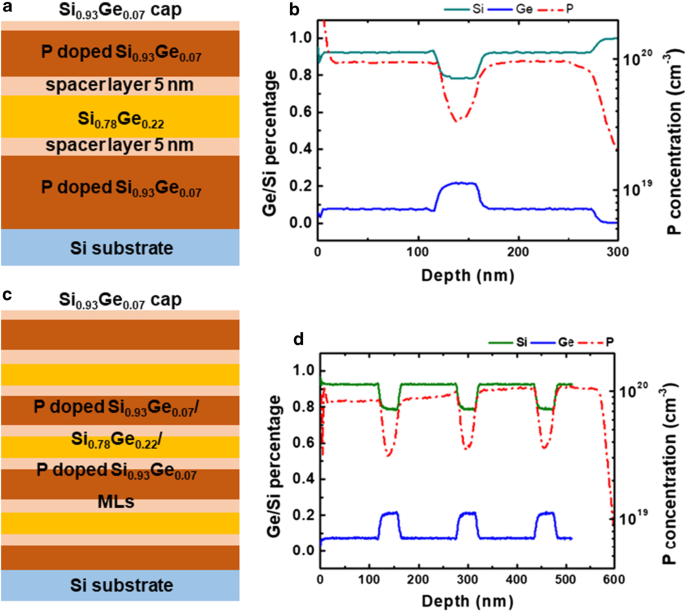

正如我们之前所讨论的,SiGe 中 P 的结合明显高于 Si。因此,这可能会引发这样的想法:在 Si 间隔物 (5 nm) 中添加几个百分比的 Ge (7%) 可以改善 P 在 Si 中的结合。这里值得一提的是,我们的目的不是显着改变 P 掺杂的 Si 的特性,而是阻止 P 在 Si 中的偏析。在这些样品中,在间隔层的生长过程中,腔室压力降低到 10 Torr。在这种情况下,依赖于掺杂的增长率和 Ge 百分比很重要。从图 5b 可以看出,顶层和底层是 110 nm Si0.93Ge0.07,P 浓度为 1 × 10 20 厘米 −3 , 中间层为 40 nm Si0.78Ge0.22,P 浓度为 3.5 × 10 19 厘米 −3 . P 掺杂的 Si0.93Ge0.07/Si0.78Ge0.22 的 P 浓度斜率约为 33 nm/dec。由于两层之间的锗百分比差异不够大,所以斜率并不陡峭。在图 5d 中,生长了三层 P 掺杂的 Si0.93Ge0.07/Si0.78Ge0.22/P 掺杂的 Si0.93Ge0.07 MLs 以验证掺杂均匀性,其结构图如图 5c 所示.可以看出,从底层到顶层,P 浓度逐渐降低,这可以用 P 的记忆效应来解释。 腔室中残留的 P 原子或扩散的 P 原子积聚在薄膜表面,阻塞了薄膜表面的自由活性位点。表面 [38, 39]。虽然消除了P峰,但Si0.78Ge0.22和Si0.93Ge0.07之间的偏析仍然严重。

<图片>

一 示意图,b 一层 P 掺杂的 Si0.93Ge0.07/Si0.78Ge0.22/P 掺杂的 Si0.93Ge0.07 ML 中的 Ge/Si 和 P 分布。 c 示意图,d 三层P掺杂Si0.93Ge0.07/Si0.78Ge0.22/P掺杂Si0.93Ge0.07ML中的Ge/Si和P分布

Si/SiGe/Si MLs 的选择性蚀刻特性

当 ML 结构成功生长时(使用上述生长策略),NW 已通过使用 SiO2/SiN 作为硬掩模的垂直蚀刻形成。之后,必须在横向方向上选择性地蚀刻SiGe层以形成具有设计宽度的沟道层。在这些实验中,选择了两种类型的 ML 结构:P 掺杂的 Si/SiGe/P 掺杂的 Si(样本 1,在图 2c 中)和 P 掺杂的 Si0.93Ge0.07/Si0.78Ge0.22/ P 掺杂的 Si0.93Ge0.07(样品 2,图 5b)。这些选择是根据上述讨论(部分)抑制了 P 的外扩散,并考虑了器件应用的角度做出的。

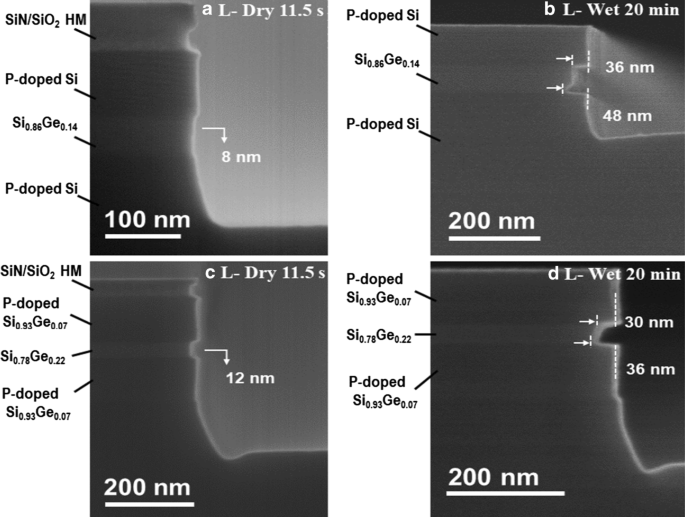

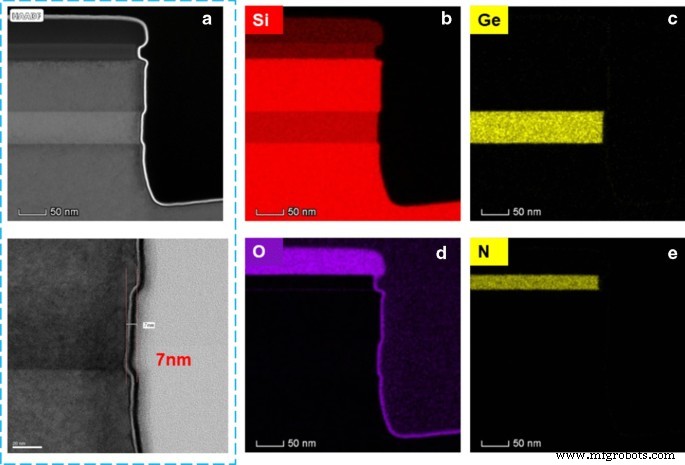

垂直方向的蚀刻通过干蚀刻进行,而对于横向蚀刻,应用选择性干蚀刻或湿蚀刻。样品 1 的蚀刻曲线如图 6a、b 所示。并且图 6a 的 TEM 图像和 EDS 映射已显示在图 7 中。在这些实验中,硬掩模是氧化物/氮化物。图 6a 显示了 CF4/O2/He 干法蚀刻 11.5 秒后。 Si0.86Ge0.14 和 P 掺杂的 Si 的蚀刻选择性为 5.8。图 6b 显示 HF (6%)/H2O2 (30%)/CH3COOH (99.8%) 湿法蚀刻 20 分钟后。湿蚀刻去除了硬掩模 (SiO2/SiN),结果,Si 帽层也被蚀刻 ~ 10 nm。如“间隔层的影响”部分所述,P 掺杂的 Si/Si0.86Ge0.14 界面处存在 P 堆积。湿法蚀刻对掺杂水平敏感;因此,第一个界面蚀刻得更快。因此,前蚀刻界面不是垂直的,而是多面或成角度的。平均选择性小于4.2。比较两种蚀刻方法,干蚀刻对Ge百分比敏感,SiGe选择性更好,而湿蚀刻对掺杂浓度敏感。样品 2 的蚀刻也在图 6c、d 中进行了研究。在该样品中观察到类似的现象,而 SiGe 选择性蚀刻深度更深(图 6a、c),因为 Ge 百分比较高。在干蚀刻中,Si0.78Ge0.22 和 P 掺杂的 Si0.93Ge0.07 的选择性为 6.3,而在湿蚀刻中,平均选择性小于 2.5。因此,考虑到蚀刻的均匀性和选择性,干法蚀刻是更好的选择。

<图片>

图 2c 中 P 掺杂的 Si/Si0.86Ge0.14/P 掺杂的 Si 的 SEM 图像,带有 a 11.5 秒干蚀刻,b 20 分钟湿法蚀刻,P 掺杂 Si0.93Ge0.07/Si0.78Ge0.22/P 掺杂 Si0.93Ge0.07 MLs 与 c 11.5 秒干蚀刻,d 20 分钟湿蚀刻。干蚀刻为CF4:O2:He =4:1:5,湿蚀刻为HF(6%):H2O2(30%):CH3COOH(99.8%) =1:2:4

<图片>

一 TEM 图像,b –e 图 6a 中 P 掺杂的 Si/Si0.86Ge0.14/P 掺杂的 Si 的 EDS 映射,采用 11.5 秒干法蚀刻。 b 中的元素 是 Si,在 c 中 是 Ge,在 d 是 O,并且在 e 是 N

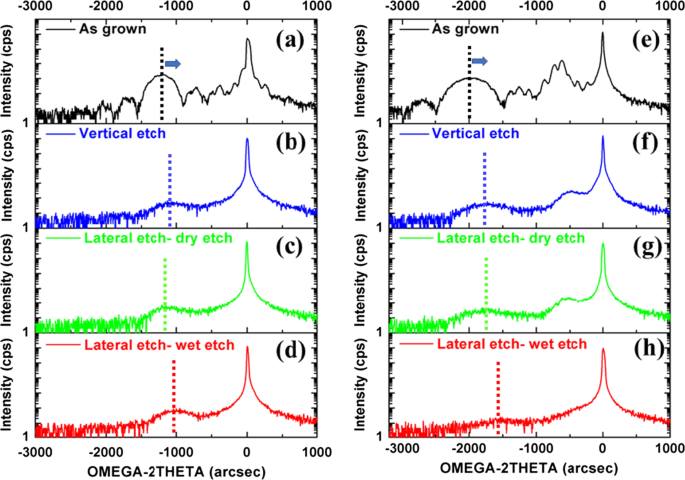

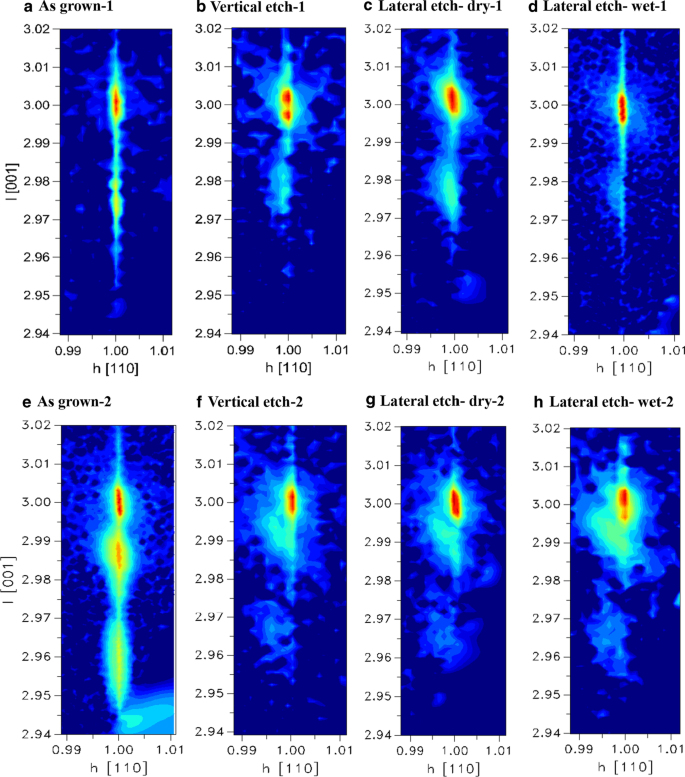

进行了进一步分析以研究样品 1 和样品 2 中蚀刻步骤后的应变。图 8a-h 显示了这些样品的 (004) 摇摆曲线 (RC),如下所示:生长状态、垂直蚀刻后,以及使用湿法和干法蚀刻的 SiGe 横向蚀刻。在 RC 分析中,展宽(全宽半最大值或 FWHM)是缺陷密度的指标,与 Si 相比 SiGe 峰的位置决定了层中的应变量。我们在这里强调,峰展宽也可能是由于层的薄厚度。因此,很难将缺陷密度的贡献与 RC 分析区分开来,但我们只能在这些分析中的某些扩展中比较 FWHM。在这些 RC 中,样本 1(图 8a-d)具有单个 SiGe 层;同时,样品 2(图 8e-h)显示了代表 7% 和 22% Ge 的两个峰。对于生长样品,观察到 X 射线束的干涉,这会导致厚度层条纹。这些条纹的出现表明了高质量的 SiGe/Si 界面。在样品 1 和样品 2 的 RC 中,Ge 峰已向 Si 衬底峰移动,表明应变松弛。在 SiGe 的横向干蚀刻之后,没有检测到 Ge 峰的进一步移动。这是晶体管性能的一个有希望的结果,因为沟道区中的载流子迁移率取决于应变。同时,湿蚀刻的 SiGe 的应变更加松弛,并且已经观察到更多地向衬底峰移动。这说明湿法刻蚀不适用于横向SiGe刻蚀,形成沟道层。

<图片>

样品 1 在 (004) 反射附近的 HRXRD 摇摆曲线,在 a 中具有 5 nm 间隔层的 P 掺杂 Si/Si0.86Ge0.14/P 掺杂 Si ML –d 和样品 2,e 中的 P 掺杂 Si0.93Ge0.07/Si0.78Ge0.22/P 掺杂 Si0.93Ge0.07 MLs –h .两个样品都有四个面板:随着生长,在垂直蚀刻后,HF (6%)/H2O2 (30%)/CH3COOH (99.8%) 的 SiGe 横向湿蚀刻 20 分钟,以及 CF4/O2/He 的横向干蚀刻11.5 秒

进行了进一步的 X 射线分析以找出有关图 9a-h 中样品中缺陷密度的更多信息。如图 9a-h 所示,此处执行基于二维测量的 HRRLM。 HRRLM 中缺陷密度的指标是 SiGe 层沿 ω 方向的展宽(ω 是入射光束角)。 Si 和 SiGe 峰的位置提供平行和垂直于生长方向的应变分量。在样品 1 和样品 2 中,生长的 SiGe 层显示出较小的 ω 展宽,并且该层与 Si 对齐,显示出完全应变的 SiGe 层(见图 9a、e)。图 9b 显示了垂直蚀刻后的样品,SiGe 峰以与图 8b 中的 RC 结果类似的方式移向 Si 衬底,表明应变松弛。但令人惊讶的是,横向干蚀刻样品(图 9c)显示出明显的 SiGe 峰 ω 展宽以及倒易空间的位移,该位移与 Si 峰的排列方向相反。然而,湿蚀刻样品(在图 9d 中)是完全应变对齐的,并且层强度低于干蚀刻样品(在图 9c 中)。在这种情况下,由于蚀刻工艺的性质不同,预计这些样品中产生的缺陷具有不同的来源。 Sample-2 包含两个 SiGe 层;在垂直和横向蚀刻后,Si0.93Ge0.07 峰仍然存在,而在垂直蚀刻后 Si0.78Ge0.22 消失,显示完全应变松弛(图 8f-h)。样品2工艺稳定性差的原因可能是P掺杂促进了错配位错的形成。

<图片>

a 中具有 5 nm 间隔层的 P 掺杂 Si/Si0.86Ge0.14/P 掺杂 Si MLs 的 HRRLMs(样品 1) –d , 和 e 中的 P 掺杂 Si0.93Ge0.07/Si0.78Ge0.22/P 掺杂 Si0.93Ge0.07 MLs(样品 2) –h .这两个映射都有四个面板:垂直蚀刻后,HF (6%)/H2O2 (30%)/CH3COOH (99.8%) 横向湿蚀刻 20 分钟,CF4/O2/He 横向干蚀刻 11.5

结论

在这项工作中,研究了 P 掺杂的 Si/SiGe/P 掺杂的 Si MLs 的外延以及这些 MLs 的蚀刻作为 vGAAFET 的初始结构。首先,研究了 P 在 Si/SiGe/Si MLs 中的掺入。已经提出了不同的外延和 ML 结构策略,以消除 Si/SiGe 异质结构界面处的 P 隔离峰。从实验来看,插入未掺杂的间隔层可以降低 P 峰值。用氢气清除多余的 P 原子不是很有帮助,稳定的 P-P 二聚体不能完全去除。由于 Cl 活性表面反应,用 SiH2Cl2 作为 Si 前驱体代替 SiH4 在生长过程中引入 Cl 化学物质,显着降低了分离的 P 峰。还研究了 P 掺杂 Si 后 Si0.93Ge0.07 间隔层的影响。结果表明,SiGe 界面处的 P 峰消失,而这些层中的 P 掺入提高了一个数量级。在本研究的第二部分中,执行 Si/SiGe/Si ML 的垂直蚀刻以形成 NW,然后,在这些 NW 中,SiGe 被选择性地湿法或干法蚀刻。湿法蚀刻对掺杂浓度敏感;同时,干法蚀刻对Ge含量敏感。干蚀刻更适合具有均匀蚀刻轮廓和更高选择性的 n 型结构。对于 P 掺杂的 Si/Si0.86Ge0.14/P 掺杂的 Si ML,干蚀刻的选择性为 5.8,湿蚀刻的选择性为 4.2。 P 掺杂的 Si0.93Ge0.07/Si0.78Ge0.22/P 掺杂的 Si0.93Ge0.07 MLs 的选择性干蚀刻为 6.3,湿蚀刻为 2.5。经过垂直和横向蚀刻后,SiGe中的应变主要保留在Si/SiGe/Si中;同时,引入Si0.93Ge0.07间隔层的MLs中的该应变在蚀刻工艺后稳定性较差。

数据和材料的可用性

作者声明支持本研究结果的数据可在文章中找到。

缩写

- vGAAFET:

-

垂直栅环场效应晶体管

- ML:

-

多层

- CMOS:

-

互补金属氧化物半导体

- MBE:

-

分子束外延

- RPCVD:

-

减压化学气相沉积

- RTCVD:

-

快速热化学气相沉积

- 标准/日期:

-

源/漏

- HRTEM:

-

高分辨透射电子显微镜

- HRXRD:

-

高分辨率X射线衍射

- HRRLM:

-

高分辨率倒易点阵图

- SEM:

-

扫描电镜

- SIMS:

-

二次离子质谱

- RC:

-

摇摆曲线

- FWHM:

-

全宽半高

- HM:

-

硬掩膜

纳米材料

- 为 CyrusOne 的用户和客户提供更好的应用程序性能

- 10nm 芯片的空气隔离物

- 通过用于光检测应用的简便解决方案技术直接生长羽毛状 ZnO 结构

- 石墨烯/WO3 和石墨烯/CeO x 结构作为超级电容器应用电极的评估

- Fe3+ 的可恢复荧光探针 BHN-Fe3O4@SiO2 混合纳米结构及其在生物成像中的应用

- 通过金属盐-聚合物纳米复合膜的相分离形成的表面纳米结构,用于抗反射和超疏水应用

- 纳米结构黑硅的应用回顾

- 为您的应用选择一种机器人焊接工艺和设备

- 企业迎接 2019 年的重大技术变革和挑战

- 用于铸造、锻造和车削应用的立式车床

- 用于铸造、锻造和车削应用的立式车床(2)

- VMC Machinery 用于生产和提高效率