具有嵌入式 PMOSFET 的稳健且具有闩锁免疫能力的 LVTSCR 器件,可在 28-nm CMOS 工艺中提供 ESD 保护

摘要

低压触发可控硅整流器 (LVTSCR) 有望为低压集成电路提供静电放电 (ESD) 保护。然而,由于其极低的保持电压,它通常容易受到闩锁效应的影响。在本文中,提出了一种嵌入了称为 EP-LVTSCR 的额外 p 型 MOSFET 的新型 LVTSCR,并在 28 纳米 CMOS 技术中进行了验证。所提出的器件具有 ~ 6.2 V 的较低触发电压和 ~ 5.5 V 的显着更高的保持电压,在传输线脉冲测试下故障电流仅降低 23%。还表明 EP-LVTSCR 以 ~ 1.8 Ω 的较低导通电阻以及在 3.63 V 下测得的可靠漏电流 ~ 1.8 nA 运行,使其适用于 2.5 V/3.3 V CMOS 中的 ESD 保护过程。此外,还通过TCAD仿真对所提出的器件的触发机制和传导特性进行了探索和验证。

背景

随着半导体器件特征尺寸的不断小型化,集成电路(IC)中静电放电(ESD)引起的损坏已成为一个更加严重的问题。此外,由于先进的工艺技术,ESD保护器件的制造成本急剧增加[1]。因此,高面积效率和鲁棒性ESD保护器件的设计具有重要价值。

由于其寄生双极结晶体管中的强正反馈效应,可控硅整流器 (SCR) 器件已被证实能够以较小的器件尺寸维持高 ESD 电流 [2]。但 SCR 通常具有高触发电压 (V t1) 超过纳米级 CMOS 技术中输入级的栅极氧化层击穿电压。降低V 在 SCR 的 t1 时,通过插入重掺杂 n + 报告了改进的横向 SCR (MLSCR) 用于输入 ESD 保护 或 p + 跨越 n 阱和 p 阱边界的区域 [3, 4]。但是MLSCR的触发电压仍然大于CMOS输出缓冲器中输出晶体管的击穿电压。因此,它不能单独提供有效的输出ESD保护。

为了有效保护 CMOS 输出缓冲器,人们提出了一种低压触发 SCR (LVTSCR),通过在传统 SCR 中插入一个短沟道 NMOS (PMOS) 器件来实现低得多的触发电压 [5,6,7] ,相当于插入的 NMOS(PMOS) 器件的回弹触发电压。然而,与传统的 SCR 和 MLSCR 器件一样,LVTSCR 也存在闩锁危险,因为它的保持电压 (Vh) 极低,约为 2 V [8]。这种闩锁效应会导致正常工作时发生故障,并不断产生大电流破坏IC [9]。

有几种可能的方法可以改善 V LVTSCR [10,11,12,13,14,15] 的 h。最常见的解决方案是扩大 SCR 寄生双极结晶体管 (BJT) 的基区,以降低其发射极-基极结的注入效率 [10]。采用这种方案不仅会增加器件的布局面积,而且导通电阻(R on) 也应该,这将进一步导致其故障电流 (I t2)。然后,提出了一种优化方法,即在 LVTSCR 中插入浮动 n 阱区,同时对 I 的牺牲较小。 t2 [11],但它也使用大 R 导通电压过高,超过栅极氧化物击穿电压对抗小电流,从而降低其有效的ESD保护电流。在 LVTSCR 中添加额外的 N-LDD/P-HALO 层的方法也可以提升 V h [12],而此类器件仅适用于特定工艺,不能广泛应用于普通 CMOS 工艺。此外,[13] 报道了一种栅极对地 NMOS 触发的 LVTSCR (GGSCR),它增加了 V h 通过将嵌入式 NMOS 的漏极引向阳极,但在低电流情况下,可能会导致嵌入式 NMOS 在 SCR 导通之前被损坏。最近,复合 LVTSCR 结构表现出低 V t1 以及高 V h 在 [14, 15] 中得到了证明。这些复合结构的设计具有很高的复杂性和面积要求,因此考虑到设计成本,限制了它们在先进 CMOS 技术中的应用。因此,在先进工艺ESD保护中,非常需要一种坚固耐用、面积高效且具有闩锁免疫能力的ESD保护器件。

在本文中,针对 2.5 V/3.3 V 电源电压应用提出了一种带有嵌入式 PMOS 晶体管 (EP-LVTSCR) 的新型 LVTSCR 结构。所提出的器件采用 28 nm CMOS 工艺制造,其电气特性通过传输线脉冲 (TLP) 的测量进行验证。通过技术计算机辅助设计 (TCAD) 模拟探索了所提出设备的物理机制。因此,所提出的结构具有较高的保持电压、较低的触发电压和较低的 R 上,并且 I 略有下降 t2 没有任何额外的过程步骤。

方法

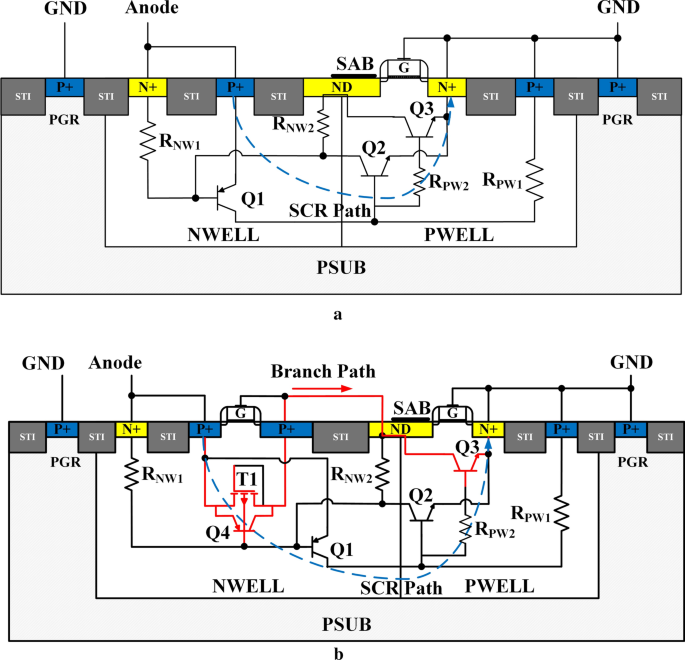

本文研究了传统的 LVTSCR 和提议的 EP-LVTSCR。传统 LVTSCR 和 EP-LVTSCR 的横截面示意图分别显示在图 1a、b 中,而它们的等效电路在具有寄生晶体管和阱电阻器的结构内描绘。在这两种器件中,硅化物阻挡 (SAB) 层都放置在部分 ND 区域的顶部,这将通过阻止硅化物层的形成来引起镇流电阻 [16, 17]。在传统的 LVTSCR 中,NMOS 晶体管插入 PWELL,其漏极 (ND) 设置在 NWELL 和 PWELL 之间,而其源极和栅极一起连接到地 (GND),如图 1a 所示。在ESD应力期间,寄生横向p-n-p BJT(Q1)和寄生横向n-p-n BJT(Q2和Q3)将逐渐导通。在这种情况下,Q1和Q2晶体管耦合构成SCR传导路径,该传导路径将主导电流放电,其中SCR传导路径由虚线表示。

a 的横截面图 传统的 LVTSCR 和 b 拟议的 EP-LVTSCR

与传统的 LVTSCR 相比,EP-LVTSCR 在 NWELL 中嵌入了一个额外的 PMOS 晶体管 (T1),因为其栅极和漏极通过金属连接到 ND,如图 1b 所示。当 ESD 脉冲施加到 EP-LVTSCR 的阳极时,如果跳变电压高于 N+/PWELL 击穿电压,则反向偏置的 N+/NWELL/N+/PWELL/P+ 二极管将首先导通。然后,雪崩倍增效应产生的空穴/电子将流向阴极/阳极,从而增加 NWELL/PWELL 中的电流密度,并进一步提高 NWELL/PWELL 上的压降电位。一旦 R 上的总电压下降 NW1 和 R NW2,相当于源极和栅极之间的压降(− V gs) 的 T1,压倒其阈值电压 (V th) 约 0.9 V,T1 将打开。随后,寄生横向 n-p-n 晶体管 Q2 和 Q3 将依赖于其发射极-基极结的传导而被触发。注意到 T1 的导通会降低 R 在 NWELL 上打开,因此 Q2 和 Q3 可以在较低的电压下触发。随着电流继续增加,R 上的电压下降 NW1 上升到大约 0.7 V 并开启 Q1 和 PMOS (Q4) 的寄生横向 p-n-p 晶体管。最后,可控硅通路导通,支路通路导通。

一些报告表明,SCR 的保持电压主要由 NWELL/PWELL 耗尽区 V 两端的电位差决定 dep [18,19,20],它与注入耗尽区的少数载流子(电子/空穴)成反比。而EP-LVTSCR的分支路径可以提取从SCR路径注入耗尽区的空穴/电子,从而提升V h EP-LVTSCR。

为了进一步论证EP-LVTSCR的物理机理,进行了TCAD仿真,整合了迁移率、复合、热力学、有效本征密度等物理模型,并结合了外推、RelErrcontrol、直流电等数学方法。使用了计算。将 1.2 A 脉冲和 10 ns 上升时间的 ESD 电流建模分别应用于 EP-LVTSCR 和传统 LVTSCR 的阳极,其中器件的基板被视为唯一的散热器,环境温度设置为 300

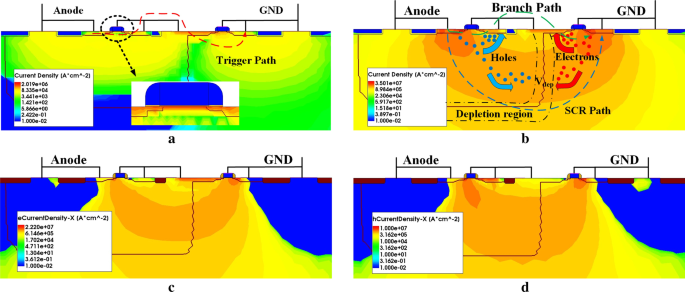

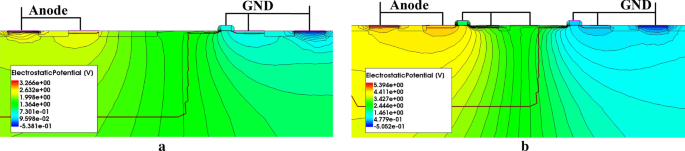

EP-LVTSCR 在 500 ps 和 5 ns 时的总电流密度分布的模拟结果分别如图 2a、b 所示。在 500 ps 时,电流密度分布集中在 T1 和 Q2 晶体管上,这表明 T1/Q2 系列已作为触发路径导通,如图 2a 所示。当时间上升到 5 ns 时,SCR 路径和分支路径都已导通,如图 2b 所示。此时,部分由 P+/N+ 产生的空穴/电子从 NWELL/PWELL 中提取出来流过分支路径,如图 2c、d 所示结构的水平空穴和电子电流密度所示.此外,传统 LVTSCR 和 EP-LVTSCR 在 5 ns 时的静电电位分布在图 3a、b 中进行了比较。显然,EP-LVTSCR 内部的潜在峰值更高。这些仿真结果为上述假设 EP-LVTSCR 较高的保持电压由图 1b 所示的分支路径提供了直接证据。

TCAD 模拟 a t 处的总电流密度分布 =500 ps,b 5 ns 时的总电流密度分布,c 5 ns 和 d 处的水平电子电流密度分布 在 1.2A-TLP 应力下,所提出的 EP-LVTSCR 在 5 ns 时的水平孔电流密度分布

a 的 TCAD 模拟静电势分布 提议的 EP-LVTSCR 和 b t 时的传统 LVTSCR =5 ns 在 1.2A-TLP 应力下

结果与讨论

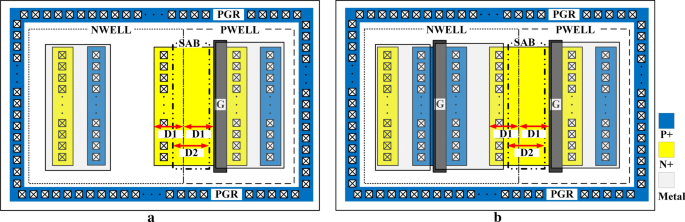

传统的 LVTSCR 和 EP-LVTSCR 在 28-nm 2.5 V/3.3 V 逻辑 CMOS 工艺中实现,宽度相同为 40 um,它们的布局拓扑分别如图 4a、b 所示。为了避免与衬底相关的寄生效应,两种结构都采用了 P 型保护环 (PGR),并且每个 PGR 都连接到 GND [21]。 ND的中轴与NWELL/PWELL结点对齐,参数D1用于描述ND长度的一半,而D2为SAB区域的长度。

a 的布局拓扑 传统的 LVTSCR 和 b 拟议的 EP-LVTSCR

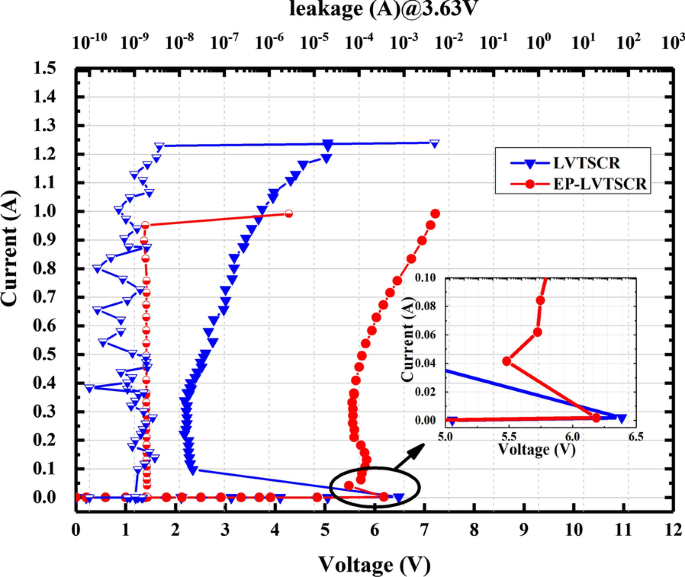

使用 Hanwa TED-T5000 TLP 测试仪以 10 ns 上升时间和 100 ns 脉冲宽度测量传统 LVTSCR 和 EP-LVTSCR 的 ESD 特性,并在每次之后在 3.63 V (1.1 * VDD) 直流电压偏置下测量泄漏电流TLP 压力。 EP-LVTSCR 和 LVTSCR 的测量 TLP I-V 和泄漏特性如图 5 所示。显然,EP-LVTSCR 具有更高的 V 与传统的 LVTSCR 的 2.18 V 相比,h 为 5.49 V。虽然 EP-LVTSCR 对保持电压有显着改善,但它的 I t2 仅下降了约 0.29 A,这得益于支路电流路径的辅助。此外,EP-LVTSCR 还执行 V t1 从 6.49 降至 6.18 V。对于 28 纳米 CMOS 工艺中的 2.5 V 或 3.3 V IO 引脚,ESD 设计窗口范围为 3.63 至 9.4 V,并考虑了 10% 的安全裕度。因此,通过克服传统 LVTSCR 型结构中的闩锁问题,所提出的 EP-LVTSCR 可用作 2.5 V/3.3 V IO 端口的有效 ESD 保护解决方案。

EP-LVTSCR 和传统 LVTSCR 的 TLP I-V 和漏电流测量值相同

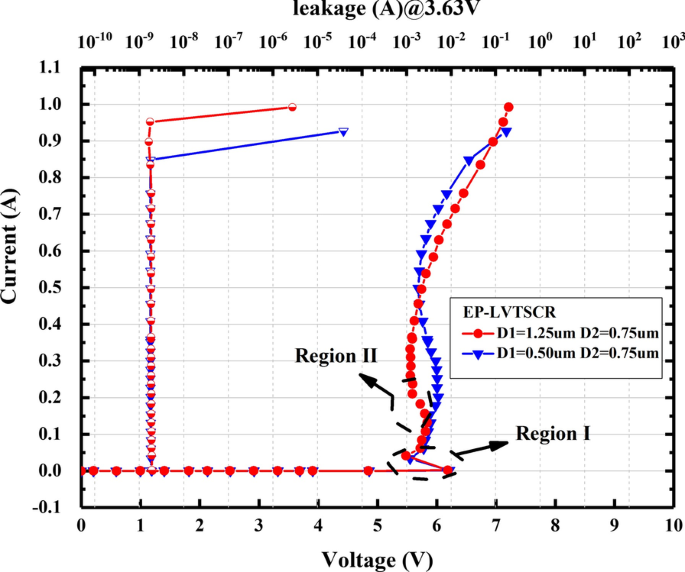

在本文中,通过修改设计变量 D1 和 D2 来优化所提出的 ESD 保护的电气特性。图 6 说明了具有两个不同 D1 的 EP-LVTSCR 的 TLP 测量结果。值得注意的是,由于器件开启期间的多重触发效应,EP-LVTSCR 的 I-V 曲线显示出两个回弹区域。第一个快速返回区域 I 表明触发路径的传导,如图 2a 所示,而区域 II 的第二个快速返回由 SCR 路径的开启引起。当 D1 从 1.25 减小到 0.5 um 时,I t2 减少约 0.1 A,第二次快速回弹中的保持电流增加约 0.17 A。这是因为阱电阻 R NW2 和 R PW2(图 1)随着 D1 的减小而减小,因此需要更多的电流来触发和维持 SCR 的传导。

两种不同D1下EP-LVTSCR的TLP I-V和漏电流测量

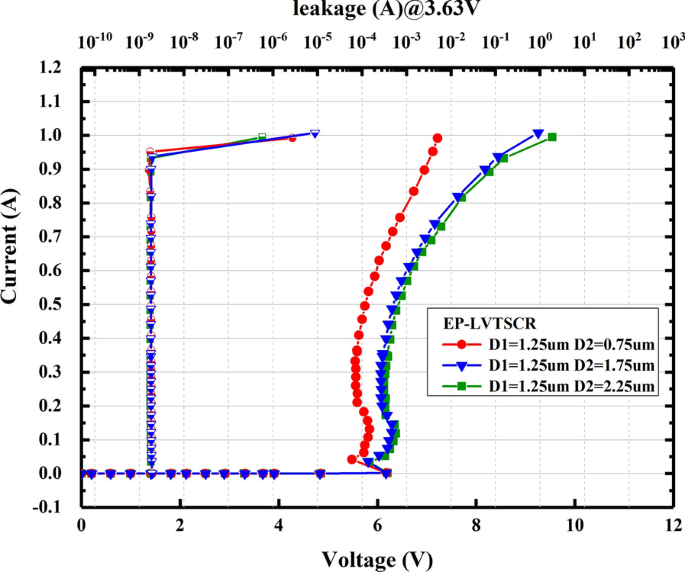

图 7 显示了具有三种不同 D2 的 EP-LVTSCR 的 TLP I-V 结果。当 D2 从 0.75 增加到 2.25 µm 时,ND 的镇流器电阻逐渐增加,导致支路电阻增加,并进一步增大 R 上,这可以通过图 7 中的 IV 特性曲线的斜率变化观察到。因此,V 随着 D2 的增加,h 从 5.5 V 升高到 5.8 V,It2 没有显着变化。

三种不同D2下EP-LVTSCR实测TLP I-V和漏电流

结论

一种称为 EP-LVTSCR 的增强型 ESD 器件采用 28 纳米 CMOS 技术设计和制造。还通过 TCAD 模拟演示了所提出设备的机制。与传统的 LVTSCR 相比,由于其改进的触发机制和支路传导效应,所提出的 EP-LVTSCR 具有 6.2 V 的较低触发电压和 5.5 V 的显着更高的保持电压。随着 V 的增加如此高 h,EP-LVTSCR 的故障电流仅降低了约 20%。此外,所提出的结构具有较低的导通电阻以及在 3.63 V 电压下约 2 nA 的可靠漏电流,因此非常适用于保护 2.5 V/3.3 V I/O 引脚。此外,EP-LVTSCR 还有望为 5 V 电源电路提供 ESD 保护,并受益于其可调节的保持电压特性。

数据和材料的可用性

本研究期间生成或分析的所有数据均包含在这篇已发表的文章中。

缩写

- ESD:

-

静电放电

- SCR:

-

可控硅整流器

- MLSCR:

-

改良横向SCR

- LVTSCR:

-

低压触发可控硅

- CMOS:

-

互补金属氧化物半导体

- IC:

-

集成电路

- V t1 :

-

触发电压

- V :

-

保持电压

- BJT:

-

双极结型晶体管

- R 上:

-

导通电阻

- I t2 :

-

故障电流

- TLP:

-

传输线脉冲

- TCAD:

-

技术计算机辅助设计

- SAB:

-

硅化物块

- V 次:

-

阈值电压

- DC:

-

直流电

纳米材料

- 微控制器和嵌入式系统的 IC 技术简介

- Maxim:具有 DC-DC 稳压器和浪涌保护的双 IO-Link 收发器

- 嵌入式设计与 FPGA:开发流程

- TRS-STAR:来自 avalue

- 三态电致变色器件的浸涂工艺工程和性能优化

- 通过纯 CMOS 逻辑工艺具有自抑制电阻开关负载的 RRAM 集成 4T SRAM

- 一种用于光伏器件的具有抗反射和超疏水特性的新型纳米锥簇微结构

- 在太赫兹范围内具有可切换吸收和偏振转换功能的多功能设备

- 具有低工作电压的基于原子层沉积的 HfAlOx 的 RRAM,用于计算内存应用

- WO3/p-Type-GR 层状材料促进光催化抗生素降解和机制洞察装置

- 自动化和网络安全:全面保护客户

- 高压PCB材料和设计