通过纯 CMOS 逻辑工艺具有自抑制电阻开关负载的 RRAM 集成 4T SRAM

摘要

本文报告了一种新颖的全逻辑兼容 4T2R 非易失性静态随机存取存储器 (nv-SRAM),具有自抑制数据存储机制,适用于低功耗/高速 SRAM 应用。这种新型 nv-SRAM 具有紧凑的单元面积和完整的逻辑兼容性,在 4T SRAM 中嵌入了两个 STI-ReRAM。数据可以通过交叉耦合的易失性结构进行读/写,以保持快速的访问速度。通过对电阻式随机存取存储器 (RRAM) 负载的独特自禁止操作,数据可以非易失性地存储在新的 SRAM 单元中,从而在数据保持期间实现零静态功耗。

背景

近年来,已经开发了各种低功耗静态随机存取存储器,以满足便携式设备和 IOT 应用上的计算系统的需求 [1,2,3,4,5,6]。随着 CMOS 技术缩小到纳米级,断态泄漏电流急剧增加,这导致易失性存储器模块的静态功耗恶化 [7, 8]。纳米级晶体管漏电流引起的静态功耗已成为低功耗SRAM发展的主要挑战之一。 [9,10,11]。多年来,已经提出了不同的单元结构或操作技术 [12,13,14,15,16] 来最小化 SRAM 的功耗。一些新提出的单元包含非易失性存储元件,例如电阻随机存取存储器 (RRAM) 和磁电阻随机存取存储器 (MRAM) [17,18,19,20],以在保持低运行的同时实现零保持功率处理易失性数据的能力和快速访问速度。然而,将非易失性存储元件添加到基于逻辑的 SRAM 阵列通常需要对标准逻辑平台进行额外的层和/或处理 [21,22,23]。这将不可避免地增加其开发过程的复杂性。此外,这些基于后端的 RRAM 和 MRAM 需要大型连接结构,由多个通孔和金属堆叠到 SRAM 单元组成。这些桥接结构增加了 SRAM 数据存储节点的寄生电容,影响了这些非易失性 SRAM 单元的访问速度 [24, 25]。在我们之前的工作 [26] 中,首次提出了一种新的零静态功耗 4T nv-SRAM,其 STI 侧壁 RRAM 位于 4T SRAM 的浮动存储节点旁边。在这封信中,这款具有非易失性数据存储、零保持能力和快速访问速度的 4T2R nv-SRAM 将针对嵌入式 NVM 应用进一步分析和优化。

方法

STI-ReRAM 单元结构

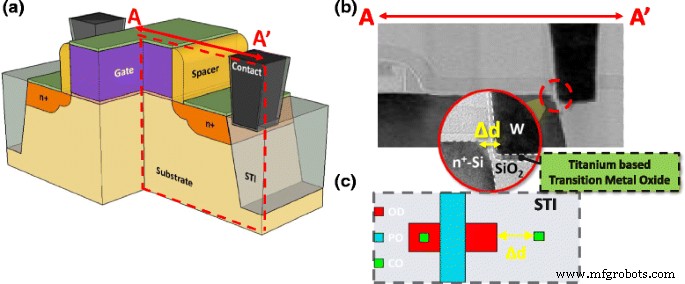

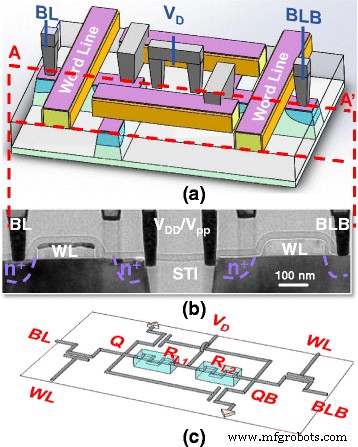

在图 1a 的 3D STI-RRAM 结构中,电阻存储节点由两个电极之间的过渡金属氧化物 (TMO) 组成,分别是 N+ 区和左右两侧的钨塞。如图 1b 中的 TEM 图片和图 1c 中的布局所示,通过将触点放置在与 N+ 区适当距离的 STI 区,钨塞下剩余的 SiO2 和阻挡层成为 TMO 膜并呈现阻变特性.

<图片>

一 紧邻 n+ 结的带有 STI-ReRAM 的 1T1R 单元的 3D 图示。 b 由过渡金属氧化物组成的电阻存储节点的相应 TEM 图片,在特殊放置的触点和选择晶体管的 n+ 区域之间形成。 c 布局

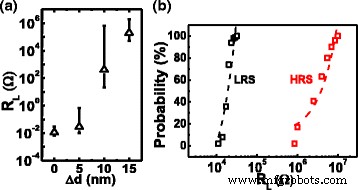

TMO 的厚度可以通过在接触和 N+ 扩散区之间选择适当的间距 Δd 来控制。根据图 2a 中的测量结果,初始电阻水平和绘制距离 Δd 之间存在正相关,分别由定义 STI 和接触区域的掩模确定。在接下来的研究中,选择 Δd 等于 10 nm 的 RRAM 是因为其较低的形成电压和在低电阻状态 (LRS) 和高电阻状态 (HRS) 中的优选 RL 分布,如图 2b 中总结的。在设置/形成操作期间通过适当的字线 (WL) 电压控制,设置电流可以由选择晶体管局部钳位,从而实现更好的耐久性性能。

<图片>

一 不同△d下STI-RRAM样品测得的初始电阻。 b STI-RRAM在高低阻状态下复位/置位后负载电阻的累积概率

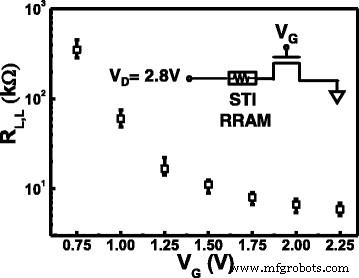

图 3 中的数据进一步表明,LRS 中的读取电流电平可以很好地由栅极电压 VG 控制。在 VD =2.8 V 形成期间,选择晶体管会限制器件设置为 LRS 后通过 STI-RRAM 的最大电流。随后的 LRS 状态电阻水平与局部钳位电流成反比,这已在各种基于 TaO 的 RRAM 器件中发现 [27, 28]。

<图片>

负载电阻水平、RL、L 和设置期间施加的栅极电压之间的相关性。数据表明通过设置不同的选择栅极电压可以得到不同的RL,L

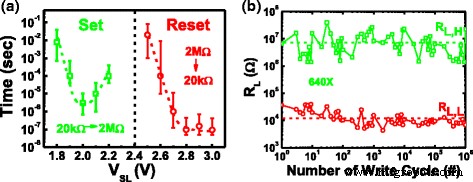

为保证 STI-RRAM 的阻变特性,我们对置位时间和复位时间进行了测试,如图 4a 所示。当 VSL =2 和 2.8 V 时,可以分别优化设置和复位操作。 RRAM 耐久性测试总结在图 4b 中。采用增量步进脉冲编程算法,其读取窗口在100万次循环后仍能保持稳定。

<图片>

一 总结了设置时间和重置时间与 VPP。 b 使用增量步进脉冲编程算法的STI-RRAM百万周期耐久性测试结果

非易失性 SRAM 概念

图 5 中的 3D 图示显示了新提出的 4T2R nv-SRAM 单元结构及其沿 AA' 切割线的相应横截面 TEM 图片。两个 STI-RRAM 用作非易失性存储节点和加载电阻器,它们夹在 Q 和 QB N+ 扩散区之间,并通过适当的间距设计紧密地落在 STI 边缘上的触点。 TEM 照片显示了隔离区左侧和右侧的结构良好的 STI-RRAM,并形成了一个相当紧凑的单元,这些非易失性存储节点紧密放置在晶体管的同一层。

<图片>

一 提议的 4T2R nv-SRAM 单元结构和 b 的 3D 图示 相应的横截面 TEM 图片。 c SRAM单元的电路原理图以两个RRAM电阻作为负载器件

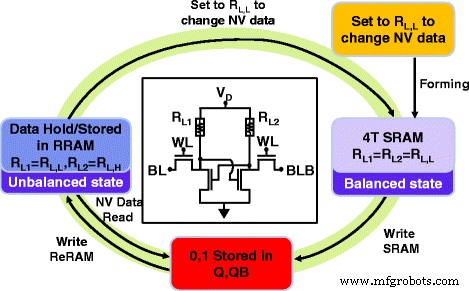

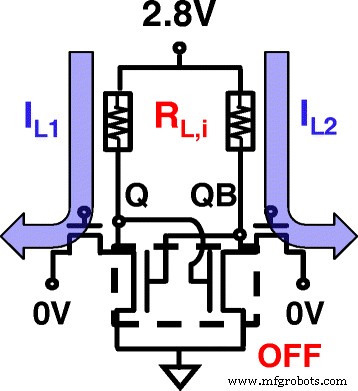

建议的 4T nv-SRAM 可以在易失性和非易失性模式下运行。其四种不同的状态及其运行方案如图6所示。

<图片>

nv-SRAM单元电路原理图及其对应的易失性和非易失性SRAM操作切换流程图

在其初始状态,STI-RRAM 通常承载 10 8 的电阻水平 Ω,而 TMO 薄膜完好无损。通过覆盖成型操作,nv-SRAM 单元可以在 VD =2.8 V 的情况下以逐块方式同时初始化。 RL1 和 RL2(分别在左侧和右侧的负载电阻)都初始化为 RL,L。通过在成型操作期间提供不同的 WL 电压,可以控制 20~370 kΩ 的最终 RL,L 电平。然后电池达到平衡状态,这意味着两个负载电阻处于相同状态。在这种状态下,该单元现在可以用作典型的 4T2R SRAM,通过将数据存储在交叉耦合锁存器中,以传统方式处理易失性数据。

为了非易失性地存储数据,互补锁存数据可以通过该单元中继承的自抑制机制存储到 RRAM 上。当数据成功存储在 RRAM 对中时,可以关闭电源以进行永久数据保持。要访问存储的状态,只需将 VDD 重新应用于阵列。非易失性数据将自动恢复到 Q 和 QB 节点,并可通过常规 SRAM 读取模式访问。最后,为了刷新非易失性数据,对 SRAM 阵列应用全面设置操作,使阵列恢复到其平衡状态。

结果与讨论

电分析

表1总结了不同阶段之间转换的操作条件。

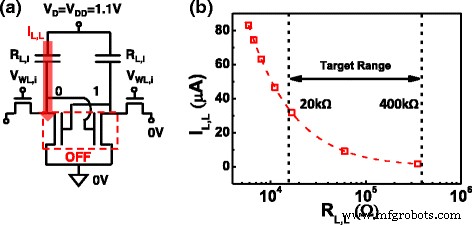

在块或阵列的初始化过程中,通过设置不同的 WL 电压可以获得不同的 RL,L 电平。考虑到稳定性和工作电压,本研究首先针对 20 至 400 kΩ 之间的 RL、L 电平进行研究。对应的 WL 电压为 0.75 至 1.25 V,由此产生的负载电阻呈线性下降,如图 3 所示。正如预期的那样,较低的 RL,L 电平将导致更高的待机电流,见图 7。但是,RL,L 必须保持足够低以确保两个电阻状态之间的大数据窗口放大。需要考虑静态、动态和非易失性数据窗口,以进一步优化目标RL,L,由初始化条件设置。

<图片>

一 处于保持状态的 4T2R SRAM 单元。 b 正如预期的那样,通过选择较高的 RL,L 可以有效降低保持期间的负载电阻水平 IL,L

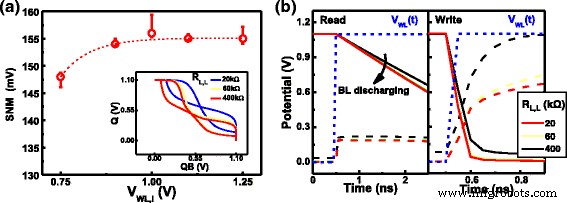

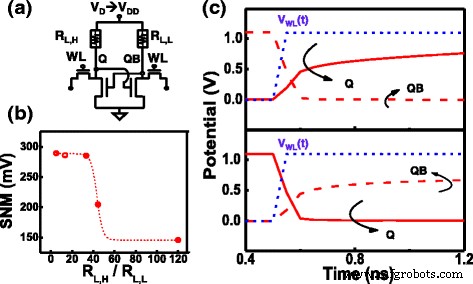

首先研究平衡状态下 nv-SRAM 的静态和动态特性,考虑到由不同条件初始化的单元。在图 8 中,由不同 WL 电压初始化的单元的多个蝶形曲线获得的静态噪声容限 (SNM)。数据显示,当负载电阻在目标范围内时,RL、L 电平对平衡单元的读取余量的影响最小。图 8a 总结了在不同初始化条件下处于平衡状态的多个单元格的 SNM 分布。整体 SNM 从单元到单元都保持相当稳定,同时可以在 WL 电压低于 VDD 的情况下建立合理的读取裕度,这对低功耗应用有利。为了研究该单元在平衡状态下的动态读写特性,图 8b 总结了写入“1”和“0”的瞬态响应。发现较高的 RL,L 会降低 Q、QB 节点的上拉速度,这会略微增加读取和写入操作期间的瞬态时间。但是,响应速度仍在预期范围内。以上数据表明,在平衡状态下,这款4T2R nv-SRAM可以像传统SRAM一样处理易失性数据。

<图片>

一 在初始化期间具有不同 WL 电压的建议 SRAM 单元的读取静态噪声容限 (SNM)。合理的SNM可以保持在20~400 kΩ的相当大的RL,L范围内。 b 平衡负载条件下单元的动态读取和写入特性显示在纳秒内的良好响应时间。较高的 RL,L 会略微降低写操作期间的上拉速度

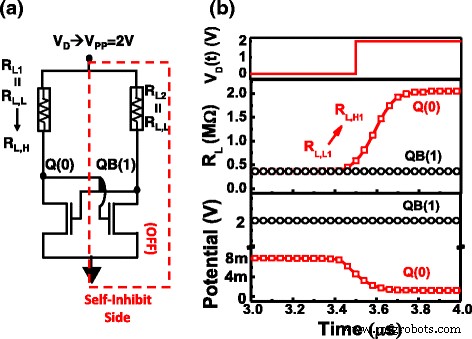

为了在 STI-RRAM 对中存储数据,该单元只允许对负载电阻对中的一个 RRAM 进行自选择性复位,这允许通过向电源节点施加更高的 Vpp 电压来非易失性地写入数据细胞块均匀。一旦锁存数据被存储到 Q 和 QB 节点,通过与 RRAM 交叉耦合结构中的自抑制机制实现非易失性写入,如图 9a 所示。只有 Q 节点低电压的 RRAM 一侧会被重置为 RL,H。由于下拉晶体管被低 VQ 关断,另一支路上的电流几乎为零。

<图片>

一 通过重置两个 RRAM 的一侧在非易失性数据写入期间的自抑制机制的说明。 b RL 和 Q、QB 电位的动态变化验证自抑制向 RRAM 写入锁存数据

当 VPP 脉冲施加到电源节点时,数据存储在 RRAM 对中。写入非易失性数据时,RL 的动态切换和 Q、QB 电位的瞬态响应总结在图 9b 中。测量数据表明,要成功地在一侧选择性地重置 STI-RRAM,Vpp =2 V 下的 300 ns 脉冲就足够了。为了确保当电池处于不平衡状态时仍然不影响易失性操作,如图 10a,具有不同 RL,H/RL,L 比的电池的 SNM 分布总结在图 10b 中。发现状态之间的低电阻比不会降低保持 SNM。为了确保具有不平衡负载的单元,特征在于向这样的单元动态写入数据。数据显示两种状态都可以成功写入,克服了2 M/400 k的初始不平衡电阻比,如图10c所示。

<图片>

一 不平衡负载时的交叉耦合结构。 b 初始化期间不同 WL 电压的静态噪声容限。 c 两种不同数据状态的动态写入。不平衡RL,L =400 kΩ也可以写成

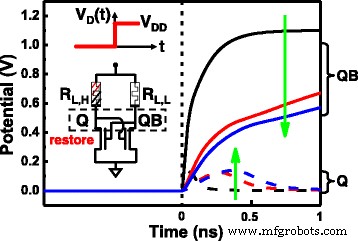

要将之前存储在 RRAM 中的易失性数据加载回,可以简单地将 VDD 施加到电源节点,RRAM 中的不平衡负载会自行恢复到 Q 和 QB 的锁存节点,如图 11 所示。

<图片>

从不平衡的 RRAM 负载状态恢复存储在 Q 和 QB 中的非易失性数据。 Q和QB节点在纳秒内恢复上电后均能恢复电位

寄生效应与比较

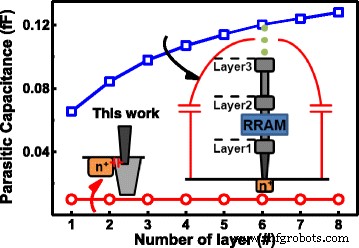

通过将完全逻辑兼容的 STI-RRAM 整合到这个新的 SRAM 单元中,该单元可以通过大多数标准逻辑工艺轻松实现,而无需添加掩膜层和工艺步骤。这一特性可以极大地增强其在许多 IC 系统所需的各种非易失性存储器 IP 模块中的应用和灵活性。此外,与之前报道的其他需要后端 (BEOL) 非易失性组件的 nv-SRAM [29,30,31] 相比,提议的 4T2R nv-SRAM 具有更小的寄生电容。为了将 Q 和 QB 节点从 Si 表面连接到这些 BEOL RRAM 或 MRAM,需要多层金属和通孔层。这些大的桥接结构会导致显着的寄生 RC 效应。 SRAM单元内部节点引入的大寄生电容会严重影响器件的响应时间。

为了比较对这些的寄生效应,基于布局后模拟的估计研究了 nv-SRAM。假设所有单元都由相同的标准 CMOS 技术实现,锁存节点上的寄生电容会随着需要大桥接结构的单元的金属层数量的增加而增加。对于使用 STI-RRAM 的新型 nv-SRAM,锁存节点上的总电容几乎没有增加。此外,它与适用于特定电路的金属层的数量无关。为了进一步研究寄生电容对SRAM速度的影响,[29,30,31]中提出的SRAM单元的模拟动态响应与这项工作在图12中进行了比较。

<图片>

参考文献 [30] 和基于 40 nm CMOS 技术的这项工作的 nv-SRAM 单元锁存节点上的寄生电容,发现随着金属层数量的增加,寄生电容显着增加

这种嵌入式 nv-SRAM 的寄生电容小得多,可以在 SRAM 单元的动态读取操作期间实现更快的响应时间。避免了连接桥内部电容较大对基于逻辑的SRAM阵列响应时间的影响。

表 2 比较了之前报告的与后端 RRAM 或 MRAM 相结合的非易失性 SRAM 的主要特性以及这项工作。尽管状态切换电压更高,但基于 STI-RRAM 的 nv-SRAM 在 SRAM 单元内的内部锁存节点上的寄生电容要小得多,并且具有完全的逻辑兼容性。

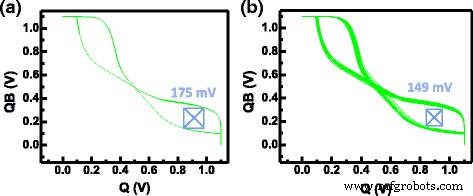

变化引起的静态噪声容限下降

为确保稳定的 SNM 单元受到工艺变化的影响,在以下研究中考虑了 RRAM 电阻水平和晶体管阈值电压 VT 的波动:已知 VT 中的不匹配会通过缩放技术导致 SRAM 中的 SNM 偏移 [32, 33 ]。此外,它还可能导致不同的设定顺从电流,进而导致两个 RL、L 的电阻水平的变化增加。如图 13 所示,不同的 VT 导致 STI-RRAM 单元中不同的初始化顺从电流,导致 RL、L 进一步失配。为了分析 VT 变化对 SNM 的影响,我们假设 VT 是一个具有均值和变化的高斯随机变量,基于之前的报告 [34]。通过蒙特卡罗模拟,在图 14a 中总结了受 RL、L 变化影响的蝴蝶曲线的分布。当同时考虑 RL、L 和 VT 的变化时,观察到 SNM 窗口显着变窄,如图 14b 所示。在未来的研究中需要解决 nv-SRAM 中增加的可变性。

<图片>

VT 变化导致不同的初始化顺应性 IL,1 和 IL,2

<图片>

蒙特卡罗模拟的蝴蝶曲线比较 a 引起的 SNM 退化 初始化后 RL、L 的变化和 b RL、L 和 VT 的变化

结论

一种新型的基于 4T2R STI-RRAM 的非易失性 SRAM 与 CMOS 逻辑工艺完全逻辑兼容,已在 40 nm 技术节点的纯 CMOS 逻辑工艺中成功展示,无需额外的掩模或步骤。此 nv-SRAM 单元具有非易失性数据的自抑制、自恢复机制、锁存节点上的小寄生电容以及数据保持期间的零静态功耗。这些优越的特性使基于 STI-RRAM 的 nv-SRAM 成为未来低功耗/高速逻辑非易失性存储器应用的有前途的解决方案。

纳米材料