采用 ZrO2 电介质的 Ge N 沟道 MOSFET 可实现更高的迁移率

摘要

展示了具有 ZrO2 栅极电介质的高迁移率 GenMOSFET,并与具有臭氧 (O3) 处理、O3 后处理和未经 O3 处理的不同界面特性的晶体管进行了比较。发现通过 O3 处理,具有 0.83 nm EOT 的 ZrO2 电介质的 Ge nMOSFET 获得峰值有效电子迁移率 (μ eff) 为 682 cm 2 /Vs,在中等反转电荷密度(Q 投资)。另一方面,O3 后处理与 Al2O3 界面层可以显着提高-μ eff,达到约 50% μ 与中等 Q 下的 Si 通用迁移率相比,效率提高 5 × 10 12 的倒数 cm −2 .这些结果表明了 ZrO2 电介质在高性能 Gen MOSFET 中的潜在应用。

背景

与硅器件相比,锗 (Ge) 具有更高的载流子迁移率和更低的加工温度的优势。这些使 Ge 成为超大规模 CMOS 逻辑器件和薄膜晶体管 (TFT) 应用的替代品,作为三维集成电路的顶层 [1,2,3]。在过去的几年中,人们在 Ge p 沟道金属氧化物半导体场效应晶体管 (MOSFET) 的表面钝化、栅极电介质和沟道工程方面付出了巨大的努力,这有助于显着提高器件的电气性能。 p 通道设备。

但对于 Ge n 沟道 MOSFET,低有效载流子迁移率 (μ 由栅叠层不良界面层引起的 eff) 强烈限制了器件的性能。各种表面钝化技术,包括 Si 钝化 [1]、等离子体后氧化 [4] 和 InAlP 钝化 [5] 以及几种高 κ 电介质,包括 HfO2、ZrO2 [6,7,8]、Y2O3 [9] 和 La2O3 [10] 已在 Gen MOSFET 中探索以提升电子 μ 效果已经证明,由于 GeO2 界面层可以与 ZrO2 层反应和混合,与 Ge 通道集成的 ZrO2 电介质可以提供稳健的界面[7]。一个不错的洞μ Ge p 沟道晶体管中已经报道了 eff [6,7,8],而电子 μ 仍有很大的改进空间 为他们的同行效力。

在这项工作中,制造了具有 ZrO2 栅极电介质的 GenMOSFET,以实现改进的 μ 在整个反型电荷密度范围内对 Si 的 eff (Q 投资)。 Ge晶体管在电子μ上获得了50%的改进 eff 与中等 Q 下的 Si 通用迁移率相比 inv 5.0 × 10 12 cm −2 .

实验

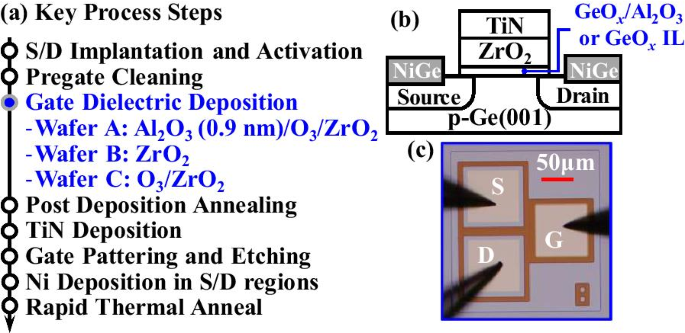

在电阻率为 0.136–0.182 Ω cm 的 4 英寸 p-Ge(001) 晶片上制造 Ge nMOSFET 的关键工艺步骤如图 1a 所示。源/漏(S/D)区以1 × 10 15 的剂量注入磷离子 cm −2 和 30 keV 的能量,然后在 600°C 下进行掺杂激活退火。栅极前清洗后,将 Ge 晶片装入原子层沉积室以形成栅极介电层:Al2O3/O3 氧化/ZrO2、ZrO2 或 O3 氧化/ZrO2 用于晶片 A、B 或C、分别。对于晶片 A,在 O3 氧化期间使用 0.9 nm Al2O3 来保护通道表面。对于晶片 A 和 C,在 300°C 下进行 O3 氧化 15 分钟。对于所有晶片,ZrO2 的厚度为 ~ 3.3 nm。随后,通过物理反应溅射沉积 TiN(100 nm)栅极金属,并使用光刻图案化和反应离子蚀刻来形成栅电极。之后,在 S/D 区域沉积 25 nm 厚的 Ni 层。最后,在 350°C 下进行 30 秒的后金属化退火 (PMA) 以形成锗化镍并改善界面质量。制作的晶体管的示意图和显微镜图像分别如图 1b、c 所示。

<图片>

一 制造 Gen MOSFET 的关键工艺步骤。 b 横截面示意图和c 所制备器件的显微图像

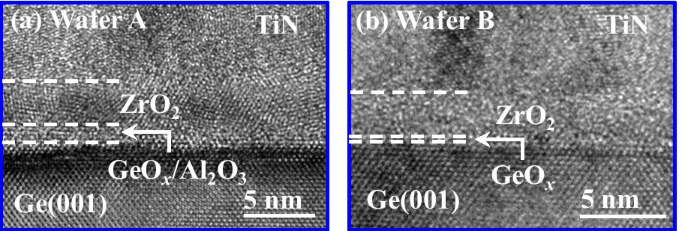

图 2a、b 分别显示了晶圆 A 和 B 上栅极堆叠的高分辨率透射电子显微镜 (HRTEM) 图像。 Al2O3/GeOx的统一厚度 晶圆 A 的界面层 (IL) 为 ~ 1.2 nm,表明 0.2–0.3 nm GeOx .对于晶圆 B 上的器件,超薄 GeOx IL得到了实验证明[7]。

<图片>

a 的 HRTEM 图像 TiN//ZrO2/Al2O3/GeOx /Ge, b TiN/ZrO2/GeOx 晶圆 A 和 B 上的器件分别为 /Ge 堆栈

结果与讨论

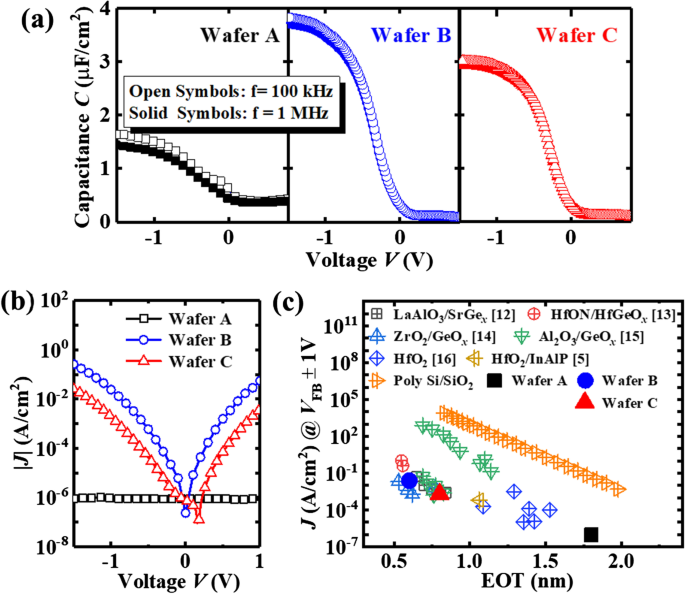

测得的电容 (C ) 和漏电流 (J ) 晶圆 A、B 和 C 上 Ge MOS 电容器的特性分别在图 3a、b 中进行测量和显示。晶片 A、B 和 C 上器件的等效氧化物厚度 (EOT) 分别提取为 1.79、0.59 和 0.83 nm。假设 GeOx 通过比较晶片 B 和 C,IL 为晶片 A 和 C 提供了 ~ 0.25 nm 的额外 EOT,3.3 nm ZrO2 贡献了 ~ 0.6 nm 的 EOT,κ 值为 ~ 21.8,这与之前报道的非晶 ZrO2 值一致[11].这些推导出的结果也证实了 GeOx 中的厚度 晶圆 B 上的 IL 可以忽略不计。

<图片>

一 测量的 C 作为电压 V 的函数 晶圆 A、B 和 C 上 Ge pMOS 电容器的特性。b J 对比 V 设备的曲线。 c J 的基准测试 (提取于 V FB ± 1 V) 的 Ge MOS 电容器在这项工作中与从文献中获得的类似偏置条件的数据相比较

GeOx /Al2O3 IL 用于晶圆 A 和 GeOx 晶圆 C 的 IL 分别产生 ~ 1.2 和 ~ 0.25 nm 的 EOT。通过降低 IL 厚度或提高界面质量,以及通过一些表面钝化(例如 NH3/H2 等离子体处理)提高 ZrO2 的介电常数,可以进一步降低器件的 EOT [6]。图 3c 比较了 J 将本工作中 Gen MOSFET 的 EOT 特性与其他报道的 Ge 器件的值进行比较 [5, 12,13,14,15,16,17]。还观察到结果与报道的具有相同趋势的超薄EOT的Ge MOS一致,表明图3b所示漏电流的差异应主要归因于EOT的差异。

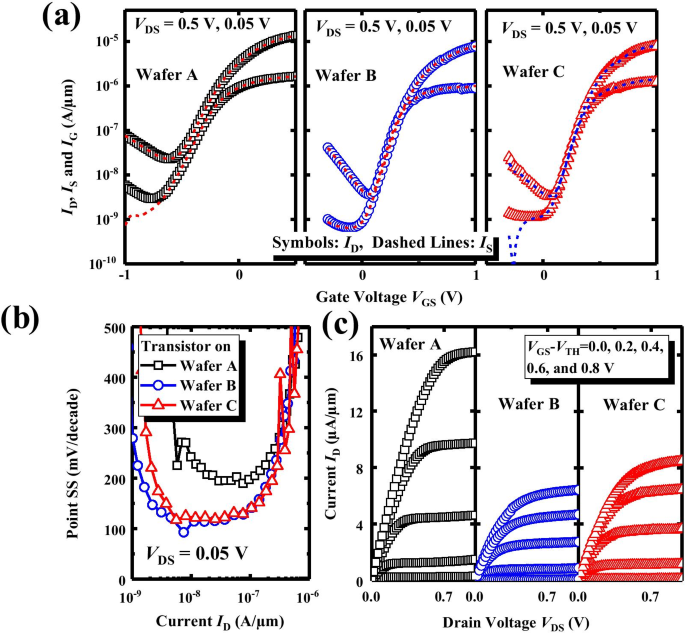

图 4a 显示了测得的漏极电流 (I D) 和源电流 (I S) 与栅极电压 (V G) 来自晶圆 A、B 和 C 的 Gen MOSFET 的曲线。所有晶体管的栅极长度为 L G 为 4 μm,栅极宽度 W 100 微米。点亚阈值摆幅 (SS),定义为 dV G/d(logI D),作为 I 的函数 图 4a 中晶体管的 D 曲线已计算并显示在图 4b 中。澄清晶片 A 上的晶体管表现出退化的 I D 漏底和 SS 与晶圆 B 和 C 上的器件相比。除了晶圆 A 上器件的 EOT 增加会导致 SS 增加,这些现象应部分归因于具有 Al2O3 插入层的器件具有更高密度的界面陷阱 (D 它)与晶圆 B 和 C 相比,在 Ge 通道的带隙内。

<图片>

一 测量 I D 和 I S 与 V 晶圆 A、B 和 C 上的 GennMOSFET 的 GS 曲线。b 点 SS 作为 I 的函数 D 为晶体管。 c 我 D–V D 特性表明,与晶圆 B 和 C 上的器件相比,晶圆 A 上的 Ge nMOSFET 具有更高的驱动电流

图 4c 显示了测量的输出特性,即 I D–V 不同栅极过驱动值的 D 曲线 |V G–V TH|的器件表明,与晶片 B 和 C 上的器件相比,晶片 A 上的 Ge 晶体管实现了显着改善的驱动电流。这里,V TH 定义为 V GS 对应于 I D 的 10 −7 A/微米。考虑到 S/D 形成的相同条件,boosted I 晶圆 A 上晶体管的 DS 表示较高的 μ 效率 [18,19,20,21]。 Al2O3 层没有导致 D 的降解 其性能接近Ge沟道导带。

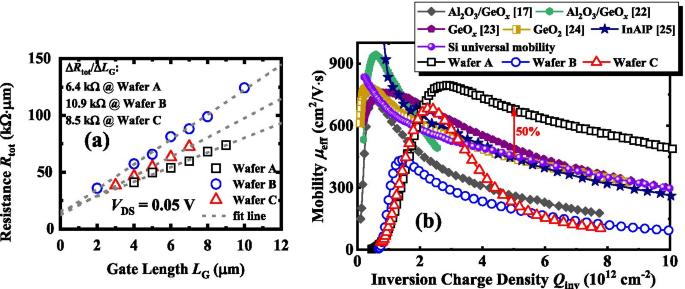

图 5a 显示了总电阻 R 作为 L 的函数的 tot G 用于具有 ZrO2 电介质且 L 的 Ge nMOSFET G 范围从 2 到 10 µm。 R 的值 在 0. 6 V 和 V 的栅极过驱动下提取 tot D 为 0.05 V。S/D 电阻 R 利用在 y 处相交的拟合线,晶体管的 SD 被提取为 ~ 13.5 kΩ μm -轴。类似的R SD与PMA和S/D形成的相同过程一致。通道电阻R 器件的 CH 值由拟合线的斜率获得,即 ΔR 总/ΔL G,可用于计算μ Gen MOSFET 的 eff 特性。为了评估界面质量,界面陷阱密度 (D 它)根据希尔的方法[17]通过以下等式提取:

$$D_{{{\text{it}}}} =\frac{{2G_{{{\text{m}}\max }} /\omega }}{{qA\left[ {\left( {\ frac{{G_{{{\text{mmax}}}} }}{{\omega C_{{{\text{ox}}}} }}} \right) + \left( {1 - C_{{\ text{m}}} /C_{{{\text{ox}}}} \right)^{2} } \right]}}$$其中 q 是电子电荷,A 是电容器的面积,G m,max 是被测电导的最大值,与其对应的电容C 米,ω 是角频率,C ox 是栅极氧化层电容。 D 它的值计算为 3.7、3.2 和 2.3 × 10 12 eV −1 cm −2 分别为晶圆A、B和C上的器件。

已知计算值对应于midgap D 它。在晶圆 A 上使用 Al2O3 IL 的器件具有更高的中隙 D 它与晶圆 B 和 C 上的器件进行比较。这与图 1 和图 2 中的结果一致。 3a 和 4a,以及较高的中间隙 D 它会导致晶片 A 中更大的耗尽电容分散,从而导致 I 的更高泄漏电流 DS 与其他两个晶圆的比较。注意晶圆 A 应该具有较低的 D 由于其较高的μ,它靠近导带隙 晶圆 B 和 C 上的效率。

<图片>

一 R tot 与 L 晶圆 A、B 和 C 上的 Ge nMOSFET 的 G 曲线。在 y 轴处相交的拟合线和线性拟合线的斜率用于提取 R SD 和 R CH,分别。 b μ 这项工作中的 Ge nMOSFET 的 eff 与先前公布的无应变 Ge 晶体管的结果。晶圆 A 上的器件显示出改进的 μ 在 Q 的整个范围内比 Si 的通用迁移率更有效 输入

众所周知,μ eff 是 Gen MOSFET 中高驱动电流和跨导的瓶颈。这里,μ eff 可以通过 \(\mu_{{{\text{eff}}}} =1/[WQ_{{{\text{inv}}}} (\Delta R_{{{\text{tot}}}} } /\Delta L_{{\text{G}}} )]\),其中 ΔR 总/ΔL G 是 R 的斜率 tot 与 L G 如图 5a 所示。 问 inv 可以通过对测量的 C 积分获得 inv–V G 曲线。在图 5b 中,我们比较了 μ eff 与 Q 晶圆 A、B 和 C 上的 GenMOSFET 与之前在 [18, 22,23,24,25] 中报道的那些的 inv。提取峰μ 晶片 A 和 C 上晶体管的 eff 值为 795 和 682 cm 2 /V s 分别为 433 cm 2 /V 秒。具有 Al2O3 IL 的 Gen MOSFET 实现了显着改善的 μ eff 与晶圆 B 或 C 上的晶体管相比,[18, 22,23,24,25] 中的器件在高场中,以及整个 Q 中的 Si 通用迁移率 输入范围。在 Q 5 × 10 12 的倒数 cm −2 , 50% μ 与 Si 通用迁移率相比,晶圆 A 上的器件实现了 eff 增强。这表明通过保护通道表面以防止 ZrO2 和 GeOx 的混合 使用 Al2O3,实现了栅极绝缘体和 Ge 之间的高质量界面,以提高迁移率特性,这在之前对具有超薄 EOT 的 Ge MOSFET 的研究中也有报道[26]。 μ 晶片 C 上晶体管的 eff 在 Q 处高于 Si 通用 2.5 × 10 12 的inv cm −2 ,虽然它随着 Q 的增加而迅速衰减 输入范围。这说明在ZrO2 沉积之前使用O3 氧化会在一定程度上改善界面质量;然而,它并没有导致足够平坦的通道表面来有效抑制载流子在高 Q 下的表面粗糙度散射 由于 ZrO2 和 GeOx 的混合而导致的 inv ,因为据报道,在混合过程中产生的氧空位会增加短程有序 (SRO) 粗糙度 [27]。优化 O3 氧化过程或降低 Al2O3 IL 厚度可以使 Ge 晶体管实现降低的 EOT,同时保持较高的 μ 高 Q 时的 eff 反诉

结论

研究了栅极介电结构和形态对 Gen MOSFET 电气特性的影响。 Al2O3/ZrO2 栅极电介质提供显着改善的 μ eff 与 Si 通用迁移率相比。 μ 可以通过在 ZrO2 和 Ge 通道之间插入 Al2O3 层来提高 eff,但这不可避免地会导致更大的 EOT。在 ZrO2 沉积之前,Ge 表面 O3 氧化的不含 Al2O3 的 Ge nMOSFET 达到峰值 μ 682 cm 2 的效果 /V s 在类似的 Q 下高于 Si 反诉

数据和材料的可用性

本文包含支持本文结论的数据集。

缩写

- 哥:

-

锗

- 氧化锆:

-

二氧化锆

- Al2O3 :

-

氧化铝

- O3:

-

臭氧

- Si:

-

硅

- PMA:

-

后金属退火

- PDA:

-

沉积后退火

- IL:

-

界面层

- TiN:

-

氮化钛

- MOSFET:

-

金属氧化物半导体场效应晶体管

- ALD:

-

原子层沉积

- 高频:

-

氢氟酸

- µ 效果:

-

有效载流子迁移率

- PPO:

-

等离子后氧化

- SS:

-

亚阈值摆动

- CET:

-

电容等效厚度

- EOT:

-

等效氧化层厚度

- Qinv:

-

反转电荷密度

- HRTEM:

-

高分辨透射电子显微镜

- Ni:

-

镍

- GeOx :

-

氧化锗

- I DS :

-

漏电流

- V 高:

-

栅极电压

- V :

-

阈值电压

纳米材料

- 利用染料和颜料实现可持续性

- KUHMUTE 通过 SLS 3D 打印重新设计移动性

- 通过介电超表面扩大带宽完成太赫兹偏振控制

- 无合规性 ZrO2/ZrO2 − x /ZrO2 具有可控界面多态切换行为的电阻式存储器

- 氮化处理的基于 HfO2 的 RRAM 中的传导机制和改进的耐久性

- 通过微波退火增强原子层沉积的 Al2O3/ZrO2/Al2O3 MIM 电容器的介电增强

- 具有非晶 Si 钝化的高迁移率 Ge pMOSFET:表面取向的影响

- 使用富氢 Al2O3 电介质的具有极低热预算的高性能 a-InGaZnO 薄膜晶体管

- 具有 ZrO2 电介质的高迁移率 Ge pMOSFET:后退火的影响

- 4.6 版改进 Protocase Designer 的 6 种方法

- 通过金属化实现非凡的表面处理

- 使用铜钨电极提高耐磨性