T 形栅极双源隧道场效应晶体管的模拟/射频性能

摘要

在本文中,提出并通过 TCAD 仿真研究了一种基于硅的 T 形栅极双源隧道场效应晶体管 (TGTFET)。作为对比研究,讨论了 TGTFET、LTFET 和 UTFET 的结构、特性和模拟/RF 性能。 T形栅极引入的栅极重叠可以提高隧道结的效率。 TGTFET 中的双源区可以增加导通电流 (I ON) 通过提供双倍的隧道结区域。为了进一步提高器件性能,TGTFET中引入了n+pocket,进一步提高了带间隧穿率。仿真结果表明 TGTFET 的 I ON 和开关比 (I ON/I OFF) 达到 81 μA/μm 和 6.7 × 10 10 在 1 V 栅极到源极电压 (V G)。 TGTFET 的平均亚阈值摆幅 (SSavg,从 0 到 0.5 V V g) 达到 51.5 mV/dec,TGTFET 的最小亚阈值摆幅 (SSmin,在 0.1 V V g) 达到 24.4 mV/dec。此外,发现 TGTFET 对漏极诱导势垒降低 (DIBL) 效应具有很强的鲁棒性。研究了掺杂浓度、几何尺寸和外加电压对器件性能的影响,以制定 TGTFET 设计指南。此外,跨导 (g m), 输出电导 (g ds), 栅源电容 (C gs), 栅漏电容 (C gd),截止频率 (f T),TGTFET 的增益带宽 (GBW) 在 0.5 V 漏源电压 (V d) 分别。受益于结构优势,TGTFET 获得了比 UTFET 和 LTFET 更好的 DC/AC 特性。总之,相当好的性能使 TGTFET 成为下一代低功耗和模拟/射频应用非常有吸引力的选择。

背景

金属氧化物半导体场效应晶体管 (MOSFET) 的按比例缩小显着改善了集成电路 (IC) 的功耗、开关特性、电路功能和 IC 密度 [1, 2]。但电源电压的缩放与关态漏电流的降低之间不可调和的矛盾(I OFF) 最终会导致无法接受的高功耗 [3]。同时,由短沟道效应 (SCE) 引起的可靠性下降变得越来越严重 [4, 5]。为了解决这些问题,降低亚阈值摆幅(SS)和器件的电源电压是有效的。基于带间隧道机制,隧道场效应晶体管 (TFET) 达到低于 60 mV/dec 的亚阈值摆幅 (SS),可以有效降低电源电压 [6,7,8,9,10] .此外,由于源极附近隧道结的存在,TFET通常具有较小的栅源电容(C gs) [1, 11] 有利于器件频率性能。

最近的研究表明,TFET 似乎是未来低功率应用 [12,13,14,15,16] 和模拟/RF 应用 [17,18,19] 的有希望的候选者。然而,由于有效隧穿面积小,有限的隧穿电流成为传统 P-I-N TFET 的固有缺点,导致低通态工作电流 (I 在)。为了提高TFET性能,近年来提出了许多新结构[20,21,22,23,24,25]。受益于凹槽栅极,L 形隧道场效应晶体管 (LTFET) [23, 24] 和 U 形隧道场效应晶体管 (UTFET) [25] 已被提出以获得高 I ON 具有紧凑的器件结构。但是LTFET和UTFET还有很大的提升空间,需要花更多的精力研究这些器件的模拟/射频性能。

本文提出了一种双源T形栅极双源隧道场效应晶体管(TGTFET),并通过TCAD仿真进行了研究。与LTFET和UTFET相比,设计的TGTFET可以使隧道结面积增加一倍。设计的 T 形栅极引入的栅极重叠可以提高带间隧穿率(BBT 率)。仿真结果表明,所提出的 TGTFET 获得了更高的 I ON (8.1 × 10 − 5 V 处的 A/μm d =1 V) 在相同条件下比 LTFET 和 UTFET。两个 SSmin(在 V g =0.1 V) 和 SSavg (0~0.5 V V g) 的 TGTFET 低于 60 mV/dec(分别为 24.4 mV/dec 和 51.5 mV/dec)。 TGTFET 获得更好的输入/输出特性 (g m =232 μS/μm,g ds =214 μS/μm) 比 UTFET 和 LTFET。此外,还详细讨论了 TGTFET、UTFET 和 LTFET 的电容特性。最后,TGTFET 获得了更好的模拟/射频性能 (f 与 UTFET 和 LTFET 相比,T =11.9 GHz 和 GBW =2.3 GHz)。因此,可以获得性能相当好的TGTFET。 本文的结构如下:“方法”部分包括TGTFET、LTFET [23, 24]和UTFET [25]的结构和参数的描述] 以及 TCAD 模拟方法。 “结果和讨论”部分包括对模拟结果的描述。在本节中,研究了 TGTFET 的机制、特性和模拟/RF 性能,并与 LTFET 和 UTFET 进行了比较。也详细分析了器件参数对TGTFET的影响。 “结论”部分对本文进行了总结。

方法

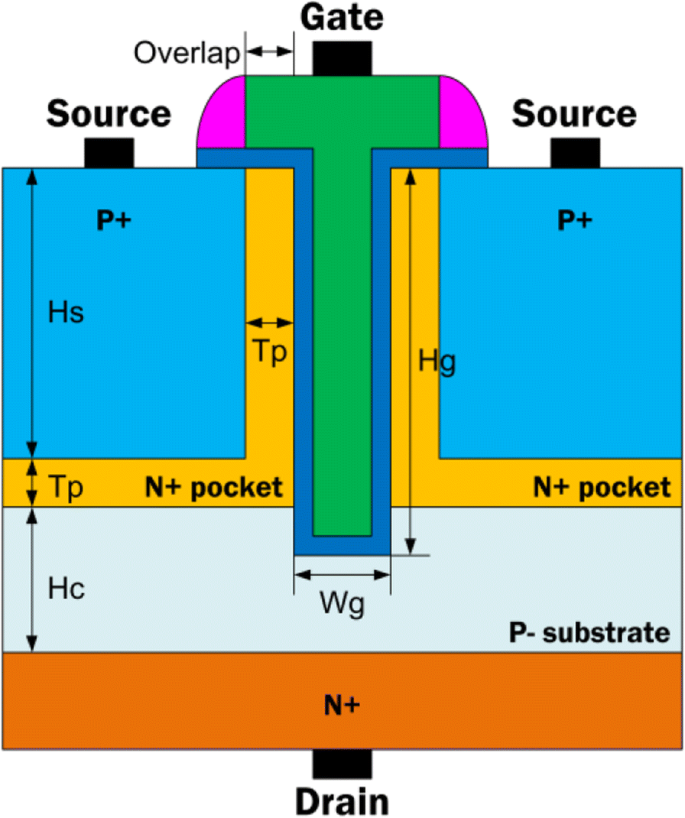

T形栅极双源隧道场效应晶体管(TGTFET)的结构如图1所示。栅极的形状类似于字母“T”(绿色区域)。双源区位于栅极的两侧(蓝宝石区)。插入两个 n+ 口袋(黄色区域)以增加通道隧穿率 [20,21,22]。 n+ 漏极放置在通道底部。因此,T 形栅极在垂直和横向方向上都与 n+ 口袋重叠。通过这种方式,可以增加隧道结顶部的电场。电场增强导致能带更陡峭地弯曲。最后,角电场增强提高了电子隧穿率[26]。

<图片>

所提出的T形栅极双源隧道场效应晶体管(TGTFET)示意图

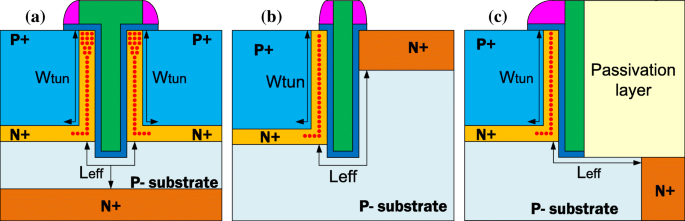

图 2 显示了 LTFET [23, 24]、UTFET [25] 和 TGTFET 的器件结构。栅极重叠有助于提高 TGTFET 的隧道效率。与LTFET和UTFET相比,TGTFET中的双源区可以使隧道结面积增加一倍。

<图片>

a 的比较 提议的 TGTFET,b UTFET 和 c LTFET

模拟中使用的硅基 TGTFET、UTFET 和 LTFET 的参数如下:Hs =30 nm(源极区域的高度),Hg =40 nm(凹槽栅极的高度),Wg =6 nm(栅极的宽度)栅极区域),Hc =15 nm(沟道区域的高度),Tp =5 nm(n+ 袋的厚度),φ =4. 33 eV(栅极功函数),Tox =2 nm(HfO2 栅极电介质的厚度),N S =1 × 10 20 厘米 −3 (p+ 源掺杂浓度), N D =1 × 10 19 厘米 −3 (n+ 漏极掺杂浓度), N sub =1 × 10 17 厘米 −3 (p-衬底掺杂浓度),和N P =5 × 10 18 厘米 −3 (n+ 口袋掺杂浓度)。模拟中的宽度系数默认为1μm。

TGTFET、UTFET 和 LTFET 的模拟在 Silvaco Atlas TCAD 工具中进行。该模拟引入了非局部BTBT模型以考虑能带空间变化,这有助于提高BTBT隧穿过程的准确性。 Lombardi 迁移率模型被认为使沟道迁移率更准确(通过考虑包括横向场和掺杂浓度的表面散射)。费米统计和带隙变窄模型被考虑在内以拟合高掺杂区域的影响。本文也考虑了Shockley-Read-Hall重组模型。

结果与讨论

不同参数下的器件机理和直流特性

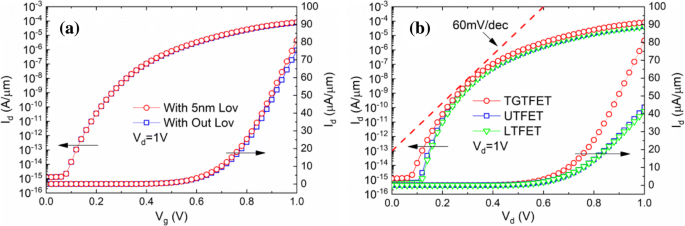

图 3a 显示了具有和不具有栅极重叠的 TGTFET 的传输特性。随着额外的门重叠,I ON 从 7.5 × 10 −5 增加 到 8.1 × 10 −5 A/μ m 在 V g =V d =1 V。图 3b 显示了 TGTFET、UTFET 和 LTFET 的传输特性曲线。为了使比较更加准确,将这三种设备的仿真模型和几何尺寸设置为相同。结果,TGTFET 的 I 增加了大约两倍 ON 与 LTFET 和 UTFET 相比,如图 3b 所示。 TGTFET 的 SSmin 在 V 处为 24.4 mV/dec g =0.1 V,当 0 V <V 时,SSavg 为 51.5 mV/dec g <0.5 V。开关比 (I ON/I OFF) 是 6.7 × 10 10 在 V g =V d =1 V 和 6.5 × 10 8 在 V g =V d =0.5 V。

<图片>

模拟a 有/无栅极重叠和b的TGTFET的传输特性 TGTFET、UTFET、LTFET的传输特性

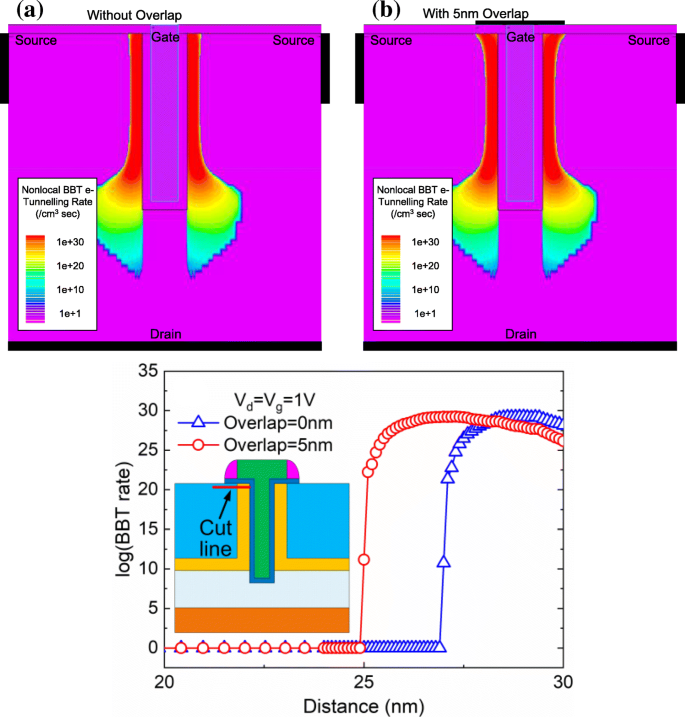

图 4a、b 显示了具有和不具有 5 纳米栅极重叠的 TGTFET 的 BBT 速率。从图 4c,我们可以清楚地看到,具有 5 nm 栅极重叠的器件在器件表面下方具有更宽的电子隧穿区域,这会导致 I ON 增加。

<图片>

a的模拟BBT电子隧穿率图 没有门重叠的器件,b 具有 5-nm 栅极重叠的器件,以及 c 两个器件的 BBT 电子隧穿率,在器件表面以下 1 纳米处; V g =V d =1 V

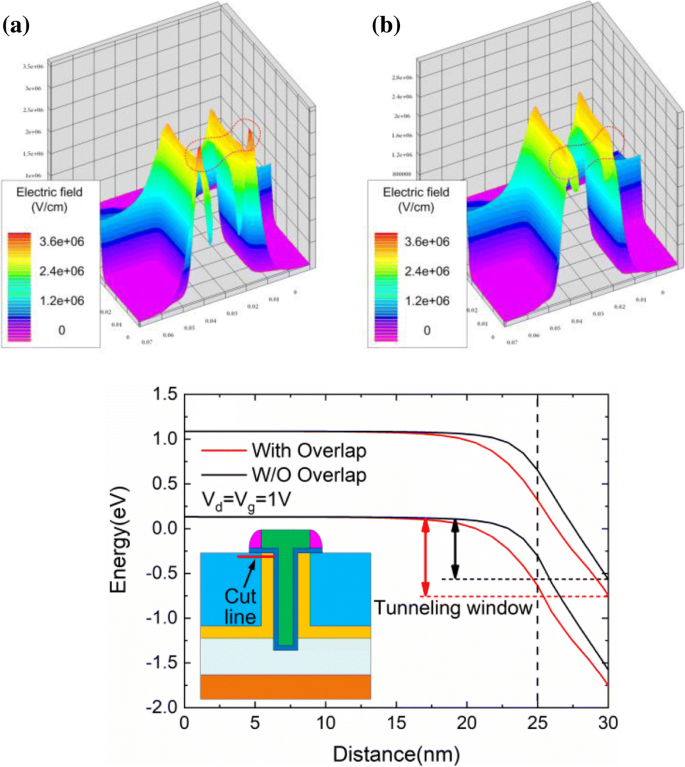

图 5a、b 显示了具有和不具有栅极重叠的 TGTFET 电场的 3D 图。两个电场峰值出现在 TGTFET 中,栅极重叠为 5 纳米,如图 5a 中的虚线圆圈所示。由于没有栅极重叠,图 5b 中没有出现电场峰值。图 5c 显示了器件表面下的能带结构。图 5c 中的插图显示了切割线位置。通过栅极重叠,可以获得更大的隧穿窗口。因此,更高的 BBT 率和 I 可以实现ON。

<图片>

器件a的电场3D示意图 有重叠和 b 无重叠;模拟c 从源到口袋区域(氧化物界面下方 1 nm)的能带图

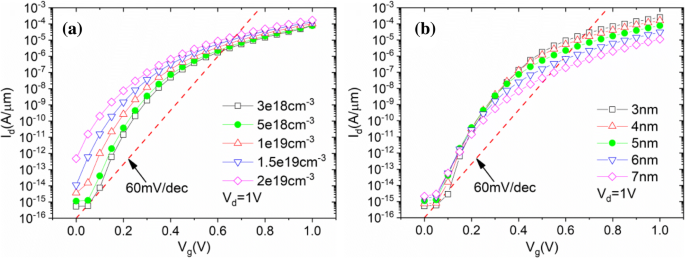

图 6 显示了 n+ 口袋对 TGTFET 性能的影响。 我 OFF 随着 n+ 袋掺杂浓度的增加而迅速增加,如图 6a 所示。较低的 SS 和较大的 I 当 N 时,通过将 n+ 口袋 (Tp) 的厚度从 7 nm 减小到 3 nm 可以获得 ON P =5 × 10 18 厘米 −3 ,如图 6b 所示。同时,图 6b 中没有注意到明显的亚阈值电流。从图 6a 可以证实,相对较低的 n+ 袋掺杂浓度有助于抑制亚阈值电流。

<图片>

具有不同 n+ 口袋 a 的模拟漏极电流 浓度和b V 处的厚度 d =1 V

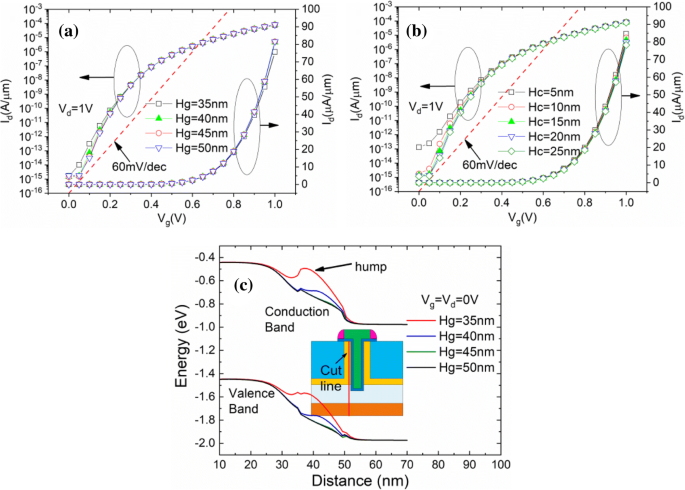

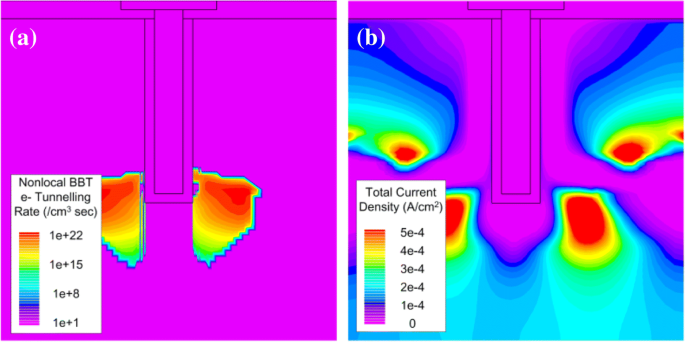

栅极高度 (Hg) 和沟道厚度 (Hc) 的影响分别如图 7a、b 所示。一个小我 当 Hg 增加时,出现 ON 和 SS 改善。因为当Hg =35 nm时,导通电流路径上存在明显的能带驼峰,成为幸运电子(通过隧道结的电子)的一定障碍,如图7c所示,可以导致我 在减少。当 Hg 增加时,能带驼峰减弱,导致 I ON 和 SS 改进。轻微的I 随着 Hc 的降低,ON 得到改善,如图 7b 所示。然而,当 Hc 降低到 5 nm 时,可以观察到亚阈值特性的严重退化。这可以通过 n+ 口袋角落处增加的亚阈值隧穿电流来解释,如图 8 所示。图 8a 显示了当 Hc =5 nm 时明显的断态带间隧穿现象,而图 8b 显示了我 Hc =5 nm 时的关断电流密度。

<图片>

使用 a 模拟 TGTFET 的传输特性 不同的汞,b 不同的 Hc 和 c 电流路径上的导带驼峰

<图片>

关闭状态a的模拟图 BTBT电子隧穿率和b Hc =5 nm时的电流密度

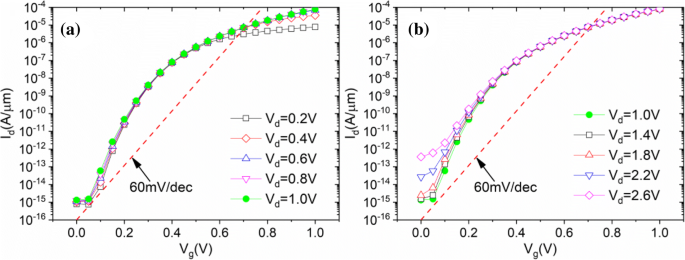

如图 9 所示,漏源电压 (V d) 在本文中也被考虑在内。对于 V d <0.6 V, I ON随着V的增加而明显增加 d,如图 9a 所示。这是因为 p 沟道的电位随着 V 的增加而缓慢增加 d 并导致 p 沟道的电阻降低。对于 V d> 1.8 V,如图 9b 所示,I ON几乎不随着V的增加而增加 d,但是我 OFF 显着增加。这是因为随着 V 的增加,n+ 袋拐角处的亚阈值隧道电流迅速增加 d.最后,对于 0.6 V <V d <1.8 V,TGTFET 表现出良好且稳定的性能。因此,TGTFET对漏极感应势垒降低(DIBL)具有鲁棒性,并在较大的施加电压动态范围内表现出良好且稳定的性能。

<图片>

a 的模拟漏极电流 V d ≤ 1 V 和 b V d ≥ 1 V

TGTFET、UTFET 和 LTFET 的模拟/射频性能

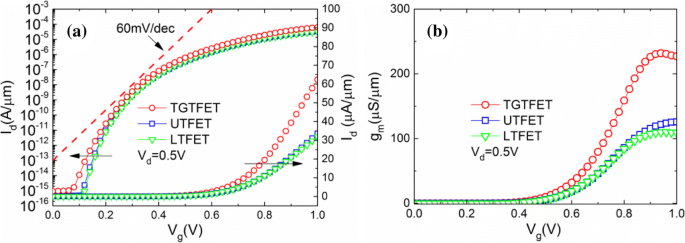

图 10 显示了 V 下 TGTFET、UTFET 和 LTFET 的传输特性和跨导曲线 d =0.5 V。跨导 (g m) 可以从传递特性曲线的一阶导数中获得,如公式 3 所示。 (1) [27,28,29]:

$$ {g}_{\mathrm{m}}={dI}_{\mathrm{d}s}/{dV}_{\mathrm{gs}} $$ (1) <图片><来源类型="image/webp" srcset="//media.springernature.com/lw685/springer-static/image/art%3A10.1186%2Fs11671-018-2723-y/MediaObjects/11671_2018_2723_Fig10_HTML">.png?as=webp /来源>

一 传输特性和b V 下 TGTFET、UTFET 和 LTFET 的跨导曲线 d =0.5 V

因此,如图 10 所示,TGTFET 的最大跨导 (232 μS/μm) 大约是 UTFET (120 μS/μm) 和 LTFET (110 μS/μm) 的两倍。这得益于双源栅重叠贡献的电流增益。

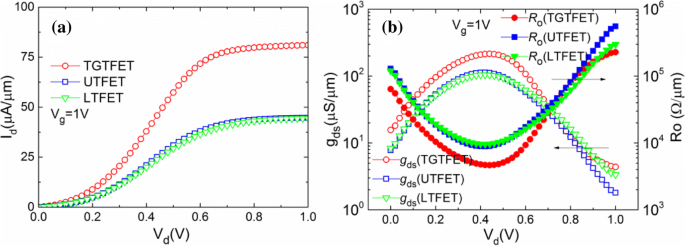

图 11 显示了输出特性、输出电导 (g ds) 和输出阻抗 (R o) TGTFET、UTFET 和 LTFET 的曲线。如图 11a 所示,可以清楚地看到器件的输出电流随着 V 的增加而增加 d,但是当 V d 达到 0.6 V 以上,输出电流趋于饱和。通过观察,很容易发现TGTFET的输出电流比UTFET和LTFET大两倍。图 11b 显示了输出电导 (g ds) 和输出阻抗 (R o) TGTFET、UTFET 和 LTFET 的曲线。 g ds 可以通过输出电流的推导得到,如公式 1 所示。 (2) [27, 29] 而 R o 可以表示为输出电导的倒数。

$$ {g}_{\mathrm{ds}}={dI}_{\mathrm{ds}}/{dV}_{\mathrm{ds}} $$ (2) <图片>

一 输出特性,b 输出电导 (g ds) 和 c 输出阻抗 (R o) TGTFET、UTFET 和 LTFET 的曲线

由于在输出电流上的优势,TGTFET获得最高的g ds 和最小 R o 这三个设备中的。在 1-V 栅极偏置条件下,TGTFET 获得了最大 g ds 为 214 μS/μm,最小 R o 在 0.45 V V 下为 4.6 kΩ/μm d.在相同的栅极偏置条件下,UTFET和LTFET获得了最大g ds 为 113 μS/μm 和 105 μS/μm 以及最小 R o 9.0 kΩ/μm 和 9.6 kΩ/μm 低于 0.4 V V d.

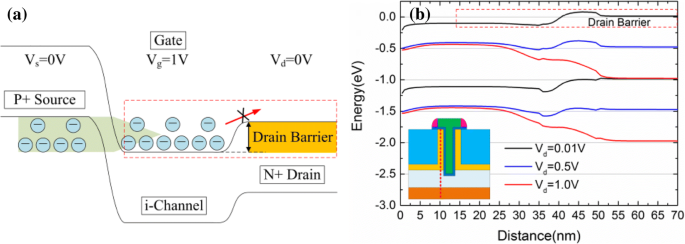

此外,在图 11 中,不难发现器件输出特性的线性区域表现出一定的非线性。如图 11a 所示,R o 随着 V 的增加先减小然后增加 d.一些研究小组对这一现象给出了相应的物理过程[7, 30],但仍有一些问题没有得到明确的解释。众所周知,R o 由沟道区和隧道结的电阻决定。当 V d <0.4 V,R o 随着 V 的增加而减小 d.考虑以下情况,当 V d =0 V 和 V g =1 V,没有一个幸运电子可以扫到漏极侧,几乎所有的电子都被相对较高的漏极势垒俘获在沟道区,如图12a、b中红色虚线框所示.当 0 V <V d <0.4 V,随着V的增加 d,漏极势垒变弱(如图 12b 所示)。因此,被困在沟道区的电子可以穿过漏极势垒,然后被漏极收集。这是电子从通道到漏极的热激发过程。最后,由于隧道结已经完全开启(当 V g =1 V),隧道电流总是处于过剩状态,隧道结引入的电阻可以忽略不计。这时,R o 由通道电阻和 R 决定 o 由跨越漏极势垒的电子热激发过程决定。因此,R o 随着 V 的增加而减小 d.当 V d> 0.6 V,这三个器件逐渐进入饱和区和R o 变大。这是因为当 V d 很大,几乎所有通过隧道结的电子都被相对较高的电场扫到漏极侧。隧道电流成为漏极电流的极限。在这种情况下,R o 主要由隧道结决定。然而,当 V d 增加。 V d 对隧道结(n+ 口袋侧)的能带结构影响很小,如图 12b 所示。结果,隧道电流不能明显增加,几乎没有I ON随着V的不断增加而增加 d(当 V d> 0.6 V),这意味着阻抗增加。此外,当 0.4 V <V d <0.6 V, R o 由沟道电阻和隧道结共同决定。

<图片>

一 V能带示意图 d =0 V 和 V g =1 V。b V不同偏压下能带图的仿真结果

由上述分析可知,R TFET 的 o 受隧穿过程和通道电子热激发过程的影响。主要的物理机制可以支配R o 随 V 移动 d 变异。最后,R o 先减小后增大,从而造成输出特性的非线性。顺便说一下,通过观察图 11b,很容易发现 TGTFET 的输出阻抗远小于 UTFET 和 LTFET。这是由于TGTFET的双源极和横向栅极重叠结构带来了更好的隧穿效率。

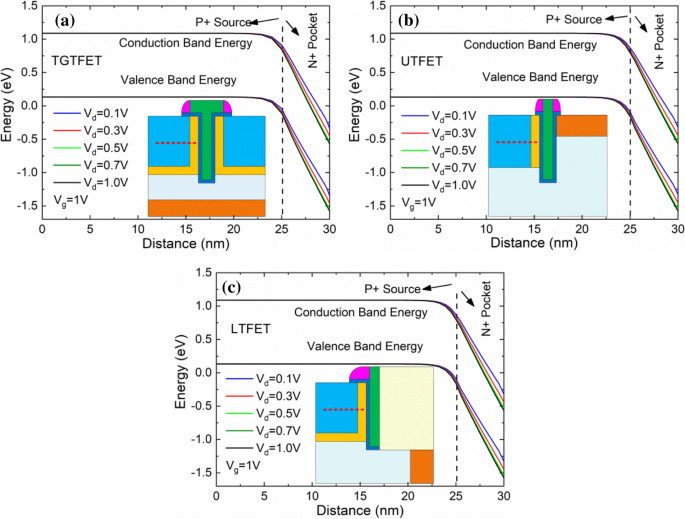

图 13 显示了具有不同施加电压的 TGTFET、UTFET 和 LTFET 的能带结构。插图中的红色虚线代表绘制能带的位置(在表面下方 15 nm,就在源区的 1/2 高度处)。可以看出,随着 V d 从 0.1 V 增加到 0.5 V,TGTFET、UTFET 和 LTFET 的能带结构有明显的弯曲趋势。这是因为漏极电压可以拉低漏极侧附近隧道结的电位。这表明,对于 TGTFET、UTFET 和 LTFET,V 0.1 到 0.5 V 的 d 有利于隧穿效率。然而,当 V d> 0.5 V,能带随V的变化 d 增加不值一提。这与图 12b 中的分析结果一致。

<图片>

a的能带结构 TGTFET,b UTFET 和 c V 处的 LTFET g =1

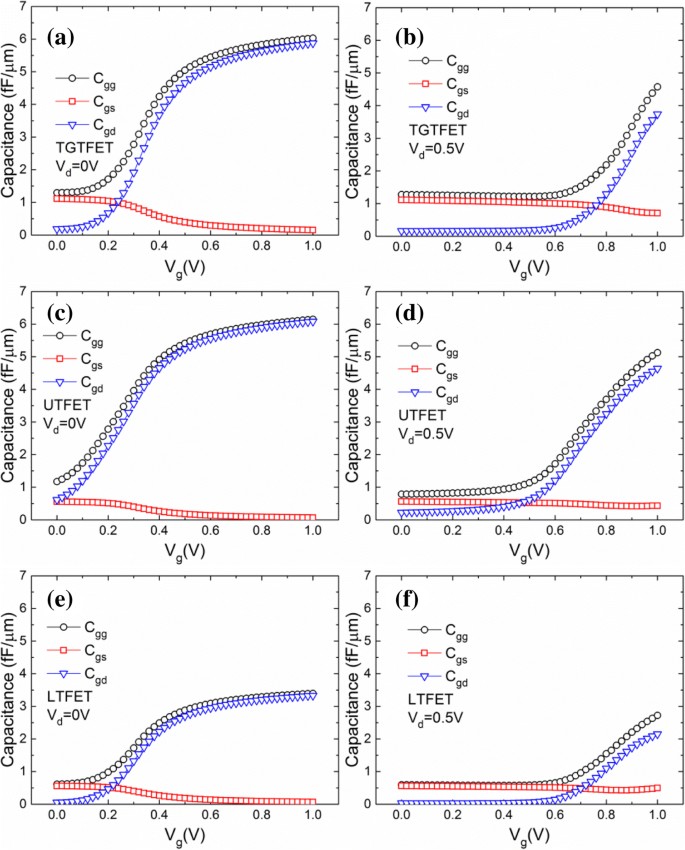

众所周知,栅极电容 (C gg) 的器件会极大地影响集成电路的频率特性。对于 TGTFET、UTFET 和 LTFET,C gg 通常由 C 组成 gs(栅极到源极的电容)和 C gd(栅漏电容)。因此,C的特点 gg,C gs 和 C gd对于评估器件的频率特性和模拟应用能力具有重要意义。尤其是TFET,电容特性与MOSFET有很大不同。由于源区存在隧道结,TFET通常具有较小的C gs [1, 11]。因此,C TFET的gg主要由C决定 广东图 14 显示了 TGTFET、UTFET 和 LTFET 的电容与 V V 下的 g d =0.5 V 和 V d =0 V,分别。

<图片>

TGTFET 的电容与 V a 下的 g V d =0 V 和 b V d =0.5 V. UTFET 的电容与 V g 在 c 下 V d =0 V 和 d V d =0.5 V. LTFET 的电容与 V g 在 e 下 V d =0 V 和 f V d =0.5 V

通过观察图 14a、b,很容易发现 C 在 V 下,1V 栅极电压下的 TGTFET 的 gs 为 0.15 fF/μm d =0 V 和 0.7 fF/μm 在 V d =0.5 V,远小于C gd(在 V 处为 5.8 fF/μm d =0 V 和 3.7 fF/μm 在 V d =0.5 V)。因此,C TGTFET的gg主要由C决定 广东当 V d =0 V,C gg 和 C gd随着V的增加而迅速增加 g,如图 14a 所示。这是因为随着 V 的增加 g、电子聚集到器件沟道中的栅极界面,使电容迅速上升。当 V d =0.5 V,C gd 直到 V 才明显增加 g 增加到 0.6 V 以上,如图 14b 所示。这是因为当 V g 低,只有少数幸运电子可以通过隧道结进入沟道。这些幸运电子中的一些将参与复合过程,而其他大部分将由于 0.5V 的漏极电压而被漏极迅速收集。因此,这些幸运的电子很难留在器件通道中。然而,随着 V g 增加,幸运电子的数量迅速增加。此时,无论是漏极收集还是电子-空穴复合过程都无法快速耗尽这些幸运电子。因此,通道中的电子浓度增加,电容迅速上升。结果,电容特性曲线趋向于右移,而 V d 增加,如图 14a、b 所示。上述分析和现象也适用于 UTFET 和 LTFET,如图 14c-f 所示。此外,UTFET 的栅极电容在 0 V 和 0.5 V V d分别达到6.2 fF/μm和5.1 fF/μm,LTFET分别达到3.4 fF/μm和2.7 fF/μm。

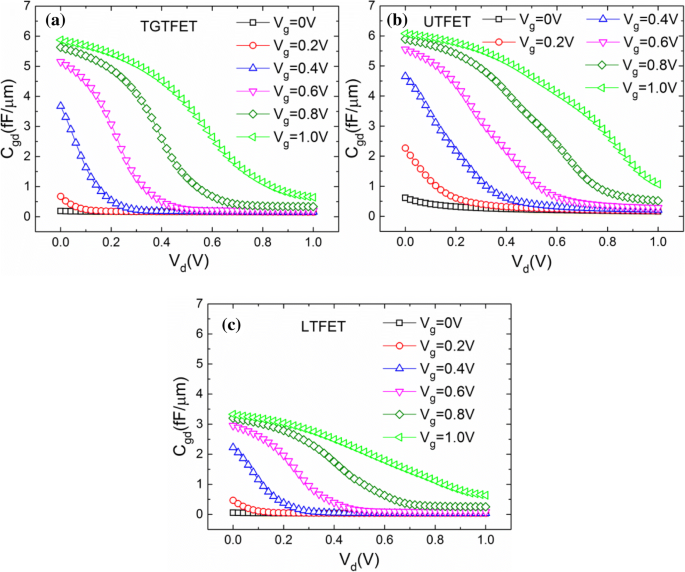

由于LTFET的栅极和漏极之间没有直接重叠,而且栅极和漏极之间的距离相对较远,因此LTFET具有最好的电容特性和最小的C GG。相比之下,UTFET 的栅极和漏极之间存在直接重叠。因此,靠近漏侧的电子更容易被栅极控制,从而导致较大的C UTFET 的 gg。对于TGTFET,虽然栅极和漏极之间的距离很近,但是有一个轻掺杂的沟道区可以隔离栅极和漏极。因此,TGTFET 的电容优于 UTFET,但略逊于 LTFET。图 15 显示了 C TGTFET、UTFET 和 LTFET 与 V 的 gd 特性 d 在不同的 V 下 G。从图 15a-v 的观察,不难发现 C 这三种设备的gd特性是相似的。也就是说,对于固定的 V g, C gd随着V的增加而减小 d.另一方面,对于固定的 V d、C gd随着V的增加而增加 g.

<图片>

C a 的 gd 特性 TGTFET,b UTFET 和 c LTFET 与 V d 在不同的 V 下 克

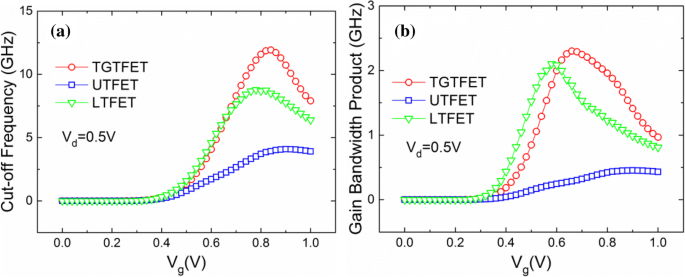

众所周知,截止频率 (f T)和增益带宽(GBW)是评价器件频率特性的评价标准。 f T 取决于 g 的比率 m 到 C gg,如方程式所示。 (3) [30, 31]。对于等于 10 的某个 DC 增益,GBW 可以用 g 的比率表示 m 到 C gd,如方程式所示。 (4) [17]:

$$ {f}_T=\frac{g_{\mathrm{m}}}{2\pi {C}_{\mathrm{gs}}\sqrt{1+2{C}_{\mathrm{gd} }/{C}_{\mathrm{gs}}}}\approx \frac{g_{\mathrm{m}}}{2\pi \left({C}_{\mathrm{gs}}}+{C }_{\mathrm{gd}}\right)}=\frac{g_{\mathrm{m}}}{2\pi {C}_{\mathrm{gg}}} $$ (3) $$ \ mathrm{GWB}={g}_{\mathrm{m}}/2\pi 10{C}_{\mathrm{gd}} $$ (4)图 16 显示了 f 的特性曲线 TGTFET、UTFET 和 LTFET 的 T 和 GBW。得益于T形栅极引入的双源极和横向栅极重叠等结构优势,TGTFET获得了与UTFET和LTFET相比最出色的频率特性。 V条件下 d =0.5 V,f TGTFET 的 T 和 GBW 分别达到最大值 11.9 GHz 和 2.3 GHz。得益于栅极和漏极之间的长距离且没有栅极/漏极重叠,LTFET 获得了很小的 C gg 和良好的频率特性。 f LTFET 的 T 和 GBW 分别达到 8.7 GHz 和 2.1 GHz。 UTFET 的电容特性与 TGTFET 和 LTFET 相比较差。这是因为直接栅极/漏极重叠。结果,f的最大值 UTFET 的 T 和 GBW 分别只能达到 4.1 GHz 和 0.5 GHz。

The characteristic curves of a f T and b GBW of TGTFET, UTFET, and LTFET versus V g at V d = 0.5 V

结论

In this paper, a T-shape gate dual-source tunnel field-effect transistor (TGTFET) with good performance is proposed and investigated. The structure, mechanism, and the influence of device parameter on the characteristic of TGTFET are discussed. In addition, the characteristics of TGTFET, UTFET, and LTFET are discussed and compared in this paper. The dual-source regions are introduced to double the area of the tunneling junction. The gate overlap and the n+ pockets can obviously enhance the tunneling efficiency of the tunneling junction in TGTFET. Finally, the TGTFET with impressive characteristics (I ON = 8.1 × 10 −5 A/μm, I ON/I OFF = 6.7 × 10 10 and SSmin = 24.4 mV/dec) is obtained. At the same time, TGTFET is robust to DIBL, which means TGTFET can exhibit a good and stable performance in a larger applied voltage dynamic range. Furthermore, the analog/RF performance of TGTFET is studied and compared with UTFET and LTFET. The key parameter such as input/output characteristics, capacitance characteristics, GBW, and f T are analyzed. Benefiting from the no direct overlap between the gate and drain, TGTFET obtains a relatively small C gd and C GG。 Finally, TGTFET with remarkable frequency characteristics (f T = 11.9 GHz and GBW = 2.3 GHz) is obtained. As a conclusion, it is expected that TGTFET can be one of the promising alternatives for the next generation of device in low-power and analog/RF applications.

缩写

- C gd :

-

Gate to drain capacitance

- C gs :

-

Gate to source capacitance

- f T :

-

Cut-off frequency

- GBW:

-

Gain bandwidth

- g ds :

-

Output conductance

- g m :

-

Transconductance

- Hc:

-

Height of the channel layer

- Hg:

-

Height of the gate electrode

- Hs:

-

Height of the source layer

- LTFET:

-

L-shape gate tunnel field-effect transistor

- N D :

-

Doping concentration of n+ drain

- N P :

-

Doping concentration of n+ pocket

- N S :

-

Doping concentration of p+ source

- N sub :

-

Doping concentration of p− substrate

- R o :

-

Output impedance

- TGTFET:

-

T-shape gate dual-source tunnel field-effect transistor

- Tox:

-

Thickness of the HfO2 gate dielectric

- Tp:

-

Thickness of n+ pocket

- UTFET:

-

U-shape gate tunnel field-effect transistor

- V d :

-

Drain to source voltage

- V g :

-

Gate to source voltage

- Wg:

-

Width of the gate electrode

纳米材料