双向门控S/D对称可互换双向隧道场效应晶体管结构参数及内部机理的影响研究

摘要

本文提出了一种双边栅极控制的 S/D 对称和可互换双向隧道场效应晶体管 (B-TFET),与传统的非对称 TFET 相比,它显示了双向开关特性和与 CMOS 集成电路的兼容性的优势。结构参数的影响,例如 N + 的掺杂浓度 区域和 P + region,N + 的长度 本征区的区域和长度,对器件性能,例如,转移特性,I on-I 详细讨论和解释了关断比和亚阈值摆动的内部机制。

介绍

功耗是集成电路产业的主要问题之一。如果一个设备工作在导通状态,它的传导电流必须达到一定的临界值;当电流达到临界值时,相应的栅极电压被定义为阈值电压。当器件处于关断状态时,对应的栅极电压应与临界导通状态下的值不同,通常称为关态电压。亚阈值摆幅 (SS) 的概念适用于工作在关断状态和临界导通状态之间的器件,其等于当电流增加一个数量级时栅极电压的变化。当器件设计好后,器件的临界通态电流值、阈值电压和断态电压已经确定;那么,SS越小,对应亚阈值区域的电流变化越大,器件在关断状态下的静态电流越小,器件静态功耗越低。金属氧化物半导体场效应晶体管 (MOSFET) 是集成电路中广泛使用的基本单元,其 SS 受器件工作时产生的电流物理机制的限制,不能低于限值 60毫伏/十进制为了突破这一限制,近年来提出了一种基于硅基技术的隧道场效应晶体管(PIN 或 NIP TFET)。传统的 TFET 是通过在 p 之间添加一层低掺杂本征半导体而形成的 - 和 n 型半导体材料。与MOSFET相比,TFET具有灵敏度高、静态功耗低的优点[1]。 TFET 是通过调制穿过势垒的量子隧穿来切换的,而不是像在传统 MOSFET 中那样调制势垒上的热电子发射。因此,TFET 不受载流子热麦克斯韦-玻尔兹曼尾的限制,这将 MOSFET 的 SS 在室温下限制为 60 mV/dec [2](在 300 K 时正好为 63 mV/dec)。这个概念是由 Chang 等人提出的。在 IBM [3] 工作时。 Joerg Appenzeller 和他在 IBM 的同事首次证明了 TFET 的 SS 可以低于 60 mV/dec。 TFET可作为高能效电子开关[4],突破了MOSFET的瓶颈,大大降低了IC功耗。生产工艺与MOSFET兼容。很有可能取代MOSFET晶体管成为下一代集成电路的基本单元。因此,TFETs 成为近年来的热门话题 [5, 6]。为了提高 TFETs 在 SS、正向传导电流和反向泄漏方面的性能,人们对 TFET 器件的结构设计和优化进行了许多研究,主要集中在改善器件沟道和栅电极的结构形状 [7]。 ,8,9,10,11,12] 和具有不同功函数的栅极介电材料。对栅介质材料[13,14,15]和不同介电常数的栅介质进行了特性分析和结构优化[15,16,17,18,19,20]。在器件物理方面,具有双栅结构 [21,22,23,24,25,26,27] 和环绕栅结构 [28,29,30,31,32,33] 的 TFET 的分析建模也有被广泛执行。与 MOSFET 相比,硅基 TFET 的一个缺点是正向电流较小,正向电流的大小由隧道电流产生的效率决定。可以通过减小用于产生带间隧道电流的区域中的价带和导带之间的带隙或通过减小隧道区域的厚度来提高隧道电流的产生效率。因此,在材料工程中,基于窄带隙半导体材料和异质结隧穿结构的TFET器件得到了广泛的发展[34,35,36,37,38]。同时,将二维材料引入 TFET 作为具有超薄厚度的隧道层已得到广泛研究 [39,40,41,42,43,44]。此外,还有一些论文报道了TFET的可靠性,例如源极掺杂对隧道带隙交错的影响[45]、陷阱辅助隧道对TFET亚阈值特性的影响[46]、随机掺杂器件性能扰动 [47]。然而,目前的研究成果主要针对单个TFET的基本工作特性和工作原理,而TFET的研发最重要的根本目的是提供一种功耗更低的基本结构单元,替代现有的MOSFET结构。 .为了实现这一基本目标,必须将其设置在特定电路中以验证其与 MOSFET 技术的兼容性。目前,基于TFET器件的电路设计策略研究正在逐步展开,如模拟和混合信号电路[48,49,50]、数字逻辑电路[50、51]、电源管理电路设计[52]。也有基于 MOSFET 和 TFET 的混合电路设计的研究 [53]。然而,源区和漏区的掺杂类型彼此相反,这造成源区和漏区的不对称。这种非对称结构使得源漏对称的MOSFET无法完全替代。

取 n 型 TFET 为例。 p 的一面 -型杂质用作源区,而另一侧带有n -型杂质用作漏区。器件工作时,必须从漏区到源区施加一个正电位差。如果源极和漏极互换,即 p - 型杂质区域相对于 n 设置在更高的电位 -型杂质区,然后由p形成的PN结 -type 杂质区和 n -型杂质区会一直处于正偏压状态,导致栅电极控制功能失效,TFET几乎一直处于导通状态,无法关断。换句话说,它会导致 TFET 开关功能失效。换言之,必须利用晶体管的双向开关特性才能正常工作的电路功能模块(如传输门),使用传统的源漏非对称结构的TFET很难实现,以解决这些问题。 ,我们提出了一种源漏对称和可互换的双向 TFET (B-TFET) [54],与传统的非对称 TFET 相比,它显示了双向开关特性和与 CMOS 集成电路的兼容性的优势。在本文中,我们提出了一种改进的具有平面沟道的双边栅极控制 B-TFET。 N + 掺杂浓度等关键结构参数的影响 区域和 P + region,N + 的长度 本征区的区域和长度,对器件性能,例如,转移特性,I on-I 关闭比和亚阈值摆幅,在物理分析的基础上详细解释。此后,对这些关键的结构参数进行优化。

方法

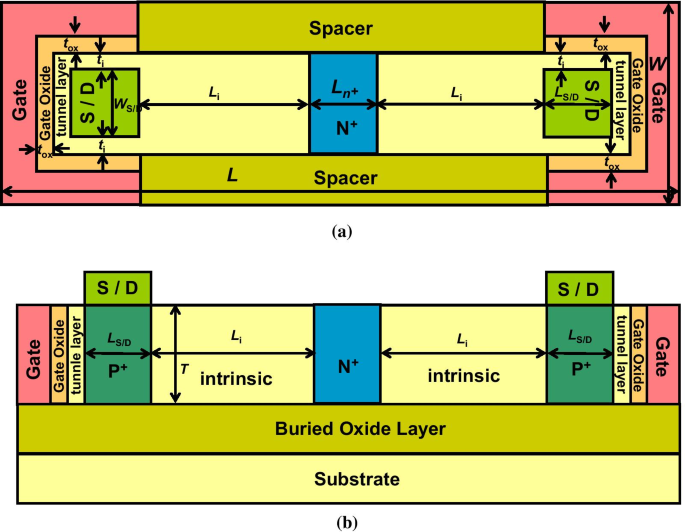

图 1a 显示了具有平面沟道的双边栅极控制 N 型 B-TFET 的示意性俯视图。图 1b 显示了双边栅极控制的 N 型 B-TFET 的横截面图。与传统的 TFET 不同,所提出的 B-TFET 是完全对称的,源极/漏极可互换 P + -掺杂区位于硅体的每一侧,栅电极位于硅体的两侧。整个器件结构是对称的。 N + -掺杂区位于硅体的中心部分。 L 和 W 分别是所提议设备的全长和全宽。 L i 是本征区的长度; L N+ 是 N + 的长度 地区; L S/D 和 W S/D 是 P + 的长度和宽度 源极/漏极可互换区域,分别; \(T\) 是硅体厚度; \(t_{{{\text{ox}}}}\) 是栅极氧化层的厚度; \(t_{i}\) 是 S/D 区和栅氧化层之间的本征隧道区的厚度。

一 具有平面沟道的双边栅极控制 N 型 B-TFET 的俯视示意图。 b 双边栅控N型B-TFET的横截面图

在本文中,所有物理模型,如费米统计模型、CVT 迁移率模型、俄歇复合模型、带隙变窄模型和标准带间隧道模型都被打开。本文装置的所有参数如表1所示。

<图>结果与讨论

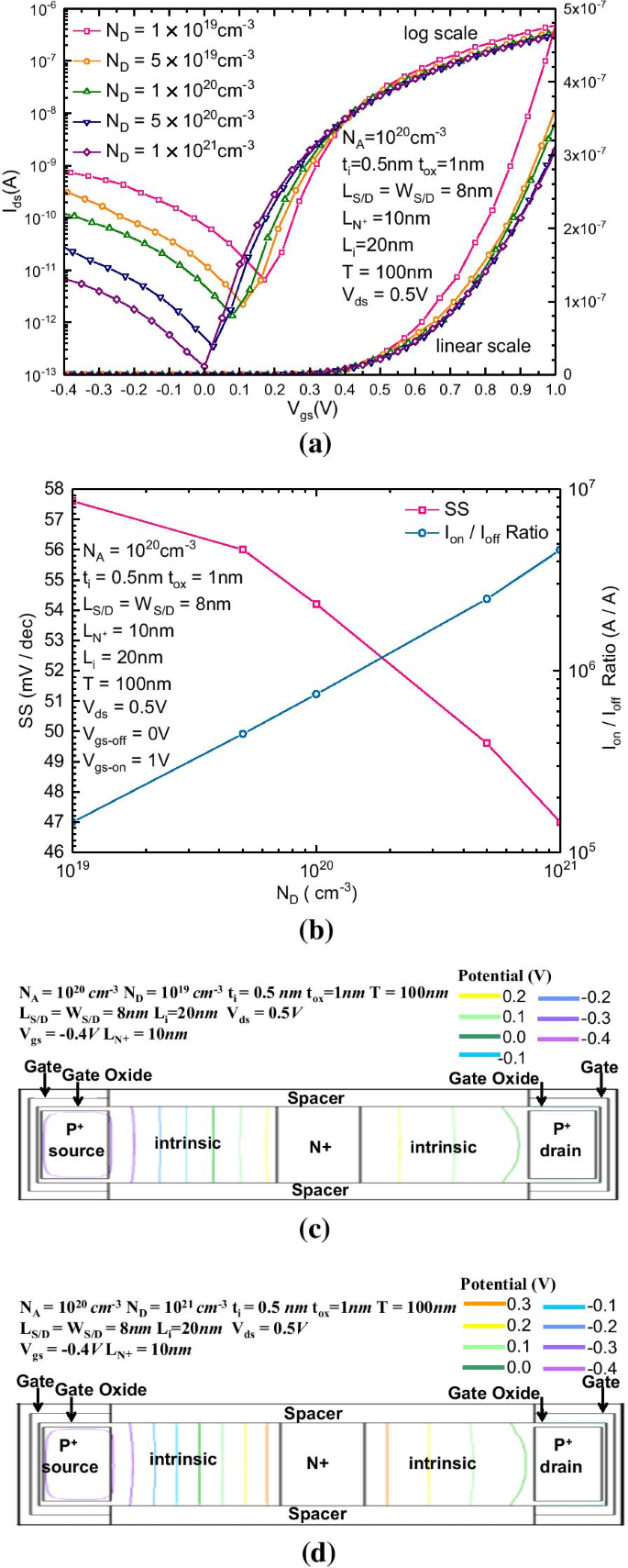

图 2a、b 显示了传输特性、\(I_{{{\text{on}}}}{-}I_{{{\text{off}}}}\) 比率和不同 \(N_{ D}\) (\(10^{18}\)–\(10^{21} \,{\text{cm}}^{ - 3}\))。在图 2a 中,\(N_{D}\) 影响反向偏置的漏源漏电流的强度。随着掺杂浓度的增加,漏电流受到明显抑制,正向电流没有明显变化。在图 2b 中,SS 和 \(I_{{{\text{on}}}}{-}I_{{{\text{off}}}}\) 也受 \(N_{D}\ )。随着掺杂浓度的增加,由于反向漏电流被明显抑制,静态工作点的电流减小,因此平均SS也减小。由于正向电流的影响远小于反向泄漏,\(I_{{{\text{on}}}}{-}I_{{{\text{off}}}}\) 比值随着增加而增加在掺杂浓度。图 2c、d 显示了所提出的 B-TFET 的二维电位分布,其中 \(N_{D}\) 等于 10 19 厘米 −3 和 10 21 厘米 −3 , 分别。当栅极反向偏置时,正向偏置的漏极和反向偏置的栅极之间会产生强电场,从而在漏极区附近产生强带间隧穿。在由此产生的电子-空穴对中,电子可以直接流出漏电极,而价带空穴必须流过N + 区,继而到源极侧的本征区,由源极放电形成连续漏电流。为了最小化泄漏电流,应有效阻止带间隧道产生的空穴流出 N + 区域。与浓度较低的N + 区域相比,浓度较高的N + 区域在P + 区域和N + 区域之间形成了更大的电位差,即本征区域与N + 区域边界处的电位值会增加随着\(N_{D}\) 的增加,因为浓度较高的N + 区域会在源漏之间产生更大的电子浓度差。然后,更多的电子可以从N + 区扩散到N + 区两侧的本征区,这增加了N + 区电离后正电荷(主要由施主组成)的数量,从而增加了电势P + 区域和N + 区域之间的差异。正是因为掺杂浓度较高的N + 区在电离后比源漏侧的电位都高,可以更有效地阻挡漏区附近带间隧穿产生的空穴,从而更有效地降低漏电流。

一 \(I_{{{\text{ds}}}}{-}V_{{{\text{gs}}}}\) 传递特性和b SS 的变化和 \(I_{{{\text{on}}}} {-}I_{{{\text{off}}}}\) 比率与不同 \(N_{D }\); c 的反向偏置二维电位分布 N D =10 19 厘米 −3 和 d N D =10 21 厘米 −3

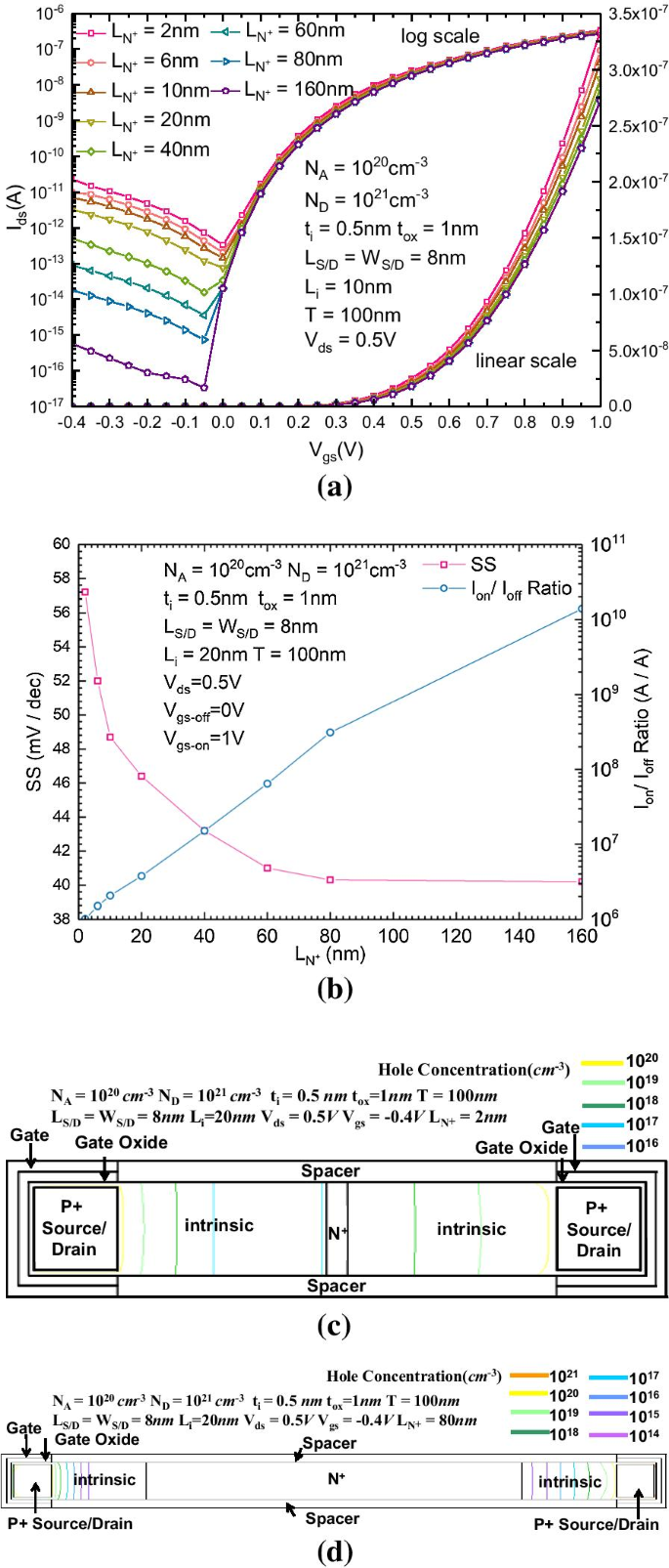

除了N + 区的掺杂浓度外,N + 区的另一个关键参数是N + 区的长度,它可以显着影响反向偏置漏电流。图 3a、b 显示了具有不同 的拟议 B-TFET 的 \(I_{{{\text{ds}}}}{-}V_{{{\text{gs}}}}\) 传输特性L N+。随着L的增加,反向偏置漏电流大大降低 N+。如图 2b 所示,亚阈值摆动和 \(I_{{{\text{on}}}}{-}I_{{{\text{off}}}}\) 也受 L N+。随着L的增加 N+,由于反向漏电流被明显抑制,静态工作点的电流和平均SS也降低。正向电流的影响远小于反向泄漏,\(I_{{{\text{on}}}}{-}I_{{{\text{off}}}}\)比值随着增加而增加在 L N+。图 3c、d 显示了具有 L 的拟议 B-TFET 的二维空穴浓度分布 N+ 分别等于 2 nm 和 80 nm。当 L N+等于2nm,N + 区域的最小空穴浓度大于10 17 厘米 −3 , 而当 L N+ 等于 80 nm,最小空穴浓度小于 10 14 厘米 −3 . N + 区域长度的增加增强了其阻止空穴通过N + 区域的能力。作为N + 区的非平衡少数载流子,当N + 区较长时,更多的空穴会在通过N + 区之前与电子复合,因此N + 区长度的增加也可以形成连续反向偏置漏电流。平均 SS 可降低至 40.2 mV/dec,\(I_{{{\text{on}}}}{-}I_{{{\text{off}}}}\) 比值可以超过 10 10 .

一 \(I_{{{\text{ds}}}}{-}V_{{{\text{gs}}}}\) 特性; b SS 的变化和\(I_{{{\text{on}}}}{-}I_{{{\text{off}}}}\) 比建议的 B-TFET 与不同的 LN+;在 L 反向偏置下,所提出的 B-TFET 的二维空穴浓度分布 N+ 等于 (3) 2 nm 和 (4) 80 nm

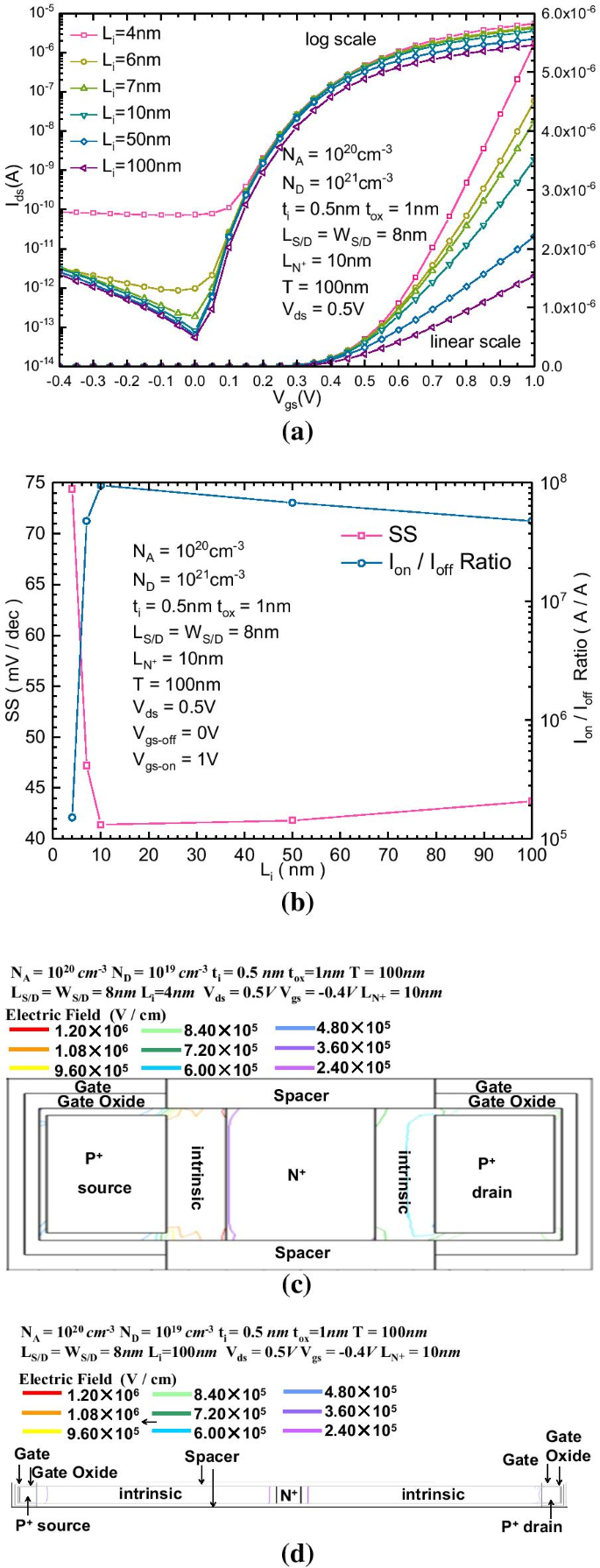

图 4a、b 显示了 \(I_{{{\text{ds}}}}{-}V_{{{\text{gs}}}}\) 传输特性和 SS 和 \(I_{{{ \text{on}}}}{-}I_{{{\text{off}}}}\) 具有不同 L 的拟议 B-TFET 的比率 我,分别。正向电流随着L的增加而减小 i 因为本征区的电阻与其自身的长度成正比。然后,为了使正向电流最大化,本征区的长度应该最小化。然而,本征区长度的减少增强了源极P + 区和N + 区之间本征区的电场,因此该区域附近的能带弯曲大于漏电极附近的本征区,从而导致更多的反向偏置漏电流。图 4c、d 显示了用于 L 的拟议 B-TFET 的二维反向偏置电位分布 i 分别等于 4 纳米和 100 纳米。对于最短的 L 在(4 nm)情况下,源极附近的源极P + 区和N + 区之间的本征区中的电场比靠近源极的漏极P + 区和N + 区之间的本征区强得多。漏电极。然后,漏电流几乎保持不变,这与栅极电压的变化无关。图 4b 显示了 L 的最佳值范围 i 大约为 7–10 纳米,其中 SS 降低到 41 mV/dec 的谷值,并且 \(I_{{{\text{on}}}}{-}I_{{{\text{off}} }}\) 比率增加到几乎 10 8 的最大值 .

一 \(I_{{{\text{ds}}}}{-}V_{{{\text{gs}}}}\) B-TFET 和 b 的特性 SS 和 \(I_{{{\text{on}}}}}{-}I_{{{\text{off}}}}\) 比率与不同 \(L_{i}\) 的变化;用于 L 的拟议 B-TFET 的二维反向偏置电位分布 我 等于 c 20 纳米和 d 100 纳米

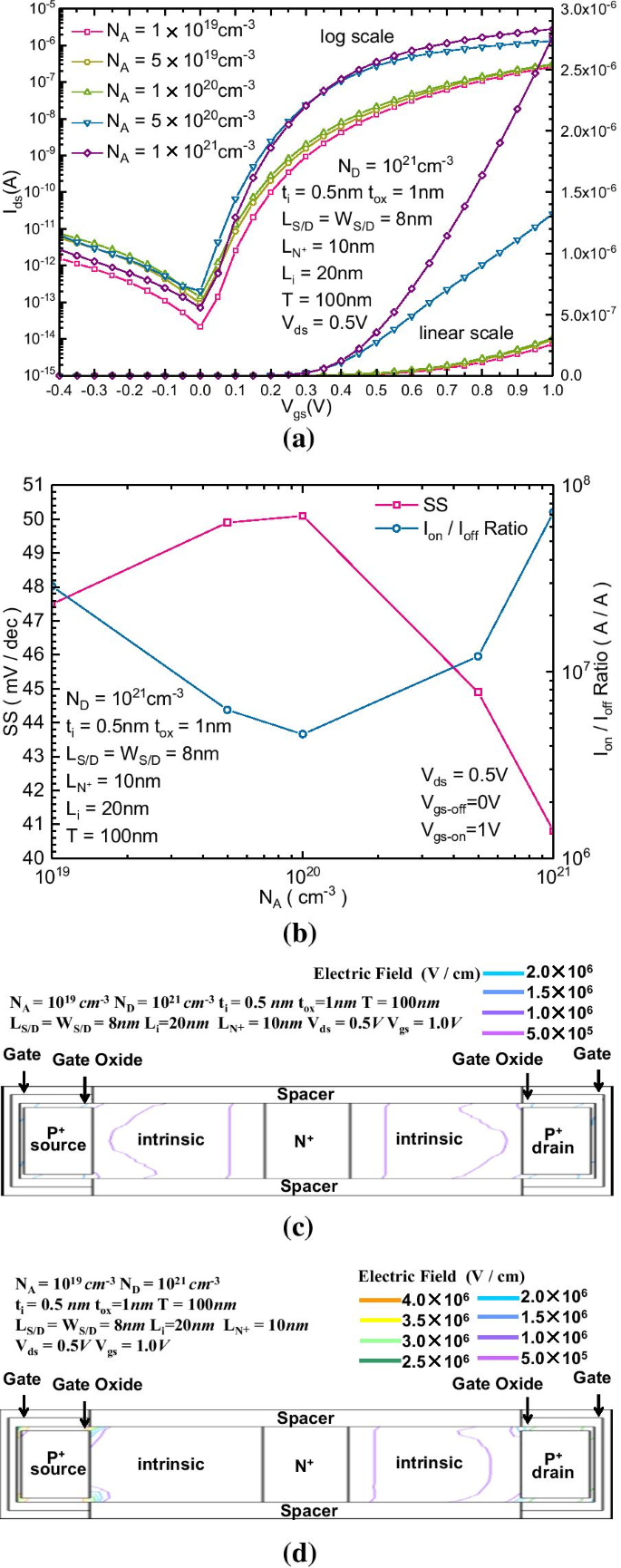

图 5a、b 显示了 \(I_{{{\text{ds}}}}{-}V_{{{\text{ds}}}}\) 传输特性和 SS 和 \(I_{{{ \text{on}}}}{-}I_{{{\text{off}}}}\) 与不同 \(N_{A}\) 的 B-TFET 的比率。图 5a 显示,通过增加 P + 掺杂区域的浓度,我们可以获得更少的 SS 和更大的正向电流。反偏漏电流受\(N_{A}\)的变化影响不明显,但正向电流可以随着\(N_{A}\)的增加而增加。在图 5b 中,SS 和 \(I_{{{\text{on}}}}{-}I_{{{\text{off}}}}\) 比率都可以通过增加}\)。图 5c、d 显示了所提出的 B-TFET 的二维电场分布,其中 \(N_{A}\) 等于 10 19 厘米 −3 和 10 21 厘米 −3 , 分别。 \(N_{A}\) 的增加增强了本征隧道区的电场;然后,可以通过带间隧穿产生更多的电子-空穴对,从而增强所提出的B-TFET的正向电流。

一 \(I_{{{\text{ds}}}}{-}V_{{{\text{gs}}}}\) 传递特性,b SS 和 \(I_{{{\text{on}}}}}{-}I_{{{\text{off}}}}\) 比率的变化与不同 \(N_{A} \)。所提出的 B-TFET 的二维反向偏置电场分布,\(N_{A}\) 等于 (3) 10 19 厘米 −3 和 (4) 10 21 厘米 −3

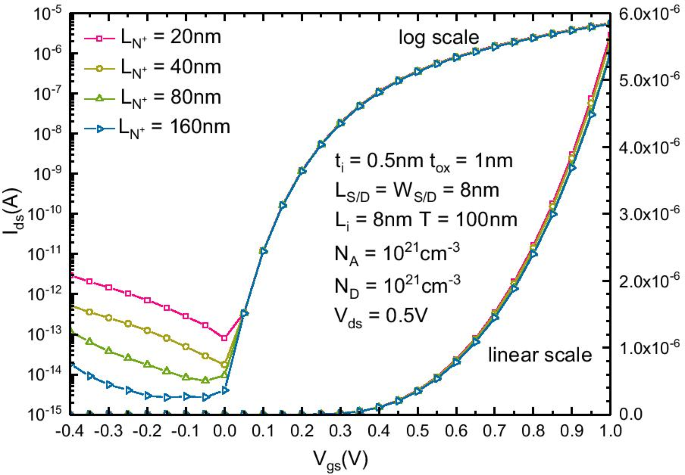

根据上面的讨论,\(N_{D}\) 和\(N_{A}\) 都应该设置为最大可能值。 L的最佳取值范围 i 是 7-10 纳米。但是,静态功耗和 L 之间存在权衡 N+。图 6 显示了具有不同 L<的优化 B-TFET 的 \(I_{{{\text{ds}}}}}{-}V_{{{\text{ds}}}}\) 传输特性/i> N+。 L 可根据不同的静态功耗设计要求选择N+。作为妥协,要确保\(I_{{{\text{on}}}}{-}I_{{{\text{off}}}}\) 比率高于10 8 , LN+ 建议在 20 nm 以上。导通电流增加到大约 6 × 10 –6 A、SS 降低到 38 mV/dec。

\(I_{{{\text{ds}}}}{-}V_{{{\text{ds}}}}\) 不同LN+优化后的B-TFET传输特性

结论

本文分析了一种双边门控S/D对称可互换双向隧穿场效应晶体管的结构参数和内部机制的影响。详细讨论了N + 区域的浓度和长度、P + 和N + 区域之间的本征区域的长度以及P + 区域的浓度等关键参数的影响。与传统的TFET相比,B-TFET具有抗反向偏置漏电流能力强的优点。此后,可以获得良好的性能,例如较低的平均 SS 和较高的 \(I_{{{\text{on}}}}{-}I_{{{\text{off}}}}\) 比率。此外,由于结构对称性和源漏可互换和双向开关特性,使其与CMOS电路更加兼容。

数据和材料的可用性

我们在“竞争利益”下包含了一份声明,说明我们自己和代表我们的合著者可以获得数据和材料。所有可用的数据和材料都是原创作品。稿件中已明确提供所有数据,没有额外的数据和支持材料。

缩写

- L :

-

建议设备的全长

- W :

-

建议设备的整个宽度

- L 我:

-

本征区长度

- L N + :

-

N + 的长度 地区

- L S/D :

-

P + 的长度 源漏可互换区域

- W S/D :

-

P + 的宽度 源漏可互换区域

- \(T\) :

-

硅体厚度

- \(t_{{{\text{ox}}}}\) :

-

栅氧化层厚度

- \(t_{i}\) :

-

S/D区与栅氧化层之间的本征隧道区厚度

- MOSFET:

-

金属氧化物半导体场效应晶体管

- TFET:

-

隧道场效应晶体管

纳米材料

- 肖克利二极管

- 硼烯稳定性和STM图像的第一性原理研究

- TiO2 中金纳米粒子分布对染料敏化太阳能电池光学和电学特性的影响

- 接触非平衡等离子体对 Mn Х Fe3 − X О4 尖晶石结构和磁性能的影响

- 原位退火处理对基于 TIPS-并五苯的有机场效应晶体管的迁移率和形态的影响

- TiO2-水纳米流体在螺旋槽管中的流动和传热特性的实验研究

- TiO2 纳米管阵列:由软硬模板制造和场发射性能的晶粒尺寸依赖性

- Pt/Nd:SrTiO3结中多级电阻开关记忆和记忆状态相关光电压的研究

- 通过尺寸、修饰、缺陷和掺杂设计和调整石墨烯功函数:第一性原理理论研究

- 碳纳米纤维和活性炭作为水性电解质中对称超级电容器的研究:一项比较研究

- 探测 Ag n V (n =1-12) 簇的结构、电子和磁特性

- 天然和合成纳米材料的电化学、生物医学和热特性的比较研究