具有阶梯沟道厚度的双栅极隧道场效应晶体管的仿真研究

摘要

双栅隧道场效应晶体管 (DG TFET) 有望扩展漏电流和亚阈值斜率的限制。然而,它也受到对称源极/漏极架构的双极行为的影响。为了克服双极性电流,必须在源极和漏极之间引入不对称性。在本文中,我们利用 2D 模拟研究了具有阶梯沟道厚度 (SC TFET) 的 DG TFET 的性能。通过阶梯沟道厚度引入源漏不对称;因此,两极行为有望得到缓解。结果表明,与传统的 DG TFET 相比,SC TFET 显示出双极电流的显着降低。彻底讨论了 SC TFET 的机制,以探索物理洞察力。结构参数对起始电压、亚阈值斜率、导通态和双极态漏极电流的影响也体现在确定最优结构中。

背景

随着极端缩放过程的继续,具有传统 MOSFET 的 CMOS 技术遇到了各种挑战,例如不断增加的漏电流和亚阈值斜率 (SS )。隧道场效应晶体管 (TFET) 采用带间隧道 (BTBT) 机制,有望扩展泄漏电流和 SS 的限制 [1,2,3,4,5,6,7,8]。硅基TFET显示出高可靠性和低成本等优势。然而,由于 BTBT 速率受限,传统的硅基 TFET 与 MOSFET 相比具有相对较低的导通电流 [9,10,11]。为了开发基于硅的 TFET 的潜力,最近提出了各种新颖的 TFET 结构来增强导通电流。双栅极 TFET (DG TFET) 显示出更高的 BTBT 速率,从而提高了导通电流 [12,13,14]。然而,DG TFET 的双极电流也增加了,因为 BTBT 速率提高也在双极状态下被激活 [15]。为了进一步克服双极性电流,必须在源极和漏极之间引入不对称性 [16]。具有栅漏重叠和较少漏掺杂浓度的 DG TFET 是缓解双极问题的常用方法 [17,18,19]。但是栅极-漏极重叠需要更大的 S/D 距离,而更低的漏极掺杂浓度会增加串联电阻 [15]。先前的一项工作表明,通过使用低 k 间隔和将触点置于顶部和底部配置 [15],可以进一步减轻具有漏极下重叠的 TFET 中的双极效应,这表明组合不对称策略可能对提高 TFET 的性能。在我们之前的工作中,已经证明鳍片宽度不对称的 FinFET 可以提高 FinFET 的性能 [20]。还认为通道厚度 t si对DG TFET的BTBT率有显着影响[21];因此,源极厚度和漏极厚度之间的不对称性可能会进一步缓解双极电流,需要深入研究。

在本文中,我们研究了具有阶梯沟道厚度的 DG TFET (SC TFET) 的各种性能,通过阶梯沟道厚度引入源漏之间的不对称性,从而有望降低双极电流。本文的其余部分安排如下:第 2 节介绍了器件结构和仿真设置。在第 3 节中,彻底讨论了 SC TFET 的机制。详细讨论了结构参数对传输曲线、起始电压(V 开始),平均SS 并且还介绍了导通/双极状态下的漏极电流。最后,第四部分对本文的研究结果进行了启发。

结构与模拟

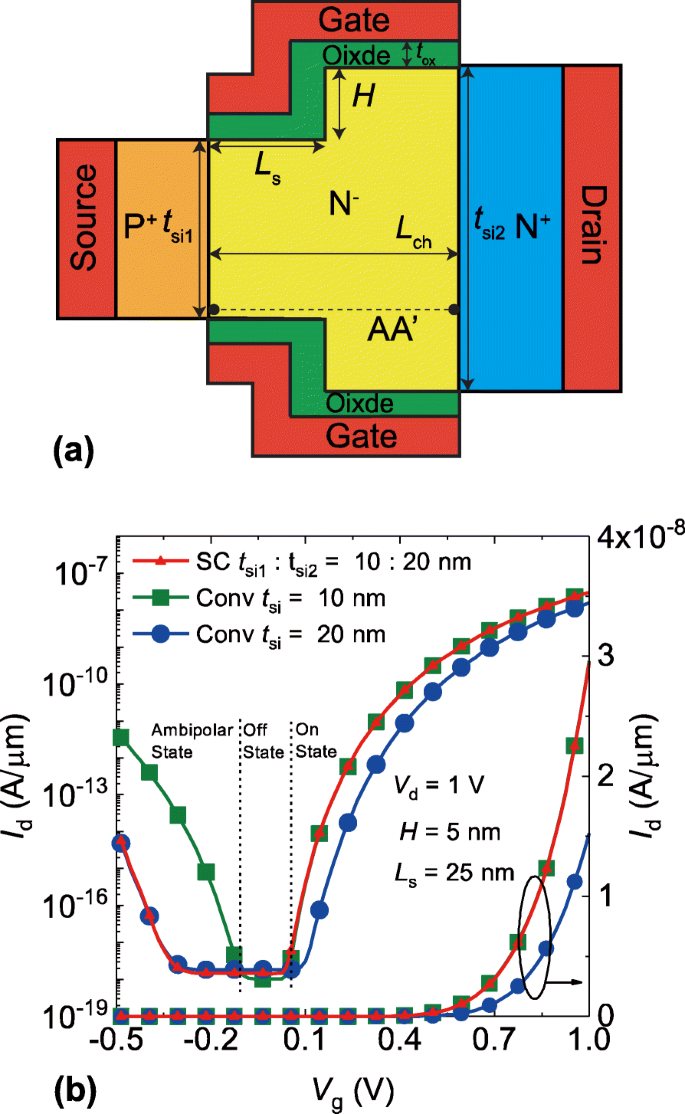

本文考虑的 SC TFET 示意图如图 1a 所示。源区附近的沟道厚度不等于漏区附近的沟道厚度。沟道厚度在沟道区的某一点处逐步变化。台阶高度和台阶位置表示为 H 和 L s 分别。 t si1 和 t si2 分别是源区和漏区附近的沟道厚度。在我们的模拟中,有效氧化物厚度 (EOT) 为 1 nm。源区高度 p 掺杂 (10 20 原子数/cm 3 ) 和漏区是高 n 掺杂 (10 20 原子数/cm 3 ) 以降低串联电阻 [15],沟道区是轻 n 掺杂 (10 17 原子数/cm 3 )。为了分析不同沟道厚度设置的起始电压,金属栅极的功函数固定为 4.5 eV,栅极长度等于沟道长度 L ch 并设置为 50 nm [22,23,24,25]。使用 Sentaurus TCAD 版本 I-2013.12 [26, 27] 进行模拟。掺杂依赖模型和场依赖迁移率模型分别是Philips统一迁移率模型和Lombardi迁移率模型。 Fermi-Dirac 统计、Shockley-Read-Hall 和 Auger 重组模型也被使用。为了考虑高掺杂源极/漏极区,带隙变窄模型被激活。基于 Wentzel-Kramer-Brillouin (WKB) 近似的非局部 BTBT 模型根据 [28] 的实验结果和密度梯度量化模型进行调整,可以实现准确的模拟 [29, 30]。起始电压定义为亚阈值斜率最大时的栅极电压。平均SS 从关态电流中提取到 I d =10 −11 A/μm。

<图片>

一 SC TFET的二维示意图,t si1 和 t si2 是源区和漏区附近的沟道厚度,显然引入了源漏之间的不对称性。切割线 AA' 是沿水平方向的切割线。切割线与源区表面之间的垂直距离为 0.5 nm。 b SC TFET和传统DG TFET的对数和线性标度的传递曲线

结果与讨论

传递曲线和机制

图 1b 分别以对数和线性标度显示了 SC TFET 和传统 DG TFET 的传输曲线。我们在图 1b 中标出了开启状态、关闭状态和双极状态。对于 TFET,总是需要较高的导通电流和较低的双极性电流,这就要求 V 发病和SS 应该是低的,而关断状态应该有一个很宽的电压范围。如图 1b 所示,V 沟道厚度为 10 nm 的常规 DG TFET 的起始时间低于沟道厚度为 20 nm 的 DG TFET。提取的 V t 开始 DG TFET si =10 nm 为 0.04 V 及其提取平均值 SS 为 44.8 mV/dec,V 发病和平均SS 具有 t 的传统 DG TFET si =20 nm 分别为 0.1 V 和 50.6 mV/dec。具有 t 的传统 DG TFET 的漏极电流 与具有 t 的传统 DG TFET 相比,si =10 nm 提高了 94.7% si =20 纳米。这种漏电流改善的主要原因是降低了SS 和 V 发作。然而,具有 t 的传统 DG TFET 的关断范围 si =10 nm 仅为 0.17 V。具有 t 的传统 DG TFET 相比之下,si =20 nm 的截止状态范围为 0.45 V。因此,具有 t 的传统 DG TFET 的双极状态电流 与具有 t 的传统 DG TFET 相比,si =20 nm 减少了 3 个数量级 si =10 纳米。

为了公平比较,t si1 和 t SC TFET 的 si2 分别等于上述传统 DG TFET 的沟道厚度。较窄的通道厚度t SC TFET 的 si1 为 10 nm 和更宽的沟道厚度 t SC TFET 的 si2 为 20 nm。步的位置假定在通道的中间,L s 是 25 纳米。可以观察到 SC TFET 显示出有希望的特性,包括导通状态下的高漏极电流以及宽范围的关断状态。与具有 t 的传统 DG TFET 相比,导通状态下 SC TFET 的漏极电流相似 si =10 nm,平均SS 为 45.8 mV/dec 和 V 起始电压为 0.03 V。然而,与具有 t si =10 纳米。因此,SC TFET 的导通特性与沟道厚度较窄的传统 DG TFET 相似,SC TFET 也显示出与沟道厚度较宽的传统 DG TFET 几乎平行的关断/双极曲线。因此,SC TFET 可以实现低 SS , 降低 V 起效,同时关断范围宽。

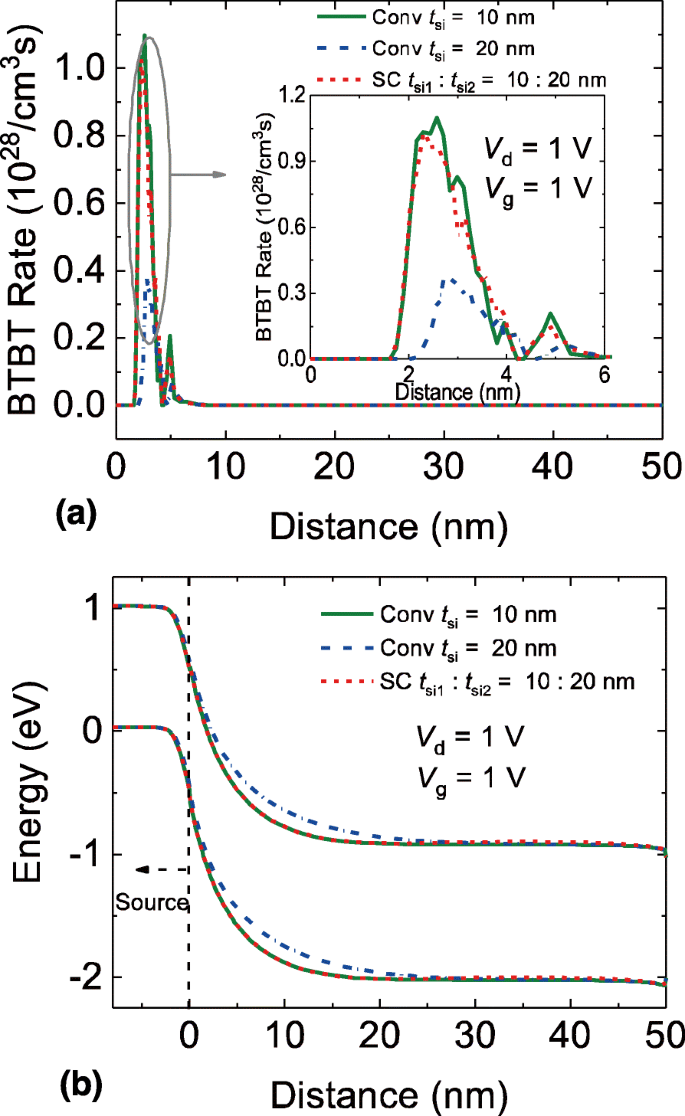

为了探索 SC TFET 的物理机制,我们分别比较了导通状态、接近起始点和双极状态下的 BTBT 速率和能带图。图 2a 显示了 SC TFET 和传统 DG TFET 的 BTBT 速率。可以看出,BTBT 速率强烈依赖于通道厚度。实际上,沟道厚度与BTBT电流的关系I BTBT可以表示为[31]。

$$ {I}_{BTBT}\propto \exp \left(-\frac{4\lambda \sqrt{2{m}^{\ast}{E_g}^{2/3}}}{3\mathrm {\hslash}\left(\Delta \Phi +{E}_g\right)}\right) $$ (1)

一 BTBT 费率和 b SC TFET和常规DG TFET在导通状态下的能带图,距离为图1中切割线AA'的横向位置

其中 λ =(ε sit sit 牛/2ε ox) 1/2 是自然长度,ε si 和 ε ox 分别是硅和氧化物的介电常数,t ox 是氧化物厚度。 ΔΦ 是可以发生隧穿的能量范围,E g 是隧道结处的带隙,m * 是隧道质量。等式 (1) 表明 I BTBT 应该随着 t 增加 si 减少。因此,具有t的传统DG TFET的BTBT率 si =10 nm 应大于具有 t 的传统 DG TFET si =20 纳米。 SC TFET 的 BTBT 速率分布与具有 t 的传统 DG TFET 相似 si =10 纳米。这是因为在导通状态下BTBT主要发生在源结附近,因此源结附近的沟道厚度将决定导通状态的BTBT率。图 2b 显示了 SC TFET 和传统 DG TFET 的能带图。由于 BTBT 速率与隧穿距离有着根本的关系,能带图可以清楚地呈现隧穿距离,将解释 BTBT 速率变化的起源。在图 2b 中,SC TFET 的最小隧穿距离位于源结附近,或多或少等于具有 t 的传统 DG TFET 的最小隧穿距离 si =10 纳米。具有t的传统DG TFET的最小隧穿距离 si =20 nm 明显更宽;因此,与沟道厚度较薄的SC TFET和传统DG TFET相比,其BTBT率有所降低。

图 3a 显示了当栅极电压为零且接近起始电压时的 BTBT 速率。可以看出,SC TFET拥有最高的BTBT率,其次是具有t的传统DG TFET si =10 纳米。具有 t 的传统 DG TFET si =20 nm 显示最低 BTBT 速率。图 3b 展示了相应的能带图。可以观察到从价带到导带的最小距离的位置在沟道区的中心。此外,沟道厚度较宽的常规DG TFET的最小距离大于沟道厚度较薄的SC TFET和常规DG TFET的最小距离。这表明通道厚度对起始点的 BTBT 速率也有显着影响。因此,V 起始时间也取决于通道厚度。另一个事实是,SC TFET 比具有 t 的传统 DG TFET 表现出更高的 BTBT 率 si =10 nm,即使它们的最小通道厚度相等。这种现象归因于栅电极角引入的电位分布的变化,这也可以在其他工作中观察到 [32, 33]。因此,SC TFET 显示出最低的 V 开始,其次是沟道厚度较薄的常规 DG TFET,而沟道厚度较宽的常规 DG TFET 表现出最高的 V 发病。

<图片>

一 BTBT 费率和 b SC TFET和常规DG TFET在近起始点的能带图,距离为图1中AA'切割线的横向位置

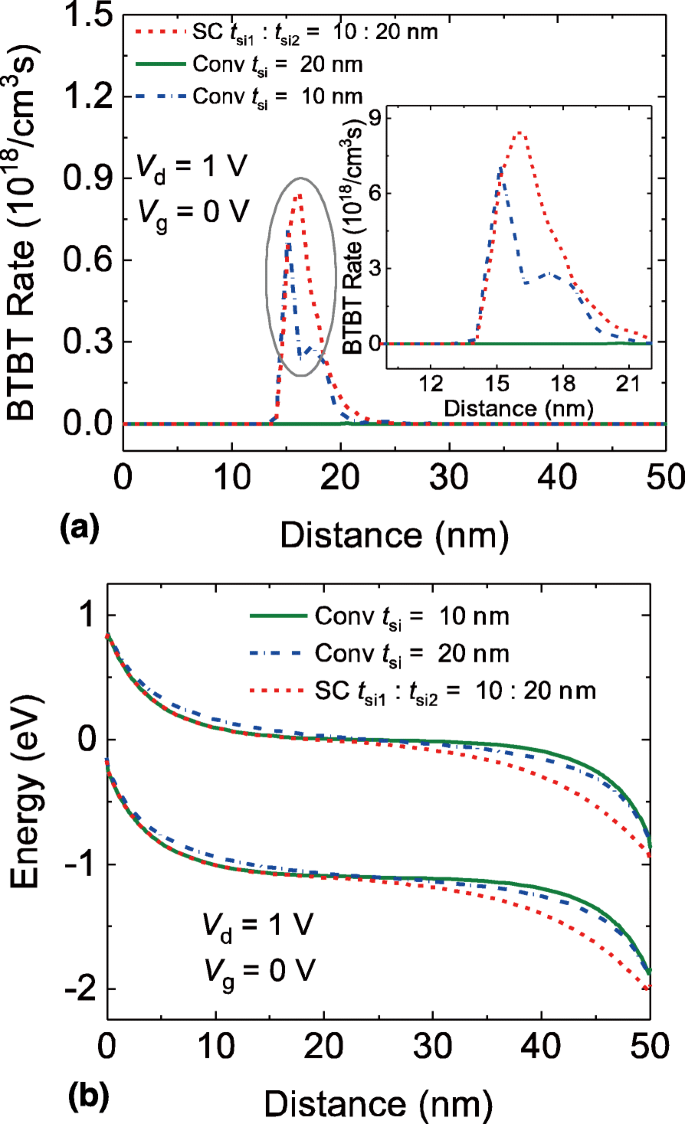

图 4a 显示了双极状态下 BTBT 速率的比较。由于 BTBT 速率强烈依赖于沟道厚度,具有 t 的传统 TFET 与其他两种 TFET 结构相比,si =10 nm 显示出最显着的 BTBT 速率。然而,SC TFET 显示出与具有 t 的传统 DG TFET 相似的 BTBT 速率 si =20 纳米。这是因为隧道效应主要发生在漏区附近,而SC TFET在漏区附近具有较宽的沟道厚度。在图 4b 中,还展示了双极态的能带图。可以清楚地看出,最小隧穿距离位于漏区附近。此外,沟道厚度较宽的SC TFET和常规DG TFET的隧穿距离大于沟道厚度较薄的常规DG TFET,导致SC TFET和沟道厚度较宽的常规DG TFET双极电流较低。 <图片>

一 BTBT 费率和 b SC TFET和传统DG TFET在双极态的能带图,距离为图1中AA’线的横向位置

H 和 LS 对直流特性的影响

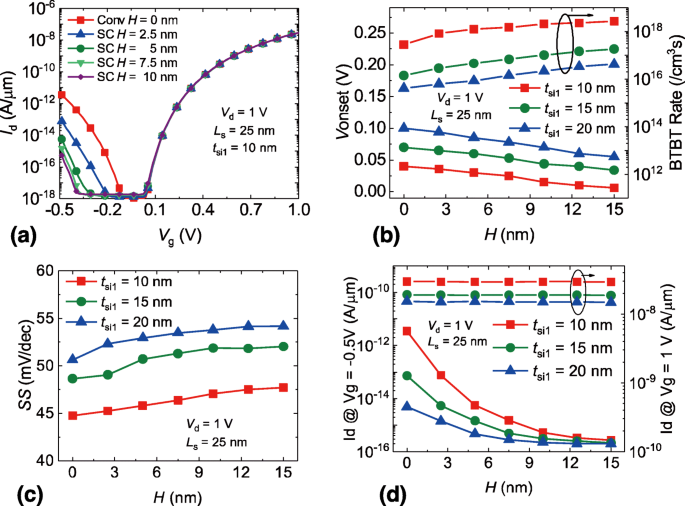

图 5a 显示了具有不同 H 的 SC TFET 的转移曲线 和 t si1 =10 纳米。可以看出,H 对通态电流的影响较小。然而,随着 H 增加,关态范围随着H的增加而提高 以及。还可以看出,随着 H 增加。其原因是双栅结构的耦合效应随着沟道厚度的增加而变得不那么明显[31]。因此,作为 H 增加,BTBT 速率变得更加独立于通道厚度,导致双极性电流饱和。为了进一步探索最优结构参数,H的影响 器件性能从 0 到 15 nm 不等,提取并显示在图 5b-d 中。图 5b 展示了 V 不同H的起始和BTBT速率变化 和 t si1.可以看出,V 起始随着H的增加而单调递减 .这是因为栅电极的拐角会引起沟道区电位分布的变化 [32, 33],导致 BTBT 速率和 V 发作。图 5b 表明 BTBT 率随着 H 的增加而增加 改善。结果,降低的V 随着 H 的增加可以发现开始 .还可以观察到 V 随着 t 的增加,发作增加 si1 增加。主要原因是 t si1 削弱了 BTBT 率,导致更高的 V 发作。在图 5c 中,提取的平均值 SS 具有各种 H 的 SC TFET 和 t 显示了 si1。 SS的趋势 具有不同的 H 与V相反 发作。换句话说,SS 随着 H 上升 增加。我们已经提到通态漏极电流取决于 t si1,因此具有不同 H 的 SC TFET 但具有相同的 t si1 在导通状态下应该具有类似的漏极电流。此外,还知道 V 起始时间随着H的增加而减少 .这意味着驱动相同漏极电流的栅极电压范围比 H 有所改善 增加。结果,平均SS 随着H的增加单调增加 .还可以看出,t的增加 si1 会破坏SS ,这是由于降低了栅极控制能力。图 5d 显示了不同 H 在导通状态和双极状态下的漏极电流 和 t 分别为 si1。导通电流几乎与 H 无关 , 但它受 t 的影响很大 si1,这对应于我们之前的结果,即导通隧道主要发生在源区附近,并且强烈依赖于源区附近的沟道厚度。然而,双极性电流随着 H 增加。由于双极态隧穿在漏区附近占主导地位,H的增加 将改善漏极侧的沟道厚度,从而削弱双极电流。还可以看出,当 H 小于10 nm,这是由于沟道厚度越薄耦合效应越大。

<图片>

H 的影响 在 a 转移曲线,b V 发病率和 BTBT 率,c 平均SS , 和 d 导通/双极状态下的漏极电流,H 是台阶的高度,H =0 nm 代表传统的 DG TFET

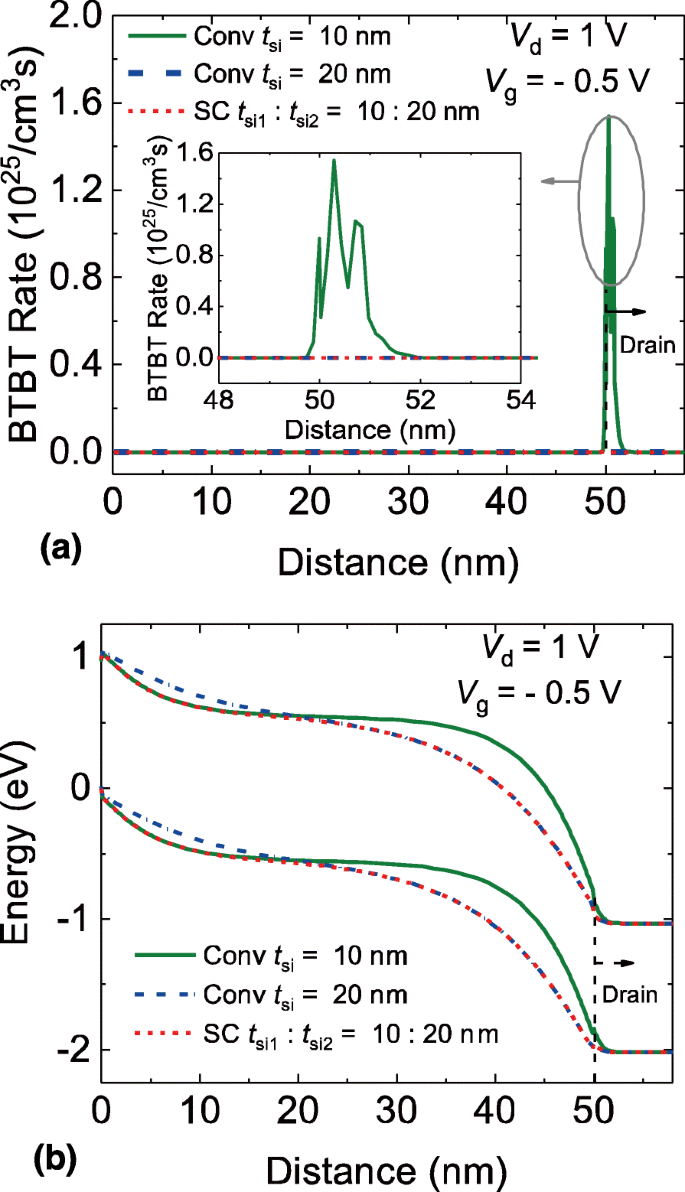

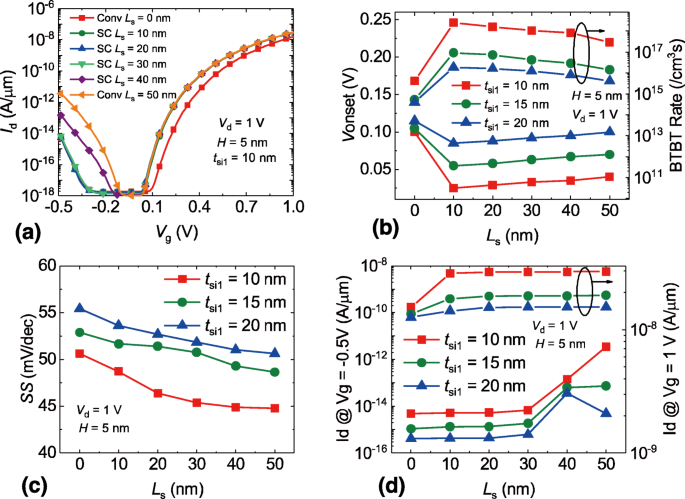

在图 6a 中,不同 L 的 SC TFET 的转移曲线 s 分别呈现。 L s =0 nm 代表具有相应 t 的传统 DG TFET si2 和 L s =50 nm 代表具有相应 t 的传统 DG TFET si1.可以看出,阶跃的位置对双极电流和断态范围有显着影响。带有 L 的 SC TFET 小于 30 nm 的 s 显示出类似的双极性电流和关闭状态范围。作为 L s超过30nm,双极电流大大增强。图 6b 显示了 V 不同 L 的起始和 BTBT 率变化 s 和 t si1, V 的趋势 随着 t 的增加,发作增加 也可以清楚地观察到 si1 的改善。 L 上的变化拐点 s =10 nm 是 t 变化的结果 si1.由于 L s =0 nm 是传统的 DG TFET,沟道厚度较大,BTBT 速率会降低,导致 V 增加 启动和降低的通态电流。除了传统的 DG TFET,V SC TFET 的开始随着 L 单调增加 s 上升,这是由于阶梯沟道结构引起的 BTBT 速率降低。图 6c 展示了 L 的影响 s 和 t SS 上的 si1 SC TFET。增加的 t si1 导致 SS 退化 .根据方程。 (1), 增加沟道厚度会降低栅电极之间的耦合效应,导致栅极控制能力降低和 SS [12]。作为 L s 下降,具有较大沟道厚度的区域将扩大并削弱整体栅极控制能力。结果,减少了 L s 会破坏SS SC TFETs,可以在图6c中清楚地观察到。图 6d 显示了不同 L 在导通状态和双极状态下的漏极电流 s 和 t 分别为 si1。可以观察到 SC TFET 的导通电流或多或少等于传统的 DG TFET 并具有相应的 t si1.至于双极电流,具有 L 的 SC TFET 小于 30 nm 的 s 显示出与具有相应 t 的传统 DG TFET 相似的电流 si2。当 L s 增加到 40 nm,双极电流急剧上升。事实上,对于带有 L 的 SC TFET s =40 nm 和 t si1 =20 nm,其双极电流甚至大于具有 t 的传统 DG TFET si1 =20 纳米。这是因为栅电极的垂直部分可以增强隧道面积,尤其是当栅电极的垂直部分靠近 PN 结时 [34]。它表明 L 为了降低双极性电流,s应小于40 nm。

<图片>

L 的影响 a 上的 s 转移曲线,b V 发病率和 BTBT 率,c 平均SS , 和 d 导通/双极状态下的漏极电流,L s 是源区到台阶的横向距离,L s =0 nm 代表具有相应 t 的传统 DG TFET si2 和 L s =50 nm 代表具有相应 t 的传统 DG TFET si1.

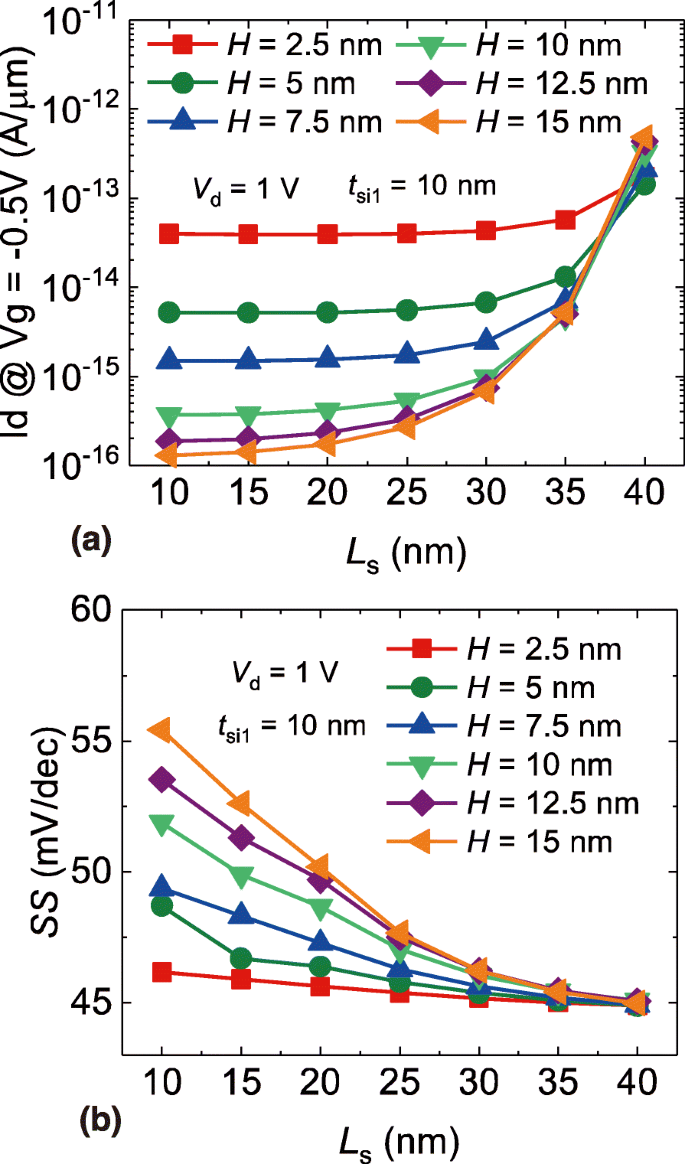

为了确定SC TFET的最佳结构参数,通过研究H的组合效应进行了正交模拟 和 L s 在设备性能上。 t si1 固定在 10 nm 以实现更大的导通电流。在图 7a 中,双极电流被提取为 L 的函数 s 带有各种 H .可以清楚地看到,随着 H 降低,这表明较高的 H 在实现较低的双极电流方面很有希望。但是,可以观察到更大的 H 带来的好处 意义不大。因此,H =15 nm 将是最佳值,因为 H 只能增加设备面积。同时,降低的L s 也会降低双极电流,尤其是 H .因此,较低的 L s 是为了最小的双极电流的目的。尽管如此,较低的L s 也可能导致亚阈值斜率的增加,如图 7b 所示。亚阈值斜率随着 L 的升高而缓慢增加 s 但随着 L 的降低而迅速上升 s,表示一个 L s 约 25 nm 将是折衷值。因此,最佳设备参数将是 H =15 nm 和 L s =25 nm,其中双极电流和亚阈值斜率都相对较低。

<图片>

一 双极电流和b 作为 L 函数的 SC TFET 的亚阈值斜率 S 带有各种 H

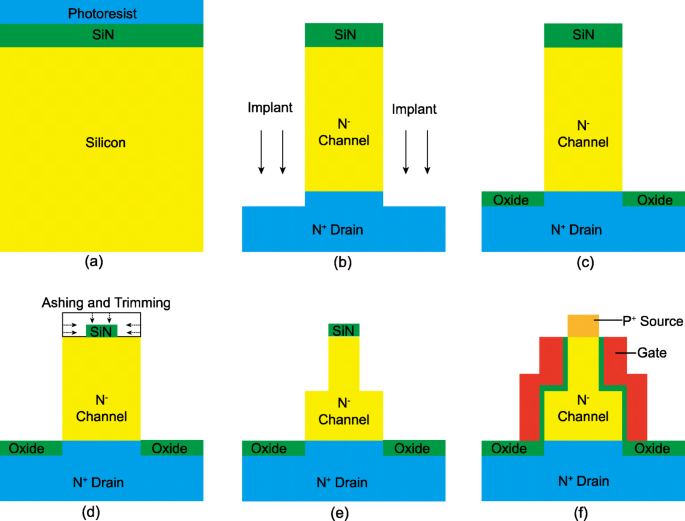

制作方法

SC TFET 的可行制造工艺如图 8 所示。由于沟道的独特形状,采用垂直结构可以更容易地实现阶梯沟道厚度。该过程首先用 SiN 和光刻胶沉积制备硅衬底,如图 8a 所示。在图 8b 中,通过光刻实现 SiN 图案化,然后蚀刻形成沟道区,然后 N + 区域是通过垂直 As 注入和退火引入的 [35]。之后,在后续工艺中沉积隔离氧化物以防止漏区蚀刻,如图8c所示。在图 8d 中,灰化和修整是通过利用反应离子蚀刻 [36] 来减小 SiN 的厚度和宽度。然后通过蚀刻引入阶梯沟道厚度,如图8e所示。其余工艺与传统的垂直TFET类似,包括栅氧化层形成、栅沉积、硅暴露和源区注入[35, 37],如图8f所示。

<图片>

SC TFET的制造工艺。 一 使用 SiN 和光刻胶沉积制备硅衬底。 b 蚀刻、注入和退火。 c 隔离氧化物沉积。 d 通过灰化和修整减少 SiN 的厚度和宽度。 e 引入阶梯通道厚度。 f 栅氧化层形成、栅沉积、栅平面化和源区注入

结论

我们利用 2D 模拟研究了具有阶梯沟道厚度 (SC TFET) 的 DG TFET 的电气性能。通过阶梯沟道厚度引入源漏不对称;因此,两极行为得到显着缓解。 SC TFET 表现出与传统 DG TFET 相似的导通特性,并具有相应的 t 具有相应t的传统DG TFET的si1和并联关断/双极曲线 si2。因此,SC TFET 可以实现宽截止状态范围、低双极电流,并保持低 SS 同时。彻底讨论了 SC TFET 的机制,以探索物理洞察力。还研究了结构参数对起始电压、亚阈值斜率、导通状态下的漏极电流和双极状态的影响,以确定最佳结构。带有 H 的 SC TFET 15 nm 和 L 25 nm 的 s 显示了最佳性能。此外,阶梯通道厚度的结构提供了一种替代的不对称方法。由于组合不对称策略被证明是有效的,我们的工作可以进一步提高 TFET 的性能。

数据和材料的可用性

所有数据完全可用,不受限制。

缩写

- DG TFET:

-

双栅隧道场效应晶体管

- SC TFET:

-

具有阶梯沟道厚度的DG TFET

- SS :

-

亚阈值斜率

- BTBT:

-

带间隧道

- EOT:

-

有效氧化层厚度

- V 开始:

-

起始电压

- H :

-

台阶高度

- L :

-

台阶位置

- L :

-

通道长度

- t 西:

-

通道厚度

- t si1:

-

源区附近沟道厚度

- t si2:

-

靠近漏区的沟道厚度

纳米材料