用于负电容设备和非易失性存储器应用的纳米晶体嵌入式绝缘体 (NEI) 铁电 FET

摘要

我们报告了一种新型纳米晶体嵌入式绝缘体 (NEI) 铁电场效应晶体管 (FeFET),其具有非常薄的统一铁电/电介质 (FE/DE) 绝缘层,有望用于低压逻辑和非易失性存储器。 NVM)应用程序。通过极化电压测量、压电响应力显微镜和电测量证明了包含嵌入非晶 Al2O3 中的正交 ZrO2 纳米晶体的 NEI 层的铁电性质。研究了 NEI 负电容 FET (NCFET) 的温度相关性能和耐久性行为。 FE/DE 厚度为 3.6 nm 的 FeFET 实现了大于 1 V 的存储器窗口,为最终缩小 FE 厚度铺平了道路,以实现鳍片间距非常小的三维 FeFET。

背景

具有铁电栅极绝缘体层 (FeFET) 的场效应晶体管引起了各种集成电路应用的极大兴趣。由于其固有的负电容 (NC) 特性,FeFET 可以实现比传统 MOSFET 更陡峭的开关行为,从而实现更低的电压操作 [1]。各种通道结构 [2,3,4] 和材料 [5,6,7] 已获得亚 60 mV/decade 亚阈值摆幅 (SS)。此外,电流-电压 (I -V ) 剩余极化特性 (P r) 可用于非易失性存储器 (NVM) 应用 [8]。由于其更好的厚度可扩展性 [9] 和 CMOS 工艺兼容性 [2],FeFET 的材料开发最近集中在多晶掺杂的 HfO2 上。然而,HfO2 厚度缩放仍然存在一个基本限制,以避免不希望的栅极漏电流;这反过来又限制了 FinFET [2]。受纳米晶体 MOS 和存储器件概念 [10, 11] 的启发,这项工作中引入了具有嵌入铁电 (FE) 纳米晶体的绝缘电介质 (DE) 层。由此产生的新器件设计如图 1 所示,称为“纳米晶体嵌入式绝缘体”(NEI) FeFET。这种设计的主要优点是更薄的统一 FE/DE 层,满足低栅极泄漏要求。

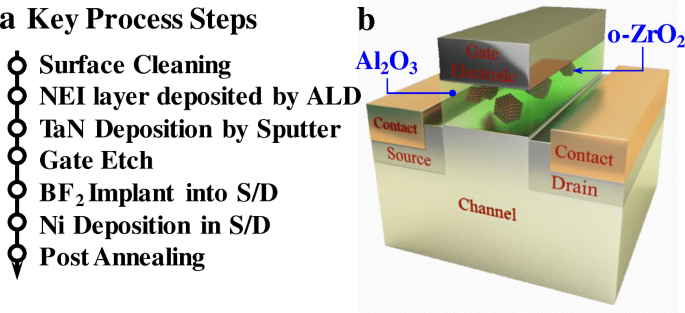

<图片>

一 制造 NEI 铁电场效应晶体管的关键工艺步骤。 b 制备的NEI FeFET 3D示意图

在这项工作中,报告了 NEI FeFET。表征了具有不同物理厚度的 NEI 层的物理性质和铁电性。针对低压逻辑和 NVM 应用研究了 NEI FeFET 的电气性能。

方法

NEI FeFET 制造的关键工艺步骤如图 1a 所示。电阻率为 0.088-0.14 Ω cm 的四英寸 n 型 Ge(001) 晶片用作起始衬底。在使用稀释的 HF 进行预栅极清洁后,将 Ge(001) 晶片装入原子层沉积 (ALD) 室,用于沉积包含嵌入无定形 Al2O3 基质中的 ZrO2 纳米晶体的 NEI 层。在这项工作中使用了具有各种厚度的 NEI 层。使用反应溅射在 NEI FeFET 上沉积 TaN 金属栅极。栅极构图和蚀刻后,BF2 + 以 20 keV 的能量和 1 × 15 cm −2 的剂量将离子注入源/漏区 .使用剥离工艺在源/漏区沉积三十纳米镍 (Ni)。最后,通过快速热退火 (RTA) 完成器件制造。还制作了具有纯介电Al2O3栅极绝缘层的控制金属氧化物半导体场效应晶体管(MOSFET)。

图 1b 显示了制造的 NEI FeFET 的 3D 示意图,其中包含嵌入非晶 DE 栅极绝缘层中的 FE 纳米晶体。虽然FE材料的体积很小,但对于NCFET和NVM应用来说已经足够了。绝缘DE材料是实现低栅极漏电流和低工作电压的关键;它应该具有大带隙能量和高介电常数(κ )。它还应提供高强制场 (E c) 嵌入的FE纳米晶体。

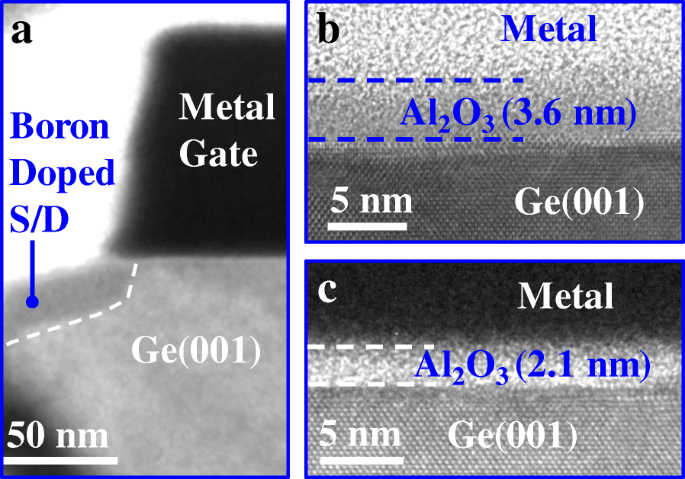

图 2a 中的横截面透射电子显微镜 (XTEM) 图像显示了制造的 FeFET 的源极/漏极、沟道和栅极边缘区域。图 2b 和 c 表示在这项工作中研究的 NEI 层的厚度分别为 3.6 和 2.1 nm。请注意,GeOx 的界面层 NEI层和Ge之间存在,虽然看不到。

<图片>

一 XTEM 图像显示了 NEI-FeFET 的栅极、沟道和源极/漏极区。 b 和 c 分别具有 3.6 nm 和 2.1 nm NEI 层的 FeFET 栅极堆叠的 XTEM 图像

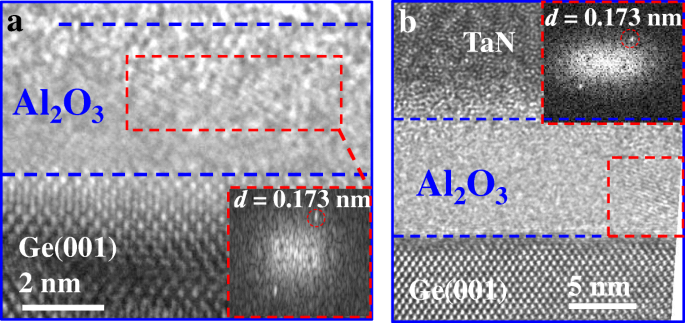

图 3 中的高分辨率 TEM (HRTEM) 图像表明,在 NEI 样品中,厚度为 3.6 和 6 nm 的 ZrO2 纳米晶体嵌入在 Ge(001) 上的非晶 Al2O3 中。在我们之前的工作中,我们已经表明 NEI 层中 Zr 的原子百分比小于 0.5% [12]。根据衍射图,晶面间距d 计算出纳米晶内为 0.173 nm,对应于 (111) 取向的正交 ZrO2 相 [13]。

<图片>

HRTEM 图像显示了厚度为 a 的样品嵌入无定形 Al2O3 中的纳米晶体 3.6 纳米和 b 6 纳米。插图显示面间距 d 在纳米晶中为 0.173 nm,对应于 o-ZrO2(111) 相

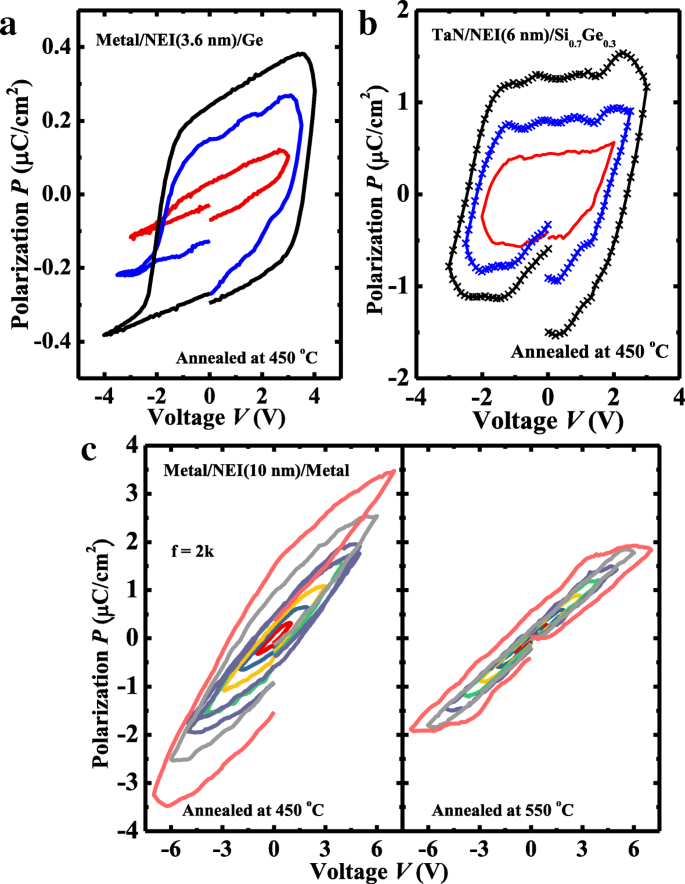

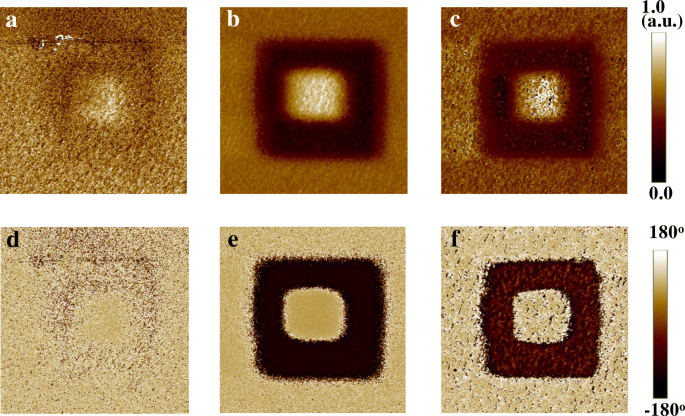

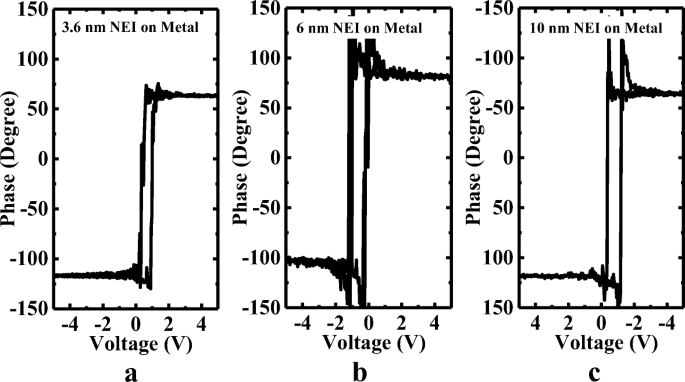

极化与电压 (P -V ) 和压电响应力显微镜 (PFM) 测量在具有不同厚度的 NEI 样品上进行。为了表征 NEI 层的铁电性,P -V TaN/NEI (3.6 nm)/Ge、TaN/NEI (6 nm)/Si0.7Ge0.3 和 TaN/NEI (10 nm)/TaN 电容器的曲线分别如图 4a、b 和 c 所示. NEI 层表现出较低的 P 与 HfZrO2 (HZO) [14] 的报道值相比,这是因为 ZrO2 纳米晶体在 Al2O3 基体中的体积比非常低。可见剩余极化P NEI 薄膜的 r 随着薄膜厚度的增加而增加。 P-V 图 4c 中的曲线表明 NEI 层的铁电性退化,而退火温度从 450°C 增加到 550°C。值得注意的是,未关闭 P-V 的原因 循环是因为确实存在泄漏。据报道,随着电压扫描范围的减小,零电场处的合成偏移会减小 [3, 15, 16]。分别测量了 3.6 nm、6 nm 和 10 nm NEI 的幅度(上)和相位(下)图像,如图 5a、b 和 c 所示。如图 6 所示,随着薄膜厚度的增加,写入到 TaN 上 NEI 表面的指示相反极性的图案表现出更清晰的对比度。

<图片>

一 –c 测量的 P -V TaN/NEI (3.6 nm)/Ge、TaN/NEI (6 nm)/Si0.7Ge0.3和TaN/NEI (10 nm)/TaN的曲线分别

<图片>

一 –c 分别在 TaN 上 3.6、6 和 10 nm NEI 的 PFM 测量的幅度(上)和相位(下)图像

<图片>

一 –c 分别为 3.6、6 和 10 nm NEI 在 TaN 上的相变特性。观察到可以在NEI层表面写入相反的极性

结果与讨论

NEI NCFET

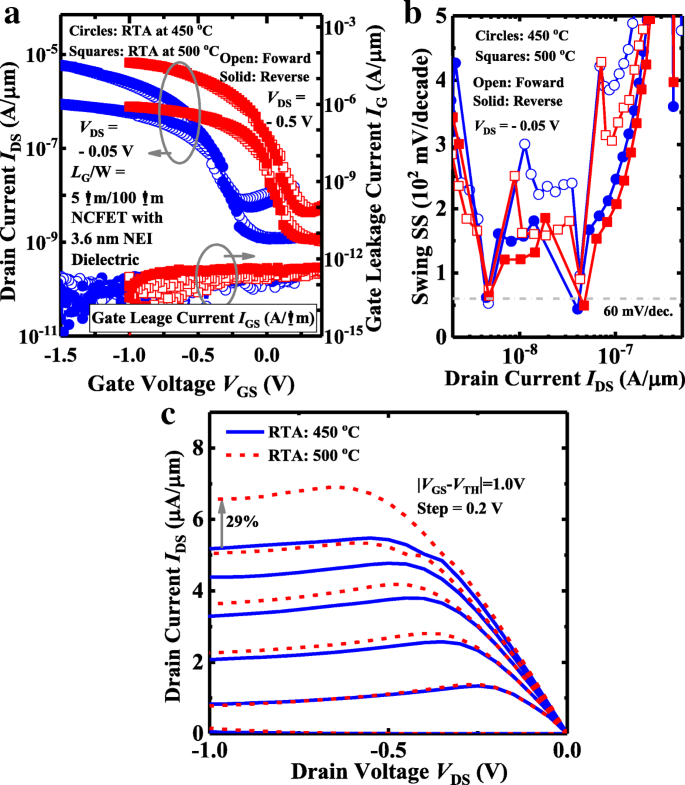

图 7a 显示了测量的 I DS-V NEI 厚度为 3.6 nm 的 NEI NCFET 在 450 °C 和 500 °C 下退火的 GS 曲线。 NCFET 表现出很小的滞后,表明铁电电容和晶体管中的 MOS 电容之间的匹配良好。 NCFET 显示顺时针方向诱导的 NC 效应 I-V 循环,这与通过电荷俘获/释放 [17] 的逆时针循环相反。栅极泄漏 I G 作为 V 的函数 同一对器件的 GS 表明在 Al2O3 中形成纳米晶体不会增加栅极泄漏。图 7b 显示 NCFET 实现了正向和反向扫描的低于 60 mV/十倍频程的陡峭 SS 点。 NEI NCFET 中的 SS 波动,也在 NC FinFET [2, 18] 中观察到,可能是由于不同铁电纳米晶体或域的极化切换。测量的 I DS-V 图 7c 中同一对器件的 DS 曲线表明,在 ∣V GS − V TH ∣ =∣ V DS ∣ =1.0 V,在 500 °C 下具有 RTA 的 NCFET 实现了 29% 的更大 I DS 与在 450 °C 下退火的晶体管相比。这是因为随着退火温度的升高,沟道中的载流子迁移率和接触电阻特性可以得到改善[19]。在 I 中观察到由铁电层引起的典型特性,即负微分电阻 (NDR) DS-V 不同温度退火NCFET的DS曲线。

<图片>

一 测量 I DS-V GS 和 I G-V 具有 3.6-nm NEI 的 NCFET 在 450 °C 和 500 °C 下退火的 GS 曲线。 b NEI NCFET 对于 V 具有低于 60 mV/decade 的点 DS 值为 − 0.05 V。c 我 DS-V NEI NCFET 的 DS 曲线显示了明显的 NDR 现象。在 500 °C 下退火的 NC 晶体管达到 29% I 在 450 °C 和 1.0 V 电源电压下,与带有 RTA 的器件相比 DS 改进

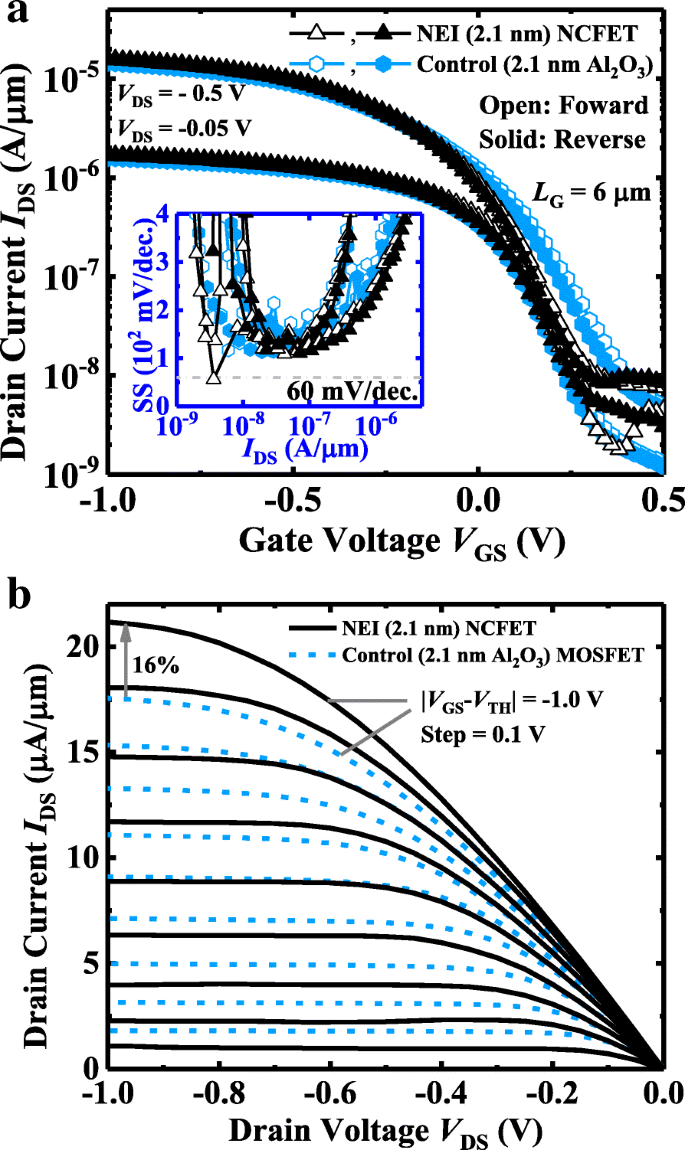

图 8a 显示了测量的 I DS-V NEI NCFET 和具有相同绝缘体厚度 2.1 nm 的控制 MOSFET 的 GS 曲线。设备有一个 L G 为 6 微米。 NCFET 表现出无滞后特性。插图显示点 SS 与 I 器件的 DS 曲线,表明与控制器件相比,NCFET 实现了改进的 SS,达到阈值电压。图 8b 显示了 I DS-V NEI NCFET 和控制 MOSFET 的 DS 曲线。 NCFET 对于低 V 表现出 NDR 现象 GS。与控制 MOSFET 相比,NDR 效应对应于 NCFET 中改进的漏极感应势垒降低 (DIBL) 特性,如图 8a 所示。在 ∣V GS − V TH ∣ =∣ V DS ∣ =1.0 V,16% I 与控制器件相比,在 NCFET 中获得了 DS 增强。与具有 3.6 nm NEI 的晶体管相比,具有 2.1 nm NEI 的 NCFET 的 NDR 不太显着,这与 [20] 中的结论一致。

<图片>

一 我 DS-V 具有纯 Al2O3 电介质的 NEI NCFET 和控制 MOSFET 的 GS 曲线。两种器件都具有 2.1 nm 栅极绝缘体。插图显示,在阈值电压之前,NCFET 比控制器件具有更陡峭的 SS。 b 测量 I DS-V NCFET 和控制 MOSFET 的 DS 曲线。在非常低的 V 下观察到 NCFET 的 NDR GS。在 ∣V GS − V TH ∣ =∣ V DS ∣ =1.0 V,NCFET 达到 16% I 与控制装置相比DS的改进

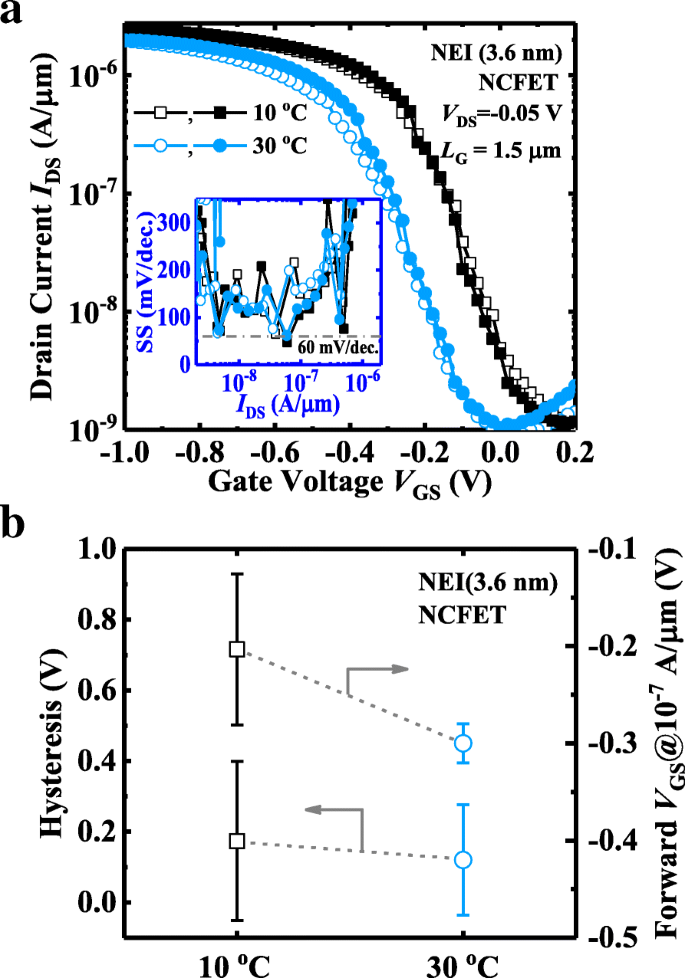

本文研究了具有 3.6 nm 厚 NEI 的 NCFET 的温度依赖性。图 9a 显示了 I DS-V 在 10 °C 和 30 °C 下测量的 GS 曲线。插图表明晶体管的 SS 性能在升高的温度下不会降低。随着温度的升高,I -V 曲线移动到更负的 V GS 由于铁电性的主导效应,这与传统 MOSFET 的趋势相反。图 9b 总结了滞后电压和正向开关阈值电压随温度的变化。前进 V 随着温度升高,GS 向更多负值移动,这可能是由于 E 的增加 国家能源部的 c。

<图片>

一 我 DS-V 在 10 °C 和 30 °C 下测量的 NEI (3.6 nm) NCFET 的 GS。正如预期的那样,曲线显示随着温度升高而向负电压移动。插图显示陡峭点 SS。 b 滞后(左)和正向 V 的统计图 GS @ 10 −7 具有 3.6-nm NEI 层的 NCFET 的 A/μm(右)。前进 V GS随温度升高而向负方向移动

用于非易失性存储器应用的 NEI FeFET

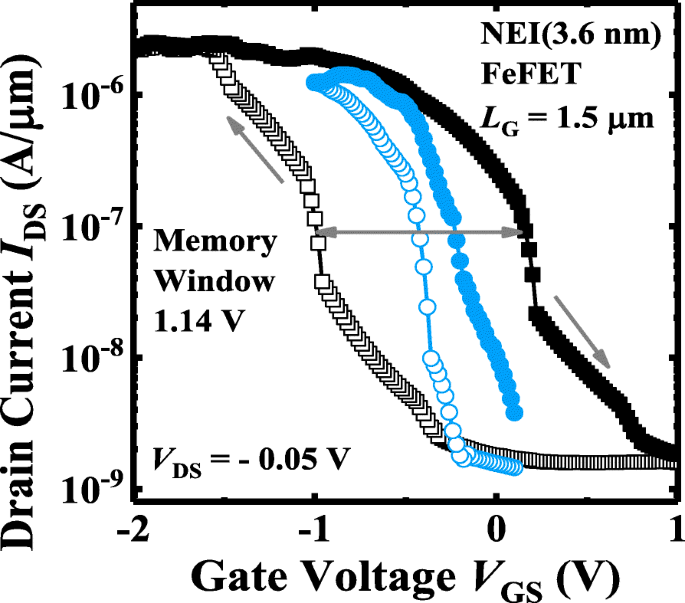

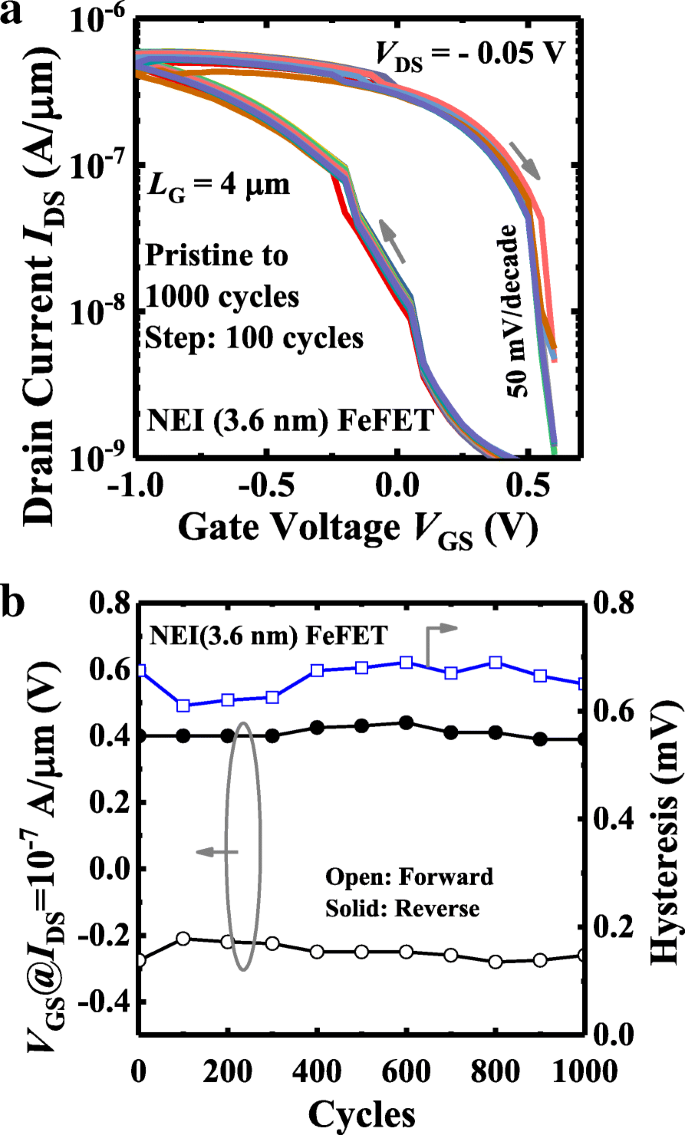

通过增加 V 的范围 GS 扫描,可以增加 NEI FeFET 的滞后电压,以实现用于读写操作的大而稳定的存储窗口 (MW)。如图 10 所示,具有 3.6-nm NEI 的 FeFET 表明随着 V MW 从 0.2 V 增加到 1.14 V GS 扫描范围从 (0.1 V, − 0.1 V) 到 (1 V, − 2 V)。另一个 FeFET 存储器件的 DC 扫描耐久性如图 11a 所示,图 11b 说明了作为 DC 扫描周期数的函数的滞后特性。稳定的I-V 可见~ 0.65 V的滞后窗口。

<图片>

对于大 V GS DC 扫描范围,NEI (3.6 nm) FeFET 的 MW 为 1.14 V

<图片>

一 测量 I DS-V NEI (3.6 nm) FeFET 的 GS 曲线,通过 1000 次直流扫描循环。 b 直流扫描耐久性测量表明NEI FeFET在1000次循环后具有稳定的MW

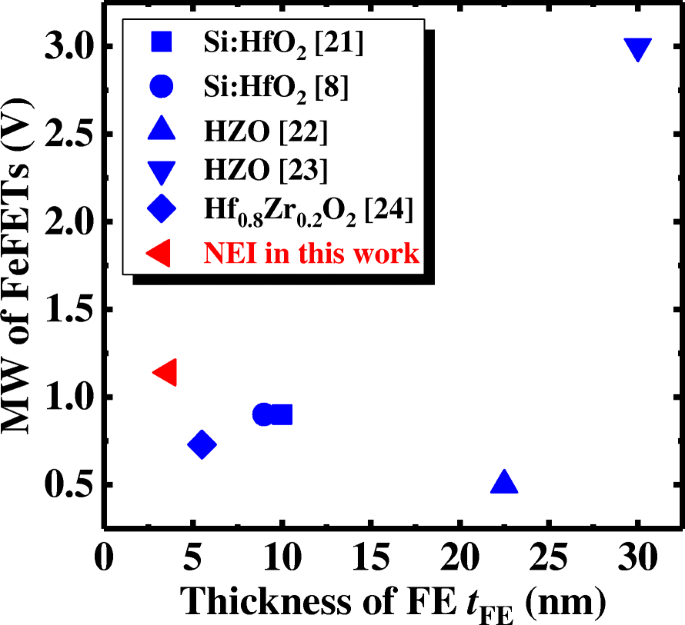

图 12 就 MW 和 FE 层厚度 [8, 21–24] 对 NEI FeFET 存储器件与报道的 FeFET 进行了基准测试。应该注意的是,这项工作中的 NEI FeFET 器件实现了相当大的 (> 1 V) MW,据报道的最薄 FE 厚度为 3.6 nm。我们推测与掺杂的 HfO2 相比,更容易在 NEI 中以更小的厚度实现稳定的 FE 相 [28,29,30]。

<图片>

就 MW 和 t 对 NEI FeFET 存储器件与已报道的 FeFET 进行基准测试 FE。 NEI FeFET存储器件实现最薄的FE

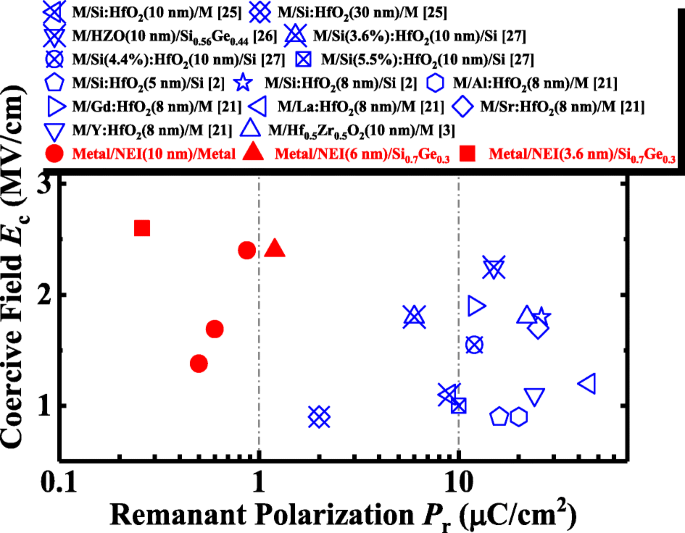

最后,讨论了嵌入在非晶栅极绝缘体中的 ZrO2 纳米晶体所提供的 NEI FeFET 的优点。图 13 将 NEI 层与已报道的掺杂 HfO2 薄膜 [2, 3, 21, 25–27] 相对比,关于 E c 和 P 河NEI 可以实现更低的 P r 与类似 E 的掺杂 HfO2 相比 C。我们的实验表明,P r 低于 1 μC/cm 2 可以在 FeFET 中提供所需的 MW。过度极化可能导致更大的去极化,导致更差的保留特性,这在 [25] 中有所报道。此外,NEI 层的 FE 和 DE 属性可以单独调整:P r 通过增加/减少 FE 纳米晶体的体积而增加/减少,而 κ 通过在非晶基质中加入其他元素(例如. , LaAlO3), 以优化 FeFET 性能。

<图片>

NEI 层与报道的掺杂 HfO2 薄膜的基准测试,关于 E c 和 P 河NEI 实现了更低的 P r 与掺杂 HfO2 相比,同时保持相似的 E C。 [2, 3, 21, 25,26,27]

结论

报道了在非晶 Al2O3 栅极绝缘层中嵌入 ZrO2 纳米晶体的新型 FeFET。物理分析表明,Al2O3 中少于 0.5% 的 Zr 可为 NCFET 和 NVM 应用产生足够的铁电性。在不同的测量温度下观察到稳定的 NC 效应。展示了具有创纪录的薄(3.6 纳米总厚度)栅极绝缘体的稳定 FeFET 存储器操作。超过 1000 次 DC 耐久循环可实现稳定的 MW。提议的 NEI FeFET 设计为缩小 FE/DE 栅极绝缘层的厚度以与具有非常小鳍间距的 FinFET 兼容提供了途径。

缩写

- Al2O3 :

-

氧化铝

- ALD:

-

原子层沉积

- BF2 + :

-

硼氟离子

- DC:

-

直流电

- Ec:

-

强制领域

- FeFET:

-

铁电场效应晶体管

- 哥:

-

锗

- GeOx :

-

氧化锗

- 高频:

-

氢氟酸

- HRTEM:

-

高分辨透射电子显微镜

- I DS :

-

漏电流

- MOSFET:

-

金属氧化物半导体场效应晶体管

- MW:

-

内存窗口

- NC:

-

负电容

- NDR:

-

负差分电阻

- NEI:

-

纳米晶嵌入绝缘体

- Ni:

-

镍

- Pr:

-

剩余极化

- RTA:

-

快速热退火

- SS:

-

亚阈值摆动

- TaN:

-

氮化钽

- V 高:

-

栅极电压

- V :

-

阈值电压

- 氧化锆:

-

二氧化锆

纳米材料

- 传感器和处理器融合用于工业应用

- 用于改进诊断和治疗应用的多功能金纳米粒子:综述

- 用于合成和生物医学应用的荧光纳米材料的进展和挑战

- 用于 Micro-LED 和 VCSEL 的高级原子层沉积技术

- 用于超级电容器应用的石墨烯和聚合物复合材料:综述

- 石墨烯/WO3 和石墨烯/CeO x 结构作为超级电容器应用电极的评估

- V/SiOx/AlOy/p++Si 器件作为选择器和存储器的双重功能

- 蚀刻变化对 Ge/Si 沟道形成和器件性能的影响

- 双层 CeO2−x/ZnO 和 ZnO/CeO2−x 异质结构和电铸极性对非易失性存储器开关特性的影响

- 工业制冷和工业冷却应用驱动器

- 用于镗削和车削应用的摆动车床

- 用于医疗器械应用的特种金属