具有改进性能的新型无掺杂鳍状 SiGe 沟道 TFET

摘要

在本文中,提出并研究了一种无掺杂鳍状 SiGe 沟道 TFET (DF-TFET)。为了形成高效的无掺杂线隧道结,引入了鳍状 SiGe 沟道和栅极/源极重叠。通过这些方法,可以获得具有高导通电流、12个数量级开关比且无明显双极效应的DF-TFET。高 κ 诱导材料堆叠栅极电介质以改善 DF-TFET 的断态泄漏、界面特性和可靠性。此外,通过使用无掺杂的沟道和鳍结构,可以解决掺杂工艺和非对称栅极重叠形成的困难。因此,DF-TFET的结构可以具有良好的制造适用性并显着减少占用空间。本文研究了器件的物理机制和参数对性能的影响。最后,通态电流 (I ON) 为 58.8 μA/μm,最小亚阈值摆幅为 2.8 mV/dec (SSmin),可以获得 18.2 mV/dec 的平均亚阈值摆幅 (SSavg)。通过改进电容特性,可以获得 5.04 GHz 的截止频率和 1.29 GHz 的增益带宽积。 DF-TFET 具有更高的性能和稳健性,非常适合超低功耗应用。

介绍

随着 MOSFET 的缩小,集成电路 (IC) 的开关速度、高频性能、密度、成本和功能都有很大的提高[1]。但随着电压缩小的不断进步,不可接受的高功耗成为现代IC的一个严重问题[1, 2]。受益于带间隧道机制,具有陡峭 SS 和低功耗的隧道场效应管 (TFET) 为这一问题带来了新的解决方案并引起了广泛关注 [3,4,5,6,7,8,9 ]。但是传统的硅基 TFET 的应用受到相当低的导通电流 (I ON)、低开关比、严重的双极性效应和大的平均亚阈值摆幅 (SS) [1, 7]。为了提高 TFET 的性能,近年来提出了在 TFET 上应用新结构和新材料的建议。例如,近年来提出了具有隧道速率增强层的 TFET [5, 10, 11]。有了这一层,隧道路径的有效长度减少,导致隧道速率明显提高。此外,许多研究小组对具有改进栅极结构的 TFET 进行了研究 [12,13,14,15,16,17,18,19,20]。 L-TFET [17,18,19] 中引入了线隧穿的概念。因此,SSavg 为 42.8 mV/decade 和 I ON 10 −6 A/μm 可以通过 L-TFET 实现。为了进一步提高 TFET 的性能,报道了一种具有 T 形重叠和双源的改进型 TG-TFET [20, 21]。结果,I TG-TFET 的导通达到 81 μA/μm。为了进一步提高器件性能,对隧道结的掺杂分布有很高的要求。代工工程师需要创建一个只有几纳米厚的超陡峭的结,这是很难实现的。为了避免这个困难,研究小组报告了使用电荷等离子体概念在薄本征半导体薄膜上的无掺杂 TFET (DL-TFET) [22, 23]。在 DL-TFET 中,通过去除超陡峭的突变结,可以显着降低制造难度。可以避免随机掺杂波动引起的性能下降。此外,DL-TFET 的制造不需要高热预算来创建源极和漏极,这开辟了在其他衬底(如玻璃单晶硅)上实现 TFET 的可能性。因此,DL-TFET 的 SS 得到了极大的改善。然而,由于点隧穿结效率低,DL-TFET的电流不够大,难以满足现代电路应用日益增长的要求。

在本文中,提出并研究了一种新型的无掺杂鳍状 SiGe 沟道 TFET (DF-TFET)。为了提高器件的性能和稳健性,DF-TFET 采用了线隧道结和 SiGe 材料。同时,优化栅极金属功函数以进一步提高隧穿率。此外,无掺杂沟道降低了制造工艺难度,而鳍状结构使得非对称栅/背栅制造适用。结果,导通电流 (I ON) 为 58.8μA/μm,断态漏电流 (I OFF) 接近 10 −11 μA/μm,DF-TFET 可以达到 18.2 mV/dec 的平均亚阈值摆幅 (SSavg) 和 2.8 mV/dec 的最小亚阈值摆幅 (SSmin)。栅极电容相对较小 (C gg) 和栅漏电容 (C gd),可以获得良好的模拟/射频性能。最后,截止频率 (f T) 达到 5.04 GHz,增益带宽积 (GBW) 达到 1.29 GHz。

本文的结构如下:“器件结构与仿真方法”部分展示了本文的TCAD仿真方法。介绍了DF-TFET的结构和参数。说明了 DF-TFET 与 DL-TFET 和 TG-TFET 相比的差异和优势。 “结果与讨论”部分讨论了 DF-TFET 的机制、特性和模拟/RF 性能。本节对 DF-TFET、DL-TFET 和 TG-TFET 进行了性能比较。此外,本节还研究了器件参数对性能和 DF-TFET 典型射频参数的影响。为了进一步了解DF-TFETs在超低功耗应用中的潜力,对不同TFETs与DF-TFETs在低电压偏置下的电学特性进行了比较。

设备结构及仿真方法

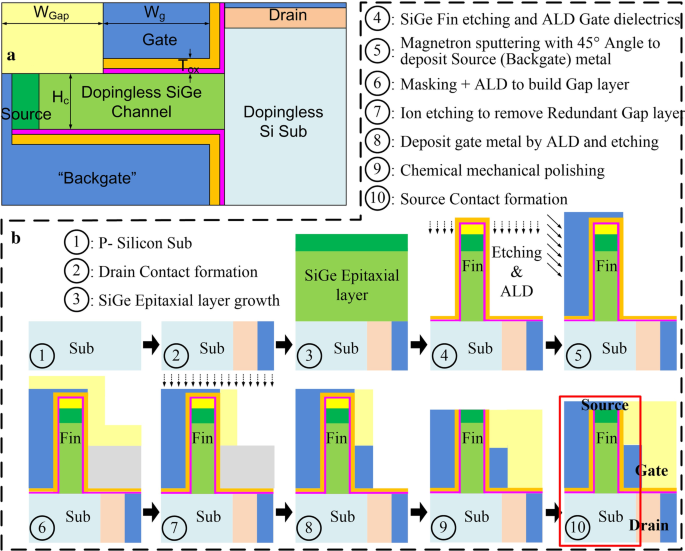

DF-TFET 的建议结构如图 1a 所示。为了提高器件性能,通过电荷等离子体概念,将线隧道结应用于无掺杂鳍状 SiGe 沟道 [24, 25]。众所周知,栅极电介质厚度会显着影响隧道电流。这是因为在 WKB 近似 [26] 的结果中,如等式所示。 (1)、隧穿概率取决于有效屏蔽长度(λ ), 有效载流子质量 (m * ), 能带隙 (E g) 和有效屏蔽能量窗口 (ΔΦ ).

$$T_{{{\text{WKB}}}} \approx \exp \left( { - \frac{{4\lambda \sqrt {2m^{ * } } \sqrt {E_{{\text{g} }}^{3} } }}{{3q\hbar (E_{{\text{g}}} + \Delta \Phi )}}} \right)$$ (1) <图片>

一 结构和b DF-TFET制作流程

减少栅极电介质的厚度或使用高 κ 电介质会降低λ 并增加ΔΦ ,这将导致隧道概率呈指数增长。因此,使用高 κ 电介质和减小电介质厚度可以显着增加 TFET 的导通电流。但高κ的介质厚度小和界面质量问题 电介质会导致严重的可靠性问题。因此,设置 0.5 nm 的 Al2O3 和 2.0 nm 的 HfO2 的堆叠栅极电介质以保证良好的界面质量 [27,28,29],这可以显着降低漏电流并提高栅极电介质的可靠性。源极位于鳍结构的顶部。同时,它也靠近鳍片的一侧,用作施加零偏置的“背栅”。通过使用具有不同金属功函数的栅极和源极电极,可以通过电荷等离子体概念在无掺杂鳍状 SiGe 沟道中形成线隧道结。带间隧穿 (BTBT) 方向垂直于沟道/栅极表面。这有助于增加I 通过提高有效隧道结面积来实现导通。

高开关比 (I ON/I OFF) 由于大的导通电流 (I ON) 和小断态电流 (I OFF) 由线隧道结提供。此外,与平面线隧道 TFET 相比,在 DF-TFET 中应用鳍状结构可以显着减少占位面积 [30, 31]。图 1b 显示了形成 DF-TFET 结构的可用制造流程。表1显示了DF-TFET的主要工艺参数。最后,无需制作陡峭且均匀的突变 p-n 结,即可实现良好的器件性能和鲁棒性。

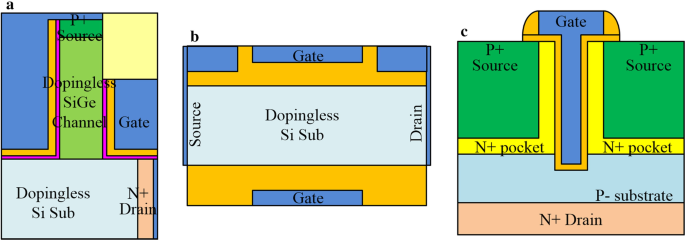

为了更好地理解 DF-TFET、DL-TFET 和 TG-TFET 的差异和优势,图 2 显示了这三种器件的结构。通过线隧道结,L-TFET 和 TG-TFET 有望获得高导通电流。但实验结果表明,L-TFET 的实际性能并没有预期的那么高 [18, 19]。最重要的原因之一是难以形成具有完美界面特性的陡峭且均匀的突变 p-n 结。 TG-TFET在L-TFET结构的基础上,对I做了很大的改进 在。但是 TG-TFET 仍然面临着形成完美的突变 p-n 结的困难。因此,为了获得理想的良好性能,应该获得只有几纳米厚的陡峭且均匀的突变 p-n 结,但在制造过程中很难实现。通过使用无掺杂沟道,DL-TFET 可以避免这个问题,并在隧道结附近带来更好的界面质量。然而,与具有突变 p-n 结的线隧穿 TFET [16,17,18,19,20,21] 相比,仿真结果表明 I DL-TFET 的 ON 相对较低 [22, 23]。为了进一步改进,本文提出并研究了DF-TFET。

<图片>

a 的结构 DF-TFET,b DL-TFET,c TG-TFET

DF-TFET 的模拟在 Silvaco Atlas TCAD 工具中进行。本次模拟引入了非局部BTBT模型,将能带空间变化考虑在内,有助于提高BTBT隧穿过程的精度。 Lombardi 迁移率模型被认为使信道迁移率准确。考虑带隙变窄模型拟合重掺杂欧姆接触区,本文也考虑了Shockley-Read-Hall复合模型。

结果与讨论

DF-TFET、DL-TFET和TG-TFET的机理与比较

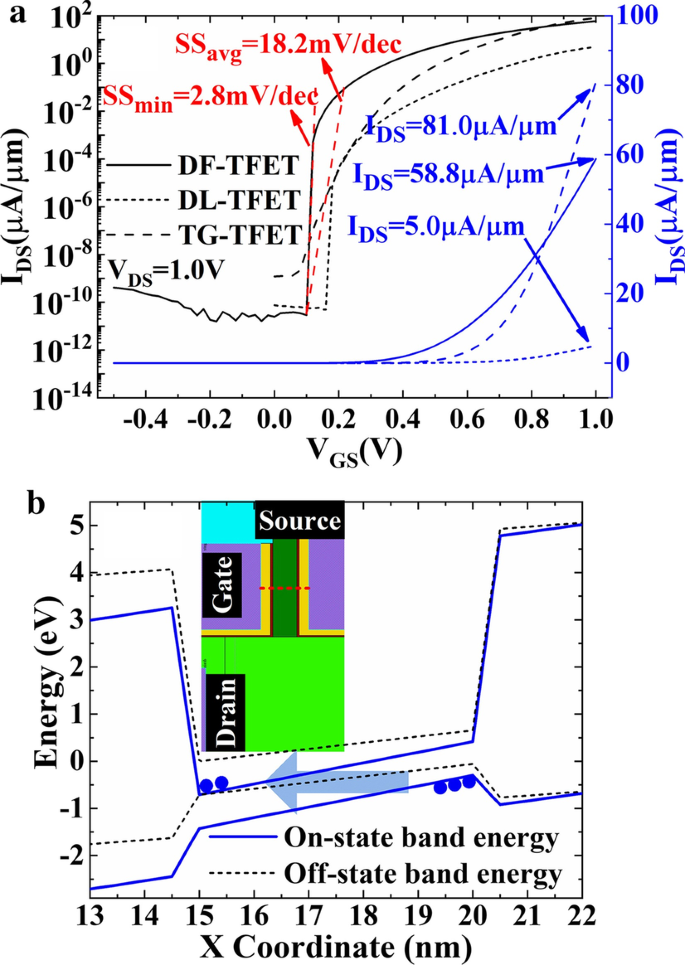

图 3a 显示了 DF-TFET、DL-TFET 和 TG-TFET 的传输特性比较。受益于鳍状 SiGe 沟道中的线隧道结,DF-TFET 达到导通电流 (I ON) 为 58.8 μA/μm,并实现了超过 12 个数量级的大开关比,而不会发生明显的双极效应。此外,获得了 2.8 mV/dec 的最小亚阈值摆幅 (SSmin) 和 18.2 mV/dec 的平均亚阈值摆幅 (SSavg)。因此,DF-TFET在I上有明显的提升 ON 与 DL-TFET 相比,亚阈值摆幅与 TG-TFET 相比。 我 在 V 处,DF-TFET 的导通比 DL-TFET 大一个数量级以上 DS =V GS =1 V。图 3b 显示了 DF-TFET 的能带条件,并说明了鳍形沟道中隧道窗口的形成。图 3b 插图中的红色虚线表示获得能带曲线的位置。

<图片>

一 DF-TFET、DL-TFET 和 TG-TFET 的传输特性。 b DF-TFET在不同工作条件下的能带情况(插图为切割线位置)

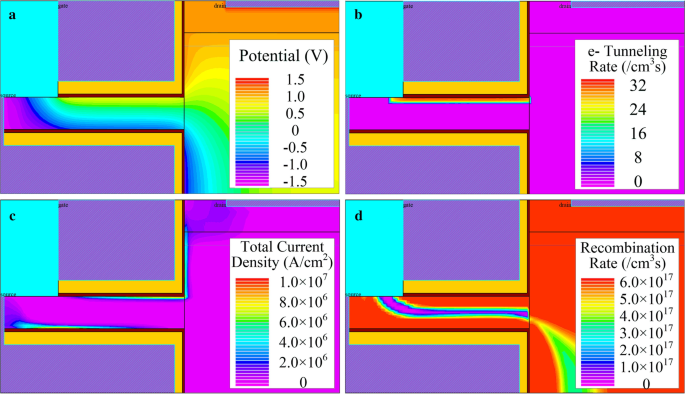

DF-TFET 隧穿过程中重要物理量的分布如图 4 所示,其中包括 (a) 电位、(b) e 隧穿率、(c) 总电流密度和 (d) 复合率的分布。州内工作条件。在图 4a 中,可以观察到垂直于栅极/沟道界面的清晰电位梯度。因此,鳍形通道中产生巨大的电位差,这将调节鳍形通道两侧的电子和空穴的浓度。同时,在鳍状通道中可以形成陡峭的能带弯曲。结果,可以形成平行于栅极/沟道界面的线隧道结。图 4b 显示了鳍结构通道中的电子隧道速率。 e-隧道速率的峰值均匀分布在栅极/沟道界面附近并平行于表面。这证明线隧道结平行于栅极/沟道界面。图 4c 显示了 DF-TFET 中的电流路径。来自背栅/沟道侧的价带电子正隧穿到栅/沟道侧附近的导带。在栅极电压和漏极电压的影响下,电子沿着鳍式沟道移动到漏极。这样,在DF-TFET中形成了隧道电流路径。图 4d 显示了 DF-TFET 中的复合率分布;这可以更清楚地说明隧道结的位置。 SiGe fin通道中的紫色条带可以代表隧道结的位置。

<图片>

a的分布 潜力,b e 隧道速率,c 电流密度和 d DF-TFET的复合率

具有不同参数和模拟/射频性能的直流特性

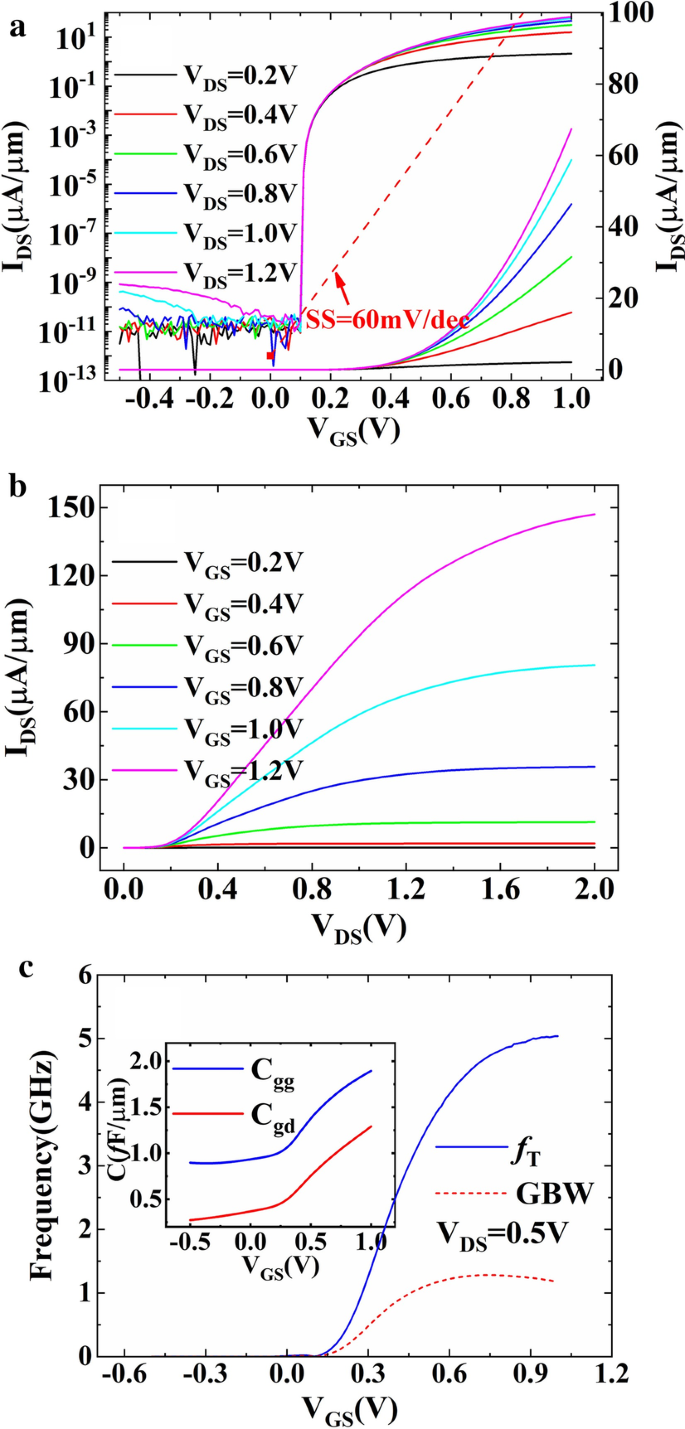

图 5a、b 显示了不同偏压下 DF-TFET 的输入和输出特性。 V 的增加 DS对亚阈值摆动特性影响不大,但I ON 将线性增长而 V DS 从 0.2 V 增加到 1.2 V(在 V GS =1.0 V)。图 5c 显示了截止频率 (f T) 和增益带宽积 (GBW) 计算公式。 (2)和(3)。结果表明,可以获得5.04 GHz的截止频率和1.29 GHz的增益带宽积。

$$f_{{\text{T}}} =\frac{{g_{{\text{m}}} }}{{2\pi C_{{{\text{gs}}}} \sqrt {1 + 2C_{{{\text{gd}}}} /C_{{{\text{gs}}}} } }} \approx \frac{{g_{{\text{m}}} }}{{2 \pi \left( {C_{{{\text{gs}}}} + C_{{{\text{gd}}}} } \right)}} =\frac{{g_{{\text{m} }} }}{{2\pi C_{{{\text{gg}}}} }}$$ (2) $${\text{GBW}} =g_{{\text{m}}} /2 \pi 10C_{{{\text{gd}}}}$$ (3)

一 输入,b 输出和 c DF-TFET的射频特性

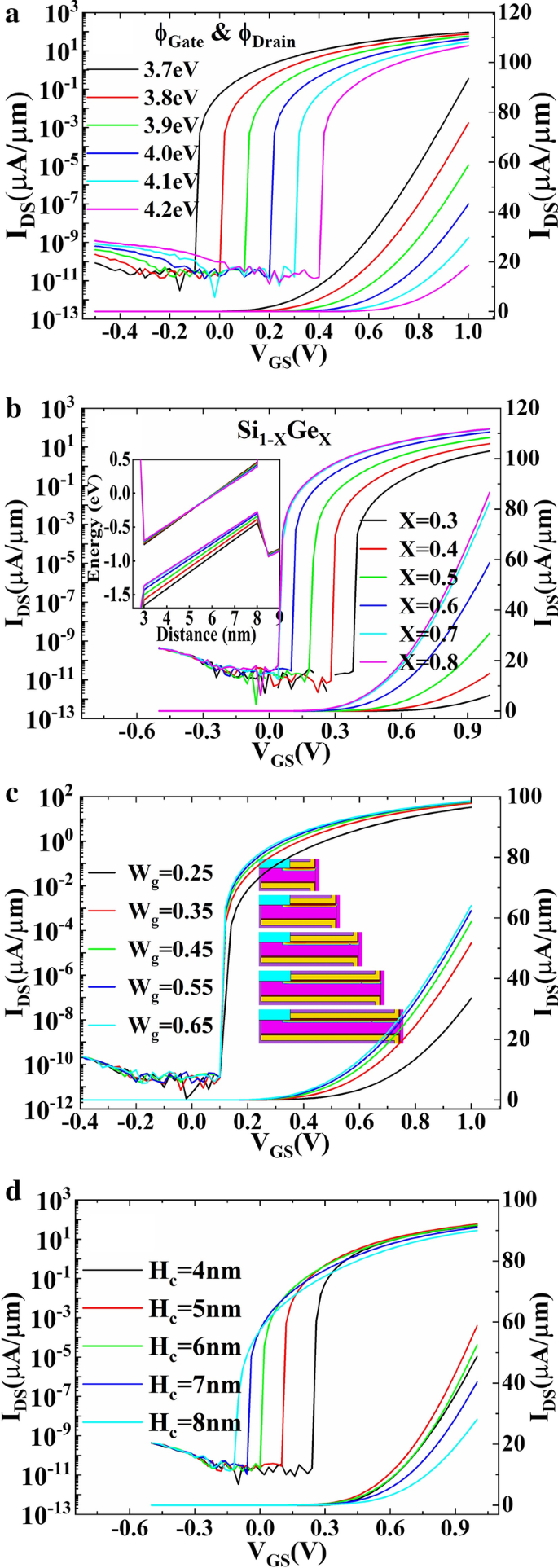

图 6a 显示了栅极功函数 (φ 栅极)和漏极功函数(φ Drain) 对 DF-TFET 传输特性的影响。随着功函数的增加,传递特性曲线向正方向移动。由于功函数从 3.7 到 4.2 eV,V th 从 0 线性增加到 0.5 V,而 I ON 从 93.4 线性下降到 18.6 μA/μm。这使得可以调整 V th 适用于不同的应用要求。图 6b 显示了组成比 X 的影响 Si1−X GeX .锗成分的增加导致能带隙的减小和隧穿窗口的增加,如图 6b 的插图所示。最后,结果在 I ON 增加和传递特性曲线向负方向平移。然而,当 X> 0.7,传递特性曲线和I ON随着X的增加变化不大 .这是因为通道能带结构对 X 变得不敏感 当 X> 0.7,如图 6b 插图所示。图 6c、d 显示了栅极长度 (W g) 和通道厚度 (H c) 关于传递特性。图 6c 的插图显示了不同 W 下设备通道的尺寸 G。从图 6d 不难看出 DF-TFET 将遭受 I 当H时ON减小 c 变得过小和过大。因此,适当的 H c 将有利于设备性能。

<图片>

具有不同a的传输特性 门功函数 (φ 栅极)和漏极功函数(φ 排水),b SiGe 组成比,c 门长 (W g) 和 d 通道厚度 (H c)

为了了解 DF-TFET 在超低功耗应用中的潜力,表 2 显示了不同 TFET 与 DF-TFET 的性能比较。与具有传统重掺杂 p-n 隧道结 [6, 20, 32,33,34,35] 的 TFET 相比,DF-TFET 在 SS 和开关比方面具有明显优势。这是由于使用静电掺杂的 DF-TFET 的特性。与其他无掺杂 TFET [22, 23, 36, 37] 相比,DF-TFET 在 ION 上具有明显优势。这是因为通过使用线隧道结和 SiGe 材料提高了隧道速率。通过结合p-n隧道结和无掺杂隧道结的优点,DF-TFET可以在超低功耗应用中提供高工作电流和低静态功耗。

结论

在这项工作中,提出了一种新型 DF-TFET,并通过仿真方法分析了其电气特性。讨论和研究了DF-TFET的结构特点、物理机制、不同参数下的性能和模拟/射频性能。受益于无掺杂鳍状结构沟道、堆叠栅介质、SiGe沟道材料和高效线隧道结,可以获得良好的开关特性和模拟/射频特性。此外,通过避免在制造过程中形成突然的 p-n 结,可以实现具有高一致性和对工艺波动的高鲁棒性的均匀掺杂。仿真结果表明,I ON 58.8 μA/μm,开关比12个数量级,无明显双极效应,SSmin 2.8 mV/dec和f DF-TFET 可以实现 5.04 GHz 的 T。其工作电流大、开关比高、SS陡峭、可靠性好、制作工艺稳定、可制造性好,有望成为未来低功耗IC和敏感传感器应用的有希望的候选者之一。

数据和材料的可用性

不适用(本文纯理论研究TFET的模拟/射频性能,仿真数据已在本文中给出,此处不再赘述)。

缩写

- DF-TFET:

-

无掺杂鳍状SiGe沟道TFET

- IC:

-

集成电路

- TGTFET:

-

T形栅双源TFET

- DL-TFET:

-

无掺杂 TFET

- I 开 :

-

通态电流

- I 关闭:

-

断态电流

- SSmin:

-

最小亚阈值摆动

- SSavg:

-

平均亚阈值摆动

- C 格:

-

栅极电容

- C gd:

-

栅漏电容

- f :

-

截止频率

- GBW:

-

增益带宽积

- λ :

-

有效筛分长度

- m * :

-

有效载体质量

- E 克:

-

能带隙

- ΔΦ :

-

有效屏蔽能量窗

- W 克:

-

浇口长度

- W 差距:

-

间隙长度

- T 牛:

-

堆叠栅氧化层厚度

- H :

-

通道厚度

- φ 门/φ 排水:

-

栅漏功函数

- V DS :

-

漏源电压

- V 高:

-

栅源电压

纳米材料

- 新颖的方法提高了 PUF 的稳定性

- 通过自动焊接提高性能

- 博客:具有出色性能的医疗可穿戴设备

- 具有增强光催化性能的新型 Bi4Ti3O12/Ag3PO4 异质结光催化剂

- 增强新型阳极 PdAu/VGCNF 催化剂在甘油燃料电池中的电氧化性能

- 氮化处理的基于 HfO2 的 RRAM 中的传导机制和改进的耐久性

- 制备分层 ZnO@NiO 核壳异质结构以提高光催化性能

- 带有 V 形槽腔的通道等离子体纳米线激光器

- 蚀刻变化对 Ge/Si 沟道形成和器件性能的影响

- 具有改良表面结构的高性能有机-纳米结构硅混合太阳能电池

- 关于具有 2DEG 通道和新型 GaN 纳米柱垂直场效应晶体管 (FET) 的 Baliga 品质因数 (BFOM) 增强带图案的基材

- 4.6 版改进 Protocase Designer 的 6 种方法