卡诺图、真值表和布尔表达式

谁开发了卡诺图?

电信工程师莫里斯·卡诺 (Maurice Karnaugh) 于 1953 年在贝尔实验室设计基于数字逻辑的电话交换电路时开发了卡诺图。

卡诺图的使用

现在我们已经借助维恩图开发了卡诺图,让我们使用它。卡诺图减少 与布尔代数相比,逻辑函数更快速、更容易。减少是指简化,减少门和输入的数量。

我们喜欢将逻辑简化为最低成本 通过消除组件来节省成本的形式。我们将最低成本定义为每个门的输入数量最少的门的数量最少。

如果有选择,大多数学生一旦学习了这个工具,就会使用卡诺图而不是布尔代数进行逻辑简化。

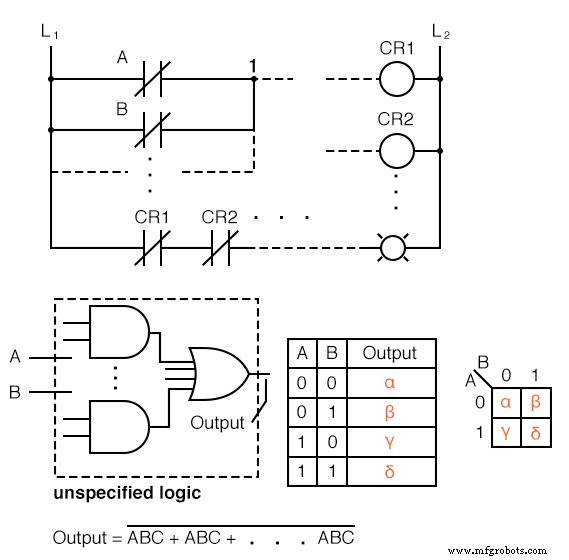

我们在上面展示了五个单独的项目,它们只是表示同一事物的不同方式:任意 2 输入数字逻辑函数。首先是中继梯逻辑,然后是逻辑门、真值表、卡诺图和布尔方程。

关键是这些中的任何一个都是等价的。两个输入 A 和 B 可以采用 0 中的任一值 或 1 ,高或低,开盘或收盘,真或假,视情况而定。有 2 2 =4 种输入组合产生输出。这适用于所有五个示例。

这四个输出可以在继电器梯形逻辑中的灯上,在门图上的逻辑探头上观察到。这些输出可以记录在真值表或卡诺图中。将卡诺图视为重新排列的真值表。

布尔方程的输出可以由布尔代数定律计算,并转移到真值表或卡诺图。

我们应该使用五种等效逻辑描述中的哪一种?对完成任务最有用的那个。

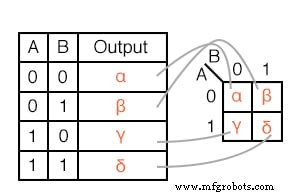

真值表的输出与卡诺图条目一一对应。从真值表的顶部开始,A=0, B=0 输入产生输出α。

请注意,在卡诺图中的 A=0、B=0 单元地址、K-map 的左上角 A=0 行和 B=0 列相交处找到了相同的输出 α。另一个真值表输出β, χ, δ 来自输入AB=01, 10, 11 在相应的K-map 位置找到。

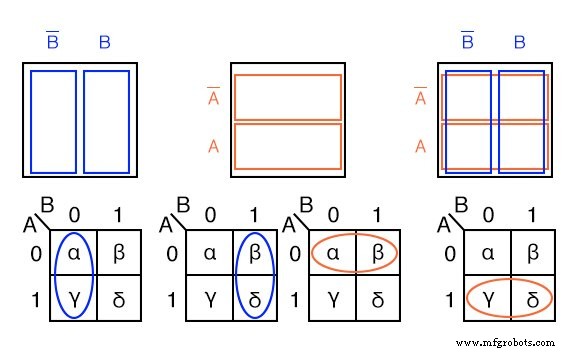

下面,我们借助之前的矩形维恩图(如布尔区域)显示 2 变量 K-map 中相邻的 2 单元格区域。

单元格 α 和 χ 在 K-map 中作为椭圆在下面最左侧的 K-map 中相邻。参考前面的真值表,情况并非如此。它们之间还有另一个真值表条目 (β)。这就把我们带到了将 K-map 组织成一个正方形数组的整个点,具有任何共同布尔变量的单元格需要彼此靠近,以便呈现出一种跳出我们的模式。

对于单元格 α 和 χ,它们具有布尔变量 B' 共同点。我们知道这一点是因为 B=0 (同 B’ ) 对于单元格 α 和 χ 上方的列。将此与 K-map 上方的方形维恩图进行比较。

类似的推理表明 β 和 δ 具有布尔 B (B=1) 共同点。那么,α和β有布尔A’ (A=0) 共同点。最后,χ和δ有布尔A (A=1) 共同点。将最后两张地图与中间的方形维恩图进行比较。

总而言之,我们正在寻找单元格之间布尔变量的共性。卡诺图被组织起来,以便我们可以看到这种共性。让我们尝试一些例子。

示例

示例:

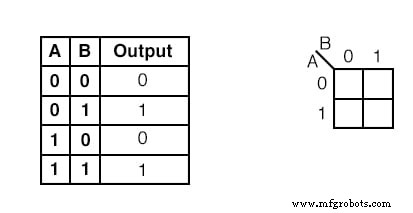

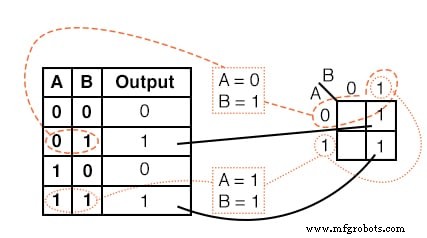

将真值表的内容转移到上面的卡诺图上。

解决方案:

真值表包含两个 1 s。 K-map 必须同时具有它们。找到第一个 1 在上面真值表的第 2 行。

- 注意真值表AB地址

- 在 K-map 中找到具有相同地址的单元格

- 放置一个 1 在那个单元格中

对 1 重复此过程 在真值表的最后一行。

示例:

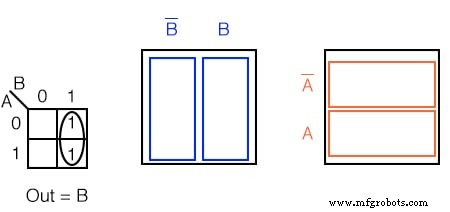

对于上述问题中的卡诺图,写出布尔表达式。解决方案如下。

解决方案:

寻找相邻的单元格,即单元格的上方或侧面。对角线单元格不相邻。相邻的单元格会有一个或多个共同的布尔变量。

- 将两个 1 分组(圈出) s 在列中

- 找到与组相同的变量 top 和/或 side,将其写为布尔结果。它是B 在我们的例子中。

- 忽略与单元格组不同的变量。在我们的例子中,A 是不同的,既是 1 又是 0,忽略布尔值 A。

- 忽略与包含 1 的单元格无关的任何变量。 B' 在它下面没有。忽略 B’

- 结果 输出 =B

通过与右侧的维恩图(特别是 B)进行比较,这可能更容易看出 列。

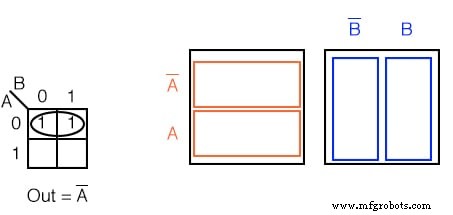

示例:

写出下面卡诺图的布尔表达式。

解决方案: (上)

- 将两个 1 分组(圈出) 在行中

- 找出组中相同的变量,Out =A'

示例:

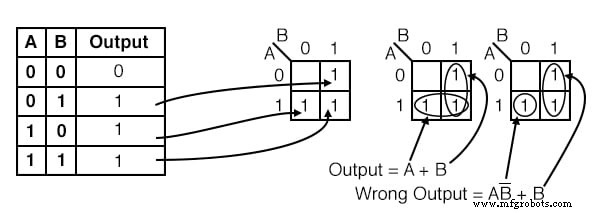

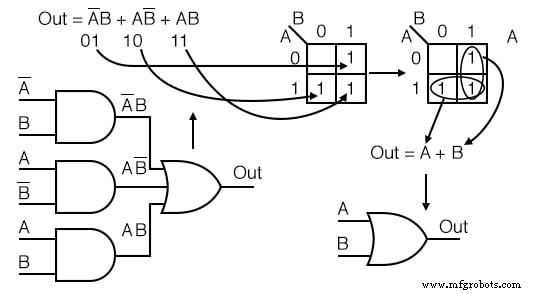

对于下面的真值表,将输出传输到卡诺,然后写出结果的布尔表达式。

解决方案:

转移1 s从Truth表中的位置到K-map中的对应位置。

- 将 B=1 下列中的两个 1 分组(圈出)

- 将 A=1 右侧的两个 1 分组(圈出)

- 为第一组编写产品术语 =B

- 为第二组编写产品术语 =A

- 写出以上两项的积和输出 =A+B

中间的K-map的解决方案是最简单或成本最低的解决方案。一个不太理想的解决方案在最右边。将两个 1 分组后 s,我们犯了形成一组 1-cell 的错误。这是不可取的原因是:

- 单个单元格的乘积项为 AB'

- 对应的解是Output =AB’ + B

- 这不是最简单的解决方案

拿起这个单曲1的方式 是与 1 组成一组 在它的右侧,如中间 K-map 的下一行所示,即使这个 1 已包含在列组中 (B )。我们可以重复使用单元格以形成更大的组。事实上,这是可取的,因为它会导致更简单的结果。

需要指出的是,上述任何一种解决方案,输出或错误输出,在逻辑上都是正确的。两个电路产生相同的输出。前者的电路是成本最低的解决方案。

示例:

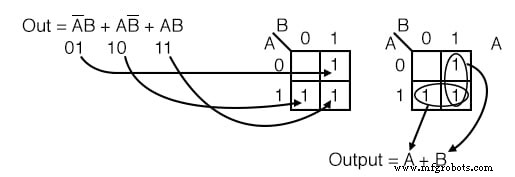

将下面的布尔表达式填入卡诺图,然后写出结果的布尔表达式。

解决方案: (上)

布尔表达式具有三个乘积项。会有一个1 为每个产品术语输入。虽然,一般来说,1 的数量 与 K-map 的大小相比,每个乘积项的 s 随乘积项中变量的数量而变化。

乘积项是 1 所在单元格的地址 被输入。第一个产品术语,A'B , 对应于 01 地图中的单元格。一个 1 在这个单元格中输入。其他两个P项共输入三个1

接下来,继续像前面的真值表问题一样对简化结果进行分组和提取。

示例:

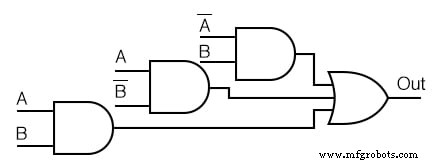

简化下面的逻辑图。

解决方案: (下图)

- 为原始逻辑图编写布尔表达式,如下所示

- 将乘积项转移到卡诺图

- 按照前面的示例形成单元格组

- 按照前面的示例为组编写布尔表达式

- 绘制简化的逻辑图

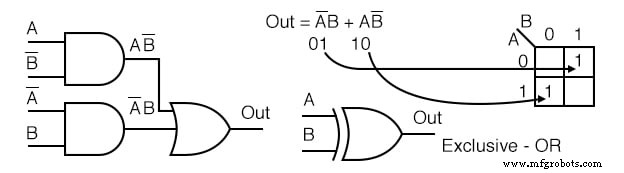

示例: 简化下面的逻辑图。

解决方案:

- 为上面显示的原始逻辑图编写布尔表达式

- 将乘积项转移到卡诺图。

- 无法组成群组。

- 无法简化;保持原样。

上图无法进行逻辑简化。这有时会发生。卡诺图和布尔代数的方法都不能进一步简化这个逻辑。

我们在上面显示了异或原理图符号;然而,这不是逻辑上的简化。它只是让示意图看起来更好。

由于异或逻辑无法简化且应用广泛,因此由制造商作为基本集成电路(7486)提供。

相关工作表:

- 卡诺图工作表

- 布尔代数工作表

- 基本逻辑门工作表

工业技术