具有 2.4Ghz 时钟速率的 100Mhz 带宽 80dB 动态范围连续时间 Delta-Sigma 调制器

摘要

Δ的带宽 Σ 由于过采样率要求,调制器受到时钟速率的限制。随着纳米级CMOS工艺的快速发展,设计宽带宽和高动态范围连续时间Δ成为可能 Σ 用于高频应用的调制器。本文提出了一个三阶4位连续时间Δ Σ 具有单回路前馈拓扑的调制器。该调制器采用 40-nm CMOS 工艺设计,可在 2.4 GHz 时钟速率下实现 80-dB 动态范围和 100-MHz 带宽。调制器从 1.2 V 电源消耗 69.7 mW。

介绍

在蜂窝标准等无线通信应用不断增长的需求的推动下,模数转换器 (ADC) 迅速发展以支持更高的信号带宽 (BW) 和动态范围 (DR)。长期演进高级 (LTE-A) 通信标准中对带宽的要求已上升到 100 MHz。奈奎斯特 ADC,通常是流水线 ADC [1, 2],因其高带宽已被用于宏基站。然而,用于驱动热噪声受限的开关输入电容器和抗混叠滤波器必不可少的输入缓冲器会导致显着的功耗和设计复杂性。此外,流水线 ADC 依赖于精确的级间增益,这决定了高增益宽带残余放大器和校准技术,这一事实导致了复杂性和功耗。 Δ Σ ADC 以其采用过采样和噪声整形技术的高性能和高能效而著称。然而,过采样率 (OSR) 的要求(通常超过 16 [3-6])决定了超过 GHz 的采样频率。最近,Δ Σ 已经通过使用纳米级 CMOS 工艺提出了超过 50 MHz BW 的 ADC,这允许多 GHz 时钟速率。以前,高频Δ Σ ADC 通常采用连续时间 (CT) 实现 [3-9] 而不是离散时间 (DT) 实现。后者由开关电容电路实现,其精度依赖于电容匹配,这意味着在工艺变化下提供稳健的操作。此外,由于电容器和开关的时间常数足够小,因此具有出色的时钟抖动抗扰性。然而,由于采样操作在调制器之前执行,因此需要抗混叠滤波器。另一方面,由于稳定要求以确保级中的稳定性,DT 调制器中的运算放大器采用比 CT 调制器更宽的单位增益带宽 (UGBW)。总而言之,DT 调制器可以提供高精度但信号较窄的信号 [10, 11],并广泛用于实现智能传感器和生物医学成像等计量应用。相比之下,相比具有可比复杂性和功耗的 DT 调制器,设计用于高频应用的 CT 调制器的努力更为广泛。

由于工艺受限的时钟速率,给定工艺中更高 BW 的苛刻设计目标决定了更低的 OSR。为了获得足够的 DR,需要通过高噪声传递函数阶数实现积极的噪声整形,这通常由环路滤波器级联执行,并且在以前的工作中通常等于或大于 3。然而,增加的环路滤波器阶数会导致功耗、不稳定性和设计复杂性。多级噪声整形 (MASH) 架构 [6, 8],由级联低阶局部 Δ 实现 Σ 彼此之间没有反馈路径的调制器被用来缓解稳定性问题,但具有失配敏感性。此外,具有多位量化器的调制器在比较器数量呈指数增加的情况下获得了有条件的高 DR。

本文描述了 40 nm CMOS 中的 CT 调制器,它使用 40 nm CMOS 工艺在 100 MHz 带宽上实现了 80 DR,功耗为 69.7 mW。本文组织如下。 “方法”部分描述了调制器拓扑和电路实现。 “结果和讨论”部分显示了模拟结果,“结论”部分提供了这项工作的总结。

方法

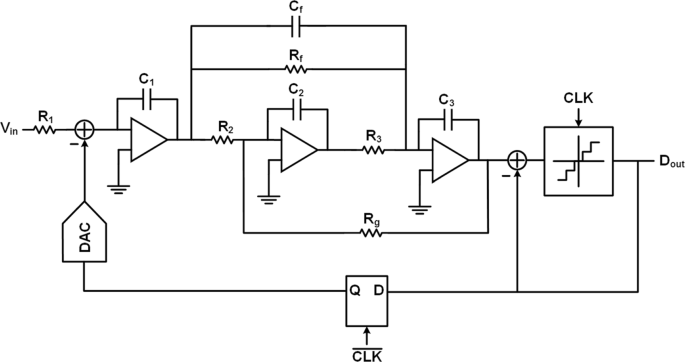

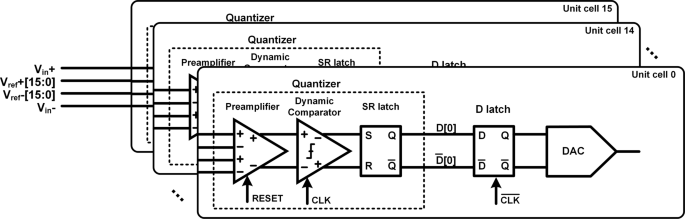

图 1 说明了所提出的三阶 CT Δ 的总体示意图 Σ 调制器采用单端结构以简化。三阶噪声整形在 DR 和环路稳定性之间取得了很好的折衷。建议的调制器的采样率为 2.4 GHz,OSR 为 12。 Δ 中相对较高的 OSR Σ 超过 100 MHz BW 的调制器可确保高 DR。调制器包含三个 RC 积分器、一个 4 位量化器和一个 4 位电流控制 DAC。积分器由创新的低功耗前馈放大器实现,以实现高能效。反馈 DAC 具有半采样周期持续时间的额外延迟,以放宽量化器的亚稳态要求。由无源加法器实现并由量化器直接驱动的快速反馈路径实现了超额环路延迟 (ELD) 补偿。前馈拓扑以牺牲带外信号传递函数为代价来提高功率效率。

提出的单环三阶 4 位 CT Δ 的总体示意图 Σ 前馈拓扑调制器

放大器设计

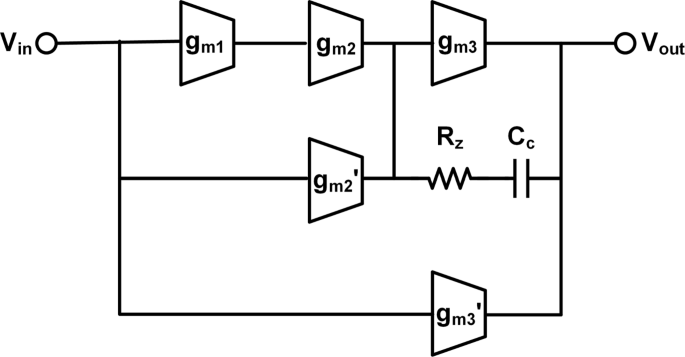

Δ 需要高放大器增益 Σ 调制器以确保所需的噪声变换功能。然而,用于实现多 GHz 时钟速率的纳米级技术的固有增益较低。因此,采用三级放大器来实现足够的直流增益,如图 2 所示。前馈拓扑和米勒补偿相结合,可以在不降低单位增益带宽的情况下提高相位裕度。前馈放大器一直是一种流行的解决方案,可实现具有足够 UGBW 和相位裕度 (PM) 的高增益。由前馈路径引起的左半平面零点应该可以有效地抵消极点的负相移。它需要前馈路径上放大器的高跨导并消耗大量功率。重复使用偏置电流的优势方案节省了功率,同时限制了 g 米 值。 g 不足 米 通常会导致零超出 UGBW 并且无法提供足够的相位裕度。通过增加一个米勒补偿电容和一个归零电阻来提供一个位于整体 UGBW 下方的优化零点。

所提出的具有米勒补偿的三级前馈放大器的拓扑结构

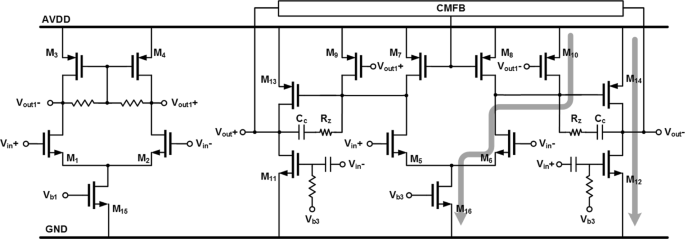

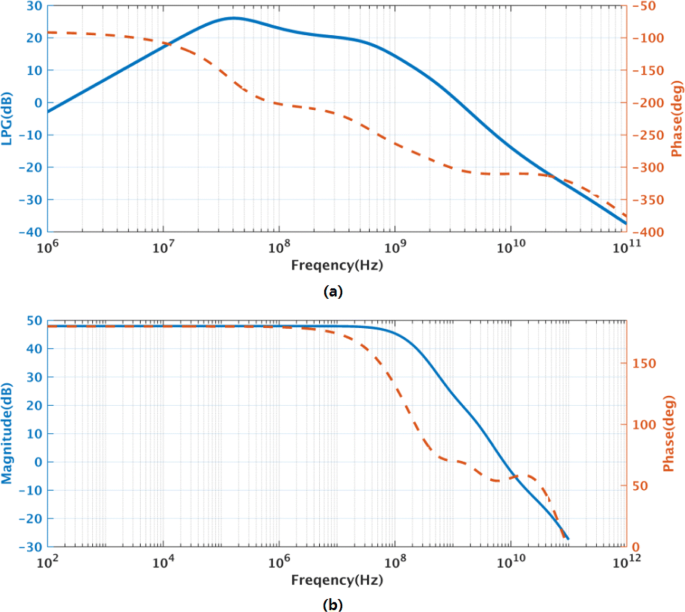

图 3 显示了第一个积分器中使用的放大器的晶体管级原理图。晶体管M 1−4 构成放大器的输入级,而晶体管M 9,10 和 M 13,14 分别形成第二和第三阶段。晶体管M 5−8 和 M 11,12 在输入和输出之间创建两个高速前馈路径,同时与第二级和第三级放大器共享偏置电流。第一级输出共模 (CM) 是本地固定的。第二级和第三级输出 CM 由跨 CMFB 放大器的第二级反馈路径固定,M 7,8 和 M 13,14。图 4a 显示了第一个积分器的放大器在所有负载下的模拟布局后开环响应,而图 4b 显示了闭环响应。第一个积分器实现了 3.6 GHz 的 UGBW 和 57.8 ∘ PM 的所有负载效应,同时从 1.2-V 电源消耗 10.5 mW。第二个和第三个积分器采用相同的拓扑结构,但偏置电流按比例缩放,实现了 4.7 和 3.3 GHz 的 UGBW 和 58.0 和 57.8 的 PM ∘ 分别消耗 4.3 和 17.3 mW。

放大器晶体管级原理图

第一个积分器中放大器的布局后仿真结果。 一 开环交流响应; b 闭环交流响应

量化器和 DAC

如图 5 所示的量化器和 DAC 的示意图,每个由 16 个单元组成。量化器实现为 4 位闪存 ADC,具有 16 级编码器,由 17 抽头电阻梯级生成。 ELD要求量化器的工作时间小于半个采样周期以保证环路稳定性,是限制最大带宽的关键块。

量化器和DAC的简化原理图

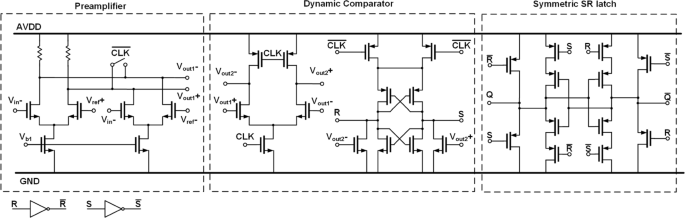

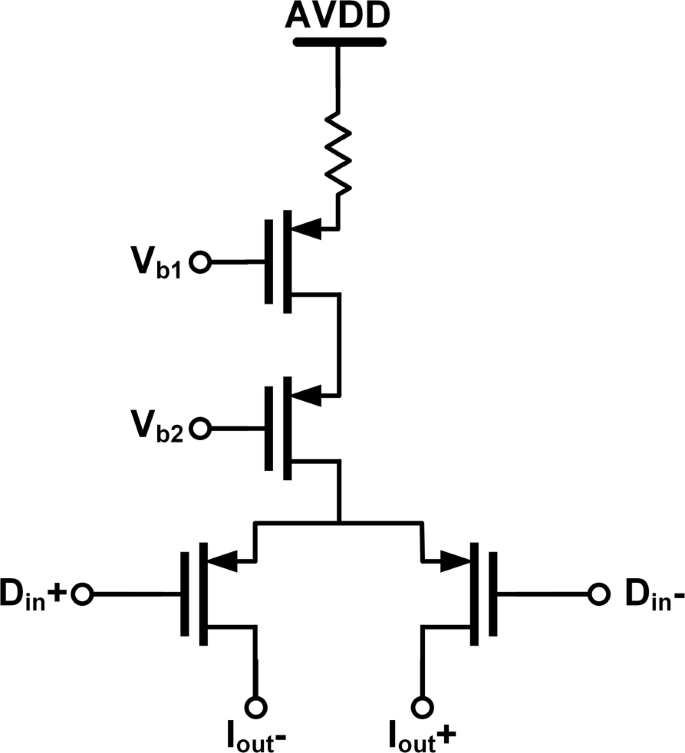

为了实现高速闪存 ADC,采用了三级比较器架构,该架构由前置放大器级、动态比较器级和对称设置和复位 (SR) 锁存器 [12] 组成,如图 6 所示。用于减少输入参考偏移的前置放大器是两个电阻负载差分对,带有一个连接在输出之间的复位开关,以实现快速恢复。与传统的动态比较器不同,差分对和交叉耦合反相器分为两部分,以最大限度地减少每个低压电源电流路径中的晶体管数量。当时钟变为高电平时,动态比较器开始做出依赖于输入的比较决定。然后,随着时钟返回从高到低,每个动态比较器的两个输出都重置为 0,从而触发对称 SR 锁存器的再生和锁存。由于每个支路只有一个晶体管处于活动状态,对称的SR锁存结构具有很强的负载驱动能力。它允许具有显着关断速度和低功耗的小晶体管尺寸。此外,它导致两个输出信号的延迟相等。 DAC 单元之前的 D 锁存器对于时钟信号的电平是低电平敏感的,从而确保一半的 ELD 持续时间。电流控制DAC单元的晶体管级电路如图7所示。

提出的量化器的一个单元元件的晶体管级电路

PMOS电流控制DAC单元元件

结果与讨论

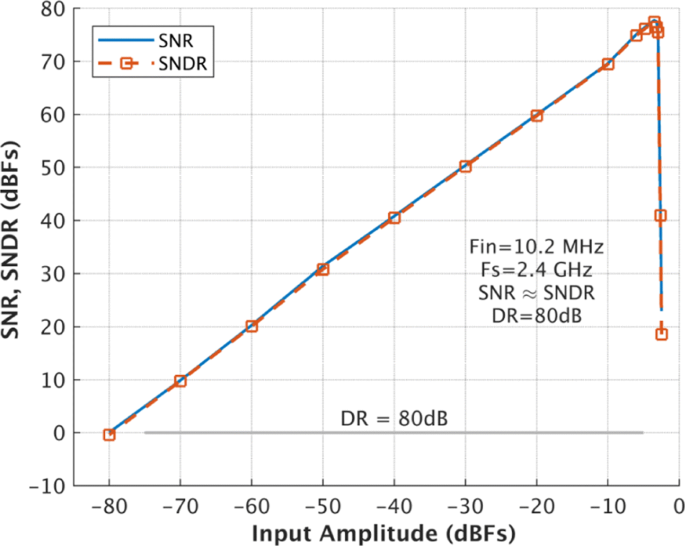

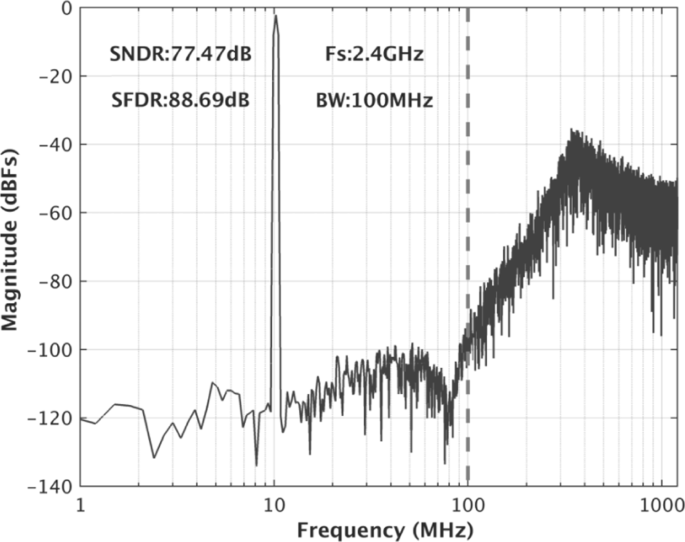

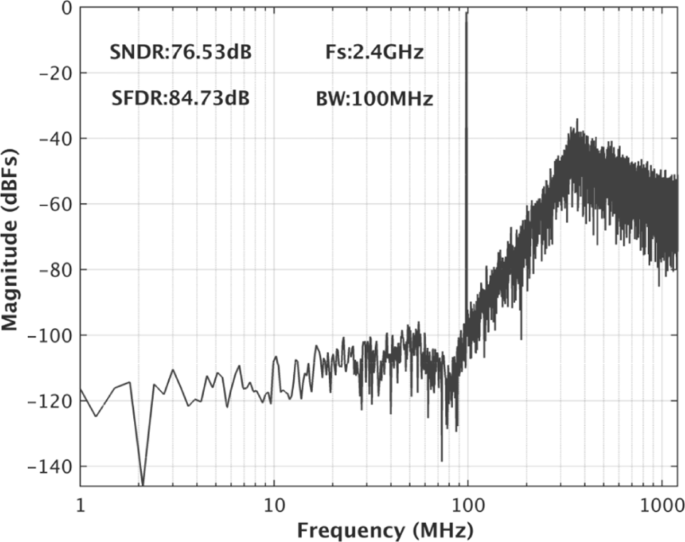

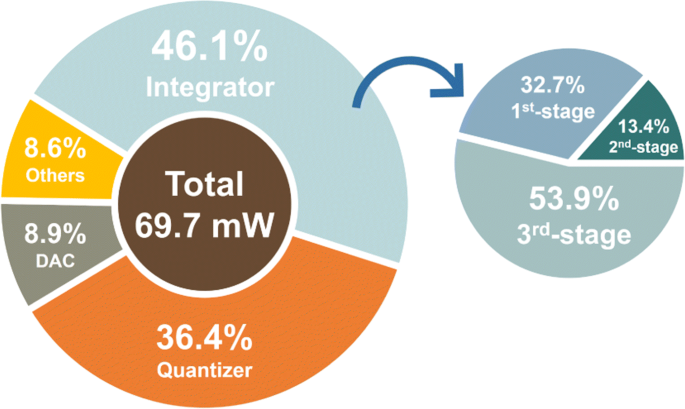

原型Δ Σ 调制器采用 40 纳米 CMOS 工艺制造。如图 8 所示,SNR 和 SDNR 与输入幅度在 10.2 MHz 下的后仿真结果如图 8 所示,实现了 80-dB DR。图 9 和图 10 分别显示了在 10.2 MHz 和 97 MHz 处使用 − 3.52-dBF 单音输入的模拟频谱,因为 0 dBF 对应于 2.4 Vpp 调制器满量程。 SNDR 分别为 77.47 dB 和 76.53 dB。如图 11 所示的击穿功耗,调制器的功耗为 69.7 mW。积分器、量化器和 DAC 分别消耗 32.1 mW、25.4 mW 和 6.2 mW。其他电流消耗 6.0 mW 功率,包括时钟缓冲器、电流偏置和电压参考。调制器基于 DR 实现了 171.6 dB 的 Schreier FOM。表 1 将这项工作与之前发表的几项工作进行了比较。所提出的调制器以最高的 FOM 实现了宽带宽。

10.2MHz 输入时的后仿真 SNR 和 SNDR 与输入信号幅度的关系

10.2 MHz 单音输入后模拟频谱

97 MHz 单音输入后模拟频谱

后仿真功耗细分

<图>结论

在这项工作中,我们提出了一个三阶 4 位 CT Δ Σ 具有单回路前馈拓扑的调制器。该调制器采用 40-nm CMOS 工艺设计,在 2.4 GHz 时钟速率下在 100-MHz 带宽上实现 80 dB DR。低功耗放大器结构具有高能效,调制器在 1.2 V 电源下的功耗为 69.7 mw,Schreier FOM 为 171.6 dB。

数据和材料的可用性

本研究期间生成或分析的所有数据均包含在这篇已发表的文章中。

缩写

- ADC:

-

模数转换器

- BW:

-

带宽

- CT:

-

连续时间

- DR:

-

动态范围

- DT:

-

离散时间

- ELD:

-

超循环延迟

- LTE-A:

-

长期进化高级

- OSR:

-

过采样率

- 下午:

-

相位裕度

- UGBW:

-

单位增益带宽

纳米材料

- DIY 最简单的 IV9 Numitron 时钟与 Arduino

- 使用 AION500MK3 进行高速 3D 打印

- 通过介电超表面扩大带宽完成太赫兹偏振控制

- 使用基于 AFM 尖端的动态犁式光刻在聚合物薄膜上制造具有高通量的纳米级凹坑

- RGO 和三维石墨烯网络共同修饰的高性能 TIM

- 具有超弹性和高电容的石墨烯/聚苯胺气凝胶作为高抗压超级电容器电极

- 基于混合全介电-石墨烯超表面的可控双折射偏振转换器

- 具有改良表面结构的高性能有机-纳米结构硅混合太阳能电池

- 具有高电导率的拓扑绝缘体纳米片中极其增强的光电流响应

- 在太赫兹范围内具有可切换吸收和偏振转换功能的多功能设备

- 具有高 PSRR 的纳米级低功耗无电阻电压基准

- 具有高开/关比和极性可切换光电导性的 SnSe2 场效应晶体管