如何分析和禁止高速PCB电源的阻抗

随着PCB设计复杂度的不断升级,稳定可靠的电源成为高速PCB设计研究的新趋势。尤其是在开关元件数量不断增加、Vcore不断降低的情况下,功率的波动往往会给系统带来致命的影响。因此,保持电源系统的稳定性成为高速PCB设计的重点。

然而,由于电力系统阻抗的存在,负载瞬态电流在电力系统阻抗中产生较大的压降,导致系统不稳定。为保证各部件自始至终正常供电,必须对电力系统中的阻抗进行控制,即尽可能降低阻抗。

去耦电容的应用是抑制电力系统阻抗的有效途径。本文分析了去耦电容在电力系统中阻阻的原因,并列出了去耦电容选择的方法。此外,主要研究如何基于谐波分析确定去耦电容的位置,以最大限度地抑制电力系统的阻抗。

阻抗分析

电源和地可视为一个大板电容,其容量由公式C=kAr/d计算得出

在这个公式中,k 是 0.2249 英寸; A是指两个平面之间的平行面积; r为介质的介电常数,常用的FR4板材料为4.5; d 指电源与地之间的距离。以 2x1 英寸大小的 PCB 为例。由电源和地形成的并联面积为 20Mils 的电容器的电容约为 0.2249x4.5x2x1/0.02=101.2pF。从这个公式可以看出,电力系统的去耦电容很小,对应的阻抗会很大,一般几欧。因此,通过电力系统的自去耦来降低阻抗是远远不够的。

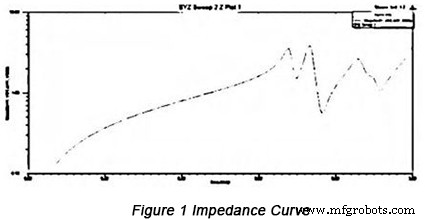

采用2.5D的仿真工具SIWAVE对有源器件进行阻抗仿真。选取电源和地网U41计算XYZ参数,扫描范围为0~1GHz,得到如下图1的阻抗曲线。

从图中可以看出,阻抗曲线随频率的变化而变化,在670MHz、730MHz和870MHz的拐点处阻抗变化很大。

禁止方法

• 去耦电容阻阻的理论分析

由于无法通过与电源本身的去耦来降低阻抗,因此必须使用去耦电容来抑制阻抗。

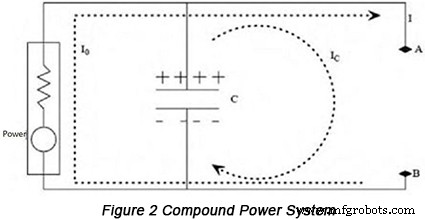

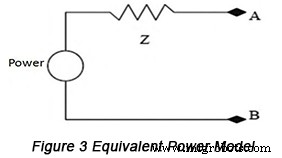

图2是复合电源系统示意图。图 3 以等效功率模型表示该电力系统。

可以应用一个公式来表示该电路:V=ZxL。应该达到这样一种情况,即即使负载瞬态电流在A点和B点之间保持较大的变化,两点之间的电压变化也必须非常小。根据公式,除非阻抗 (Z) 的值足够小,否则永远无法达到此目的。在图 3 中,去耦电容的应用有助于实现这一目标,因此可以从等效的角度表明去耦电容能够降低电力系统的阻抗。此外,从电路原理的角度来看,可以保持相同的结论。电容器在交流信号上具有低阻抗。因此,电容器的参与实际上肯定会降低电力系统中的交流阻抗。

• 去耦电容的电容选择

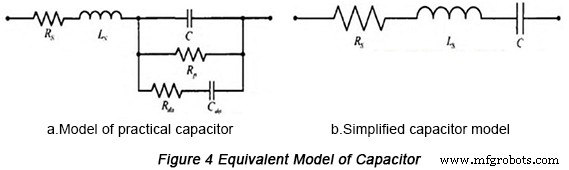

从来没有理想的电容器,它总是保持寄生参数。 ESR(有效串联电感)和ESL(有效串联电阻)对电容器的高频性能影响最大。图4为考虑寄生参数的等效模型。

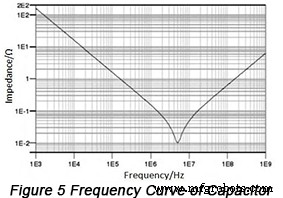

电容器也可以看成是串联谐波电路,其串联谐波频率为:f=1/2PIFC。当它停留在低频环境时,它显示电容。然而,当频率上升时,它不断地显示出它的电感。换句话说,它的阻抗会随着频率的升高先上升后缩小,等效阻抗的最小值出现在串联谐波频率f0处。此时容抗和感抗正好抵消,表现为电容等效电阻最小的阻抗值与ESR值相等。电容频率曲线如图5所示。

因此,在电容器选型过程中,选择的电容器谐波频点落在临近将遭受去耦的频点。尽可能在自谐频率之前充分应用和使用其电容性能。

不同电容的不同电容对应不同的自谐波频率如下表所示。

| 电容 | DIP (MHz) | STM (MHz) |

| 1.0μF | 2.5 | 5 |

| 0.1μF | 8 | 16 |

| 0.01μF | 25 | 50 |

| 1000pF | 80 | 160 |

| 100pF | 250 | 500 |

| 10pF | 800 | 1.6(GHz) |

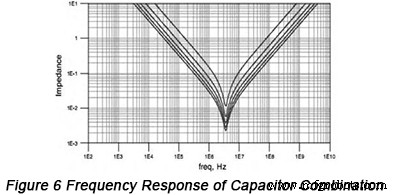

一般要求应用去耦电容的谐波特性,通过电容并联获得最低的输入阻抗。同类型电容器的并联频率响应如下图6所示。

基于这种方法,等效ESR和ESL可以大大降低。对于多个电容相同的电容(n),组合后等效电容C变为nC,等效电感L变为L/n,等效ESR变为R/n。然而,谐波频率保持不变。可以看出,由于不同类型电容器的自谐波频率相同,并联的电容器越多,容感区阻抗越小,自谐波频率点不变。

综上所述,在去耦电容的选择过程中,应将去耦频率作为去耦的自谐波频率点,以便选取相应的电容。此外,多个相同容量的电容并联使用,可以提高去耦能力,降低阻抗。

• 去耦电容位置的确定

选择去耦电容后,必须考虑它们的位置。电源和地平面可以看作是由多个电感和电容组成的网络或一个谐振腔。在一定频率下,电感和电容发生谐振,影响电力系统的阻抗。随着频率的提高,阻抗不断变化,特别是并联谐振持续显着时,阻抗也显着上升。因此,应结合PCB的谐波分析,确定去耦电容的具体位置。

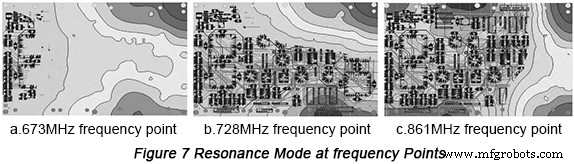

应用SIWAVE仿真工具的谐振分析功能,导出电阻、电容、电感等等效参数。此外,PCB的谐振分析需要得到不同频率点的谐振模式,如图7所示。

结合图1可以看出,阻抗比较大的几个频点与产生谐振的频点是相容的。因此,根据谐振分析的结果,可以得出结论,在谐振严重的区域应放置合适容量的去耦电容,以降低阻抗。

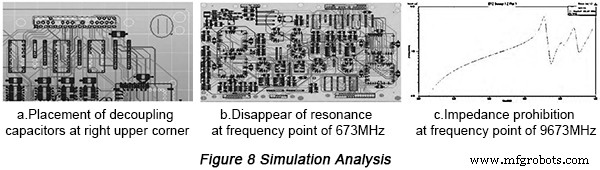

以673MHz频率点为例,可以并联去耦电容,这样会发现谐振丢失,相应的阻抗也被禁止,如图8所示。

基于PCB谐振分析,可以确定谐振发生的对应位置,根据并联放置大小合适的电容来抑制阻抗。

有用的资源

• 影响 PCB 特性阻抗的要素和解决方案

• 高速数字电路 PCB 设计中的阻抗控制

• 刚硬 PCB 的阻抗设计注意事项

• 阻抗PCB 设计中的过孔控制及其对信号完整性的影响

• PCBCart 的全功能 PCB 制造服务 - 多种增值选项

• PCBCart 的高级 PCB 组装服务 - 从 1 件开始

工业技术