高速PCB设计的差分等距处理和仿真验证

相对延迟对信号的影响

在差分信号线上传输的信号包含信号的差模分量和共模分量。

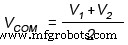

差分信号量是指两个信号之间的差异,公式 Vdiff =V1 - V2。共模信号量是指两个信号之和的一半,公式如下  。因此,单条线路的电压变化肯定会导致差模信号和共模信号同时受到影响。接下来,应用图形软件绘制数学函数图,分别研究对差模信号和共模信号的影响。为方便研究,可以将信号模拟成上、下时间相同的梯形波形进行分析。

。因此,单条线路的电压变化肯定会导致差模信号和共模信号同时受到影响。接下来,应用图形软件绘制数学函数图,分别研究对差模信号和共模信号的影响。为方便研究,可以将信号模拟成上、下时间相同的梯形波形进行分析。

• 对差分信号的影响

差分线对的正相端信号、负相端信号和差分信号如下图1所示,其中实线代表差分信号波。

如果从正相端到负相端进行移相,则在上升沿或下降沿,正相端信号与负相端信号之间的差值会发生变化,并且这种变化会随着相位的变化而变化。 Tr 用于表示上升时间和下降时间中较短的时间。可以看出,当相位放置小于Tr的第二点时,信号失真相对较小,相位放置的增加导致差分波形失真较大。当相位放置超过 Tr 时,波形上会出现非单调区域。这里的非单调区域是一条直线。但对于实际信号,由于反射,在非单调区域可能会出现较大的起伏,形成干扰脉冲,导致误触发,应避免。此外,随着相位的增加,差分波形的上沿变慢,可能导致数据信号建立时间不足,时钟信号保持时间不足。

• 对共模信号的影响

单端信号的相位放置不会对差分波形产生影响,但会改变共模信号的波形。当相位在正端信号处发生时,共模信号将发生波形变化。可以看出,波动幅度与移相量有关。当移相量分别为0.05Tr、0.1Tr、0.2Tr、0.5Tr时,共模波动幅度分别为原波动幅度的5%、10%、20%和50%。当相位增加到 Tr 或更多时,波动将增加到大约 100%,这是最高波动范围。共模信号的变化可能会导致 EMI 问题,由于在很多情况下终端无法接收到共模信号,在接收端会形成反射,导致信号振铃。因此,应尽可能减小共模信号的波动范围。

总之,差分对之间的相对延迟过大可能会导致信号误触发、信号反射、EMI 和时序问题。然而,相对延迟信号的影响程度取决于与信号Tr兼容的比例因子。当比例因子为 0.05 时,差分信号的失真几乎可以忽略不计。但是对于共模信号,当比例因子为0.05时,共模信号的电压波动可以控制在5%左右。那么,即使在全反射的情况下,叠加在信号线上的反射电压也只有原来波动的10%,这通常是可以接受的值。因此,在高速PCB设计过程中,路由规则中差分信号线的相对延迟可以设置为0.05 Tr,能够满足信号完整性的要求。

相对延迟类别的确定

综上所述,差分等距类别的确定,即差分对相对延迟的确定,关键在于确定Tr是指差分信号上下时间中的最小值。上升时间和下降时间的输出实际上是阻抗和电容组合的输出。因此,无负载的上升/下降时间实际上是固有的上升/下降时间。

可以通过以下三种方法获得Tr的值:

•上升/下降时间可以直接从元件手册中获得。但是,在大多数情况下,不提供此参数。

• Tr 的值可以从组件 IBIS(输入/输出缓冲区信息规范)模型的 Ramp 关键字中获得。 Ramp 关键字下的上升/下降时间参数一般在输出端口连接一个 50Ω 的电阻测量,通常为最终电压时间的 20% 到 80%。由于参数是在没有考虑封装影响的情况下得到的,所以我们严格使用上升/下降时间作为Tr的值。

• Tr的值可以根据最小时钟频率或最大时钟频率来估算的输出信号。由于在大多数高速数字系统中,分布式上升沿约为时钟频率的 10%,因此 Tr 的值可以根据公式提供的最小时钟周期 Tclk 估算:Tr =Tclk x 10%。

通过时钟周期获得的估计值通常是严格的,因为封装寄生参数或元件负载会使晶体管固有的上升/下降时间大大减慢。

在实际工作中,大多数情况下,电路设计人员不会将Tr的信息提供给PCB版图工程师,他们只是在差分等距控制方面收到一些模糊的要求。第三种方法无疑为PCB布局工程师提供了一个简单的方案,只要获得信号线上的最高时钟频率即可。最高时钟频率被电路设计人员视为最可靠的设计参数,通常在PCB设计之初就提供给PCB布局工程师。

第三种方法通常会导致差分对之间的相对延迟控制范围内的参考值列表,如下表所示。

| 时钟频率/ns | 时钟频率/MHz | 相对延迟类别/ps | 传输线长度/mil |

| 3.75 | 266 | 18.8 | 105 |

| 3 | 333 | 15 | 84 |

| 2.5 | 400 | 12.5 | 70 |

| 1.87 | 533 | 9.4 | 52 |

| 1.5 | 667 | 7.5 | 42 |

| 1.25 | 800 | 6.3 | 35 |

模拟验证

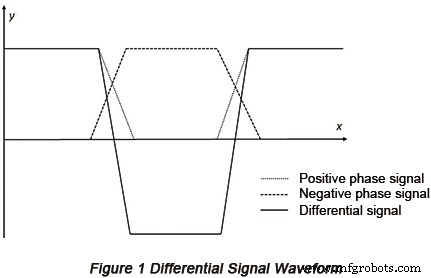

以TSM320和MT41J256M16之间的DQS(Data Strobe)差分信号为例,应用Cadence仿真软件将DOS信号传输到DRR3内存来模拟内存控制芯片,分析其对数据信号建立保持时间的影响,并验证上述分析。仿真电路如下图2所示。

根据图2,输出引脚的参考电压为1.5V;内存控制芯片通过ODT(On-Die Termination)方式直接与内存芯片相连,传输线为800mil;差分阻抗为 100Ω,仿真时钟频率为 800MHz。一条50Ω的传输线与DQS正相端串接,模拟差分对的差异现象。在等距差分情况下,50Ω单端传输线长度为0mil。

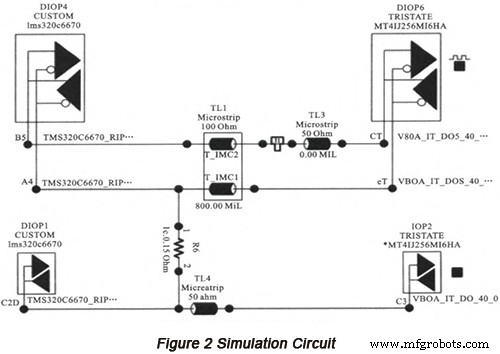

对差分等距电路进行了仿真。图 3 说明了差分信号正相端的输出信号。经测量,上升时间约为216ps,下降时间约为219ps,因此最小上升/下降时间Tr应为216ps。

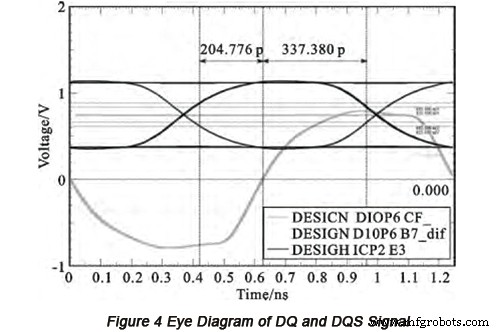

图4是数据信号DQ和门控信号DQS通过仿真得到的眼图,建立时间为205ps,保持时间为337ps。根据模拟的DQS和DQ信号的周转率,根据数据手册,要求接收端建立数据信号的最短时间为85ps,最短保持时间为95ps。因此,最小建立时间的超标为120ps,保持时间为242ps。

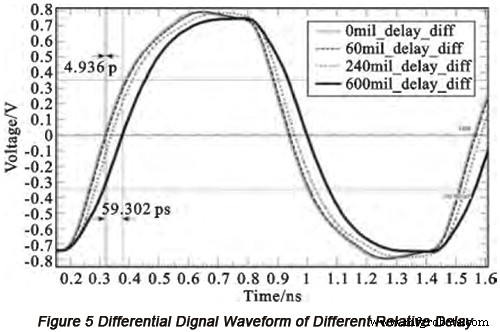

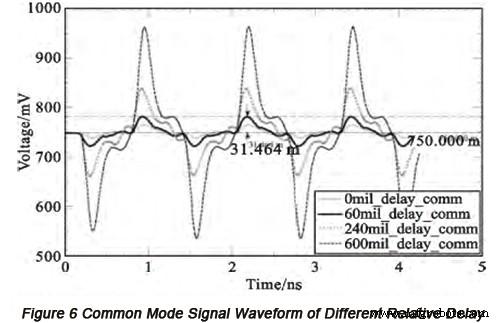

必须考虑正相端存在0.05Tr相位、0.2Tr相位和0.5Tr相位的情况。该电路可以模拟单端传输线长度,分别设置为60mil、240mil和600mil。仿真4次后的差分信号波形和共模信号波形如图5和图6所示。

根据图 5,当发生 0.05Tr 和 0.2Tr 的相对延迟时,失真最小。特别是当相对延迟为0.05Tr时,差分信号到差分信号波形仅放置约5ps,没有相对延迟,使数据信号建立过测量增加约5ps,保持过测量时间减少5ps。虽然保持过测量时间减少了,但对于 242ps 的保持时间,这个放置量是如此之少。可以避免时间排序。对于相对延迟为0.5Tr的情况,DQS信号波形的布局已经达到了60ps左右。虽然这个位置仍然属于过度测量的范畴,但应该引起足够的重视。

由图 6 可知,相位位置的增加导致波的周期性波动明显,范围逐渐增大。当相对延迟分别为0.05Tr、0.2Tr和0.5Tr时,共模信号实测峰值分别为61mV、176mV和430mV,其中最高值是最低值的7倍。最大波动幅度分别为4.3%、12%和29%。

综上所述,仿真结果与数学函数图分析得到的结果相吻合。当差分对之间的相对延迟小于0.05Tr时,对信号的影响很小。

输出端输出信号的最小时钟周期用于估计相对延迟控制类别。根据组件手册,组件的最小时钟周期为 1.25ns,时钟频率为 800MHz。根据表 1,传输线长度为 35mil 时,相对延迟应控制在 6.3ps 以内。显然,通过仿真,这个值远小于相对延迟0.05Tr的控制类。因此,估计的相对延迟控制类别相对保守,比模拟结果更具体。

有用资源

• 嵌入式应用系统中的高速PCB设计研究

• 如何设计高速PCB的图像平面

• 信号完整性的高速PCB设计挑战及其解决方案

• 使用 OrCAD PSpice 模拟 PCB

• PCBCart 的全功能 PCB 制造服务 - 多种增值选项

• PCBCart 的高级 PCB 组装服务 - 从 1 件开始

工业技术