5-nm LiF 作为聚合物太阳能电池中的高效阴极缓冲层,只需引入 C60 中间层

摘要

氟化锂 (LiF) 是体异质结聚合物太阳能电池 (PSC) 中一种高效且广泛使用的阴极缓冲层 (CBL)。由于其绝缘特性,LiF 的厚度通常限制在 1 nm。如此小的厚度在热沉积过程中难以精确控制,更重要的是,1 nm 厚的 LiF 无法为下面的有源层提供足够的保护。在这里,我们通过简单地在有源层和 LiF 层之间插入 C60 层,证明了将非常厚的 LiF 作为 CBL 的应用,而不会牺牲器件效率。具有 C60/LiF (5 nm) 双 CBL 的器件的峰值功率转换效率 (PCE) 为 3.65%,是仅使用 LiF (5 nm) 的器件 (1.79%) 的两倍。基于 C60/LiF (5 nm) 的器件的卓越性能主要归因于 C60/LiF (5 nm) 双层的良好导电性,这是由于 C60/LiF 界面处发生的混合引起的。此外,P3HT/C60子电池的形成和C60的光学间隔效应也有助于短路电流密度的增加(J sc) 的设备。随着 LiF 厚度进一步增加到 8 nm,C60/LiF 基器件的 PCE 达到 1.10%,而仅 LiF 器件的光伏性能可以忽略不计。总而言之,我们的研究结果表明,C60/LiF 双层由于其对 LiF 厚度变化的高耐受性而成为 LiF 单层的有前途的替代品。

背景

近几十年来,溶液加工的本体异质结聚合物太阳能电池 (PSC) 因其潜在的优势而受到越来越多的关注,例如成本低、重量轻以及可以制造大规模、灵活和半透明的设备 [1,2,3] ,4,5]。到目前为止,与硅基太阳能电池相比,相对较低的功率转换效率(PCE)仍然是阻碍其实际应用的主要限制因素。为了实现这一有前途的技术的商业化,广泛的研究工作集中在提高 PSC 的效率上。到目前为止,已经证明了 11-13% 范围内的 PCE,主要是由于新型共轭聚合物供体和非富勒烯受体材料的发展 [6,7,8,9,10,11,12]。此外,在活性层和电极之间引入阳极/阴极缓冲层提供了另一种提高器件性能的有效手段[13,14,15,16,17,18,19,20,21]。

根据氧化铟锡(ITO)电极作为阳极还是阴极,PSCs可以分为常规结构和倒置结构。对于以 ITO 作为阳极的传统 PSC,通常使用低功函数金属(例如 Ca)作为阴极缓冲层(CBL)以降低阴极(例如 Al、Ag)的功函数。然而,Ca暴露在空气中容易被氧化,导致器件稳定性差。 PSC 中另一种广泛使用的 CBL 是氟化锂 (LiF),它已被证明可以通过在阴极界面形成界面偶极子来提高器件性能 [22]。然而,由于其绝缘特性,LiF 的厚度被限制在小于 2 nm(通常~ 1 nm)[23, 24]。如此小的厚度很难通过热沉积来控制。此外,在热金属原子蒸发过程中,1 nm 厚的 LiF 不能为下面的活性层提供足够的保护 [17, 25]。

为了解决这些问题,我们之前曾报道过五叠 C60/LiF CBL,尽管使用了非常厚的 LiF,但由于其良好的导电性,这大大提高了 PSC 的器件效率和稳定性 [26]。然而,五层堆叠的 C60/LiF 薄膜是通过交替沉积 C60 和 LiF 层来制备的。这种制备过程非常复杂且耗时,并且显着增加了器件制造成本。在这项工作中,我们采用 C60/LiF 双层作为 CBL,以实现与五层 C60/LiF CBL 相同的效果。在 LiF 蒸发之前沉积 C60 层后,允许使用厚 LiF 而不会牺牲器件效率。具有 C60/LiF 双 CBL 的 PSC 在很宽的 LiF 厚度范围(1~6 nm)内保持 ~ 3% 的 PCE,并且即使在非常厚的 LiF(8 nm)下也显示出 1.10% 的 PCE。相比之下,具有 LiF 单 CBL 的 PSC 随着 LiF 厚度的增加表现出 PCE 的快速下降,并且在 LiF 厚度为 8 nm 时具有可忽略不计的光伏性能。此外,基于 C60/LiF 的器件的峰值效率 (3.77%) 比仅基于 LiF 的器件的峰值效率 (3.06%) 高 ~ 23%。综上所述,这些结果表明,与单层 LiF 相比,C60/LiF 双层作为 CBL 更有前景。

方法

PSC 的制造

ITO 涂层玻璃基板(Delta Technologies, LTD)在丙酮和异丙醇 (IPA) 中分别超声清洗 5 分钟,然后用 O2 等离子体处理 60 秒以生成亲水表面。将过滤后的聚(3,4-亚乙基二氧噻吩):聚(苯乙烯磺酸盐)(PEDOT:PSS)溶液(HC Starck,Clevios PH 500)以 2000 rpm 的速度旋涂到清洁的玻璃/ITO 基板上 50 秒,然后在 110°C 下在氮气气氛下烘烤 20 分钟。随后,将样品转移到 N2 吹扫的手套箱(<0.1 ppm O2 和 H2O)中,用于旋涂光敏层。

P3HT(Rieke Metals Inc.,4002-EE,91-94% 区域规整度)和 PCBM(美国染料来源,纯度> 99.5%)以 1:1 的重量比溶解在氯苯中。使用 0.45 μm 过滤器过滤混合溶液,然后以 1000 rpm 的速度在 PEDOT:PSS 层顶部旋涂 50 秒,然后在 130°C 下热退火 20 分钟,产生 ~ 160-nm-使用 Dektek 表面轮廓仪测量的厚活性层。在 1×10 − 6 的基础压力下通过热蒸发依次沉积 C60、LiF 和 Al(75 nm)电极 毫巴。沉积速率和薄膜厚度用石英晶体传感器监测。在Al沉积之前,将直径为1 mm的圆形阴影掩模放在样品上以限定活性区域。

特征化

电流密度-电压 (J -V ) 特性是使用 Keithley 2400 系统在模拟空气质量 1.5 全球 (AM 1.5 G) 太阳光照射下以 100 mW/cm 2 的强度测量的 ,由功率计(OPHIR,Nova-Oriel)和参考硅太阳能电池校准。使用手套箱内的 PSC 进行测量。使用在轻敲模式下操作的 Veeco Dimension-Icon AFM 拍摄原子力显微镜 (AFM) 图像。使用 Varian Cary 50 UV/Vis 分光光度计获得吸收光谱。在环境条件下对 PSC 进行了通过线性增加电压 (Photo-CELIV) 测量的光致电荷提取。使用脉冲 N2 激光(337.1 nm,1.4 ns)产生电荷载流子,然后通过在 100 μs 延迟时间后施加的反向偏置电压斜坡提取电荷载流子。使用数字存储示波器(50 Ω 输入阻抗)记录电流瞬变。在照明期间和之后,施加偏移电压以补偿器件的内置电位,从而防止在施加电压斜坡之前的初始光电流。载流子的迁移率可以根据下式[27, 28]计算:

$$ \mu =\frac{2{d}^2}{3{At}_{\mathrm{max}}^2\left[1+0.36\frac{\varDelta j}{j(0)}\右]} $$ (1)其中 μ 是电荷载流子迁移率,d 是活性层的厚度,A 是电压上升速度,t max 为提取电流达到最大值的时间,Δj 是当前的提取峰高,j (0)为电容的位移电流。

结果与讨论

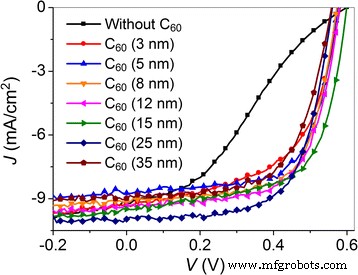

图 1 显示了 J -V 特性,记录在 100 mW/cm 2 照明(AM 1.5 G),夹在有源层和 5 纳米厚的 LiF 层之间的具有和不具有不同厚度的 C60 的 PSC。尽管典型的短路电流密度 (J sc) 和开路电压 (V o)。低 FF 是根据 LiF 的绝缘特性合理化的,当 LiF 层太厚时,它会阻止电子的注入/提取,从而导致大串联电阻 (R s) 和小分流电阻 (R sh) 的设备,如表 1 (R s 和 R sh 由照片 J 的反斜率计算 -V 0 mA/cm 2 时的曲线 和 0 V,分别)。至于J sc,正常值 (9.23 mA/cm 2 ) 意味着器件内部的内置电场(来自阳极和阴极之间的功函数差异)足以通过隧道效应促进电子传输通过 LiF (5 nm) CBL。在 P3HT:PCBM 和 LiF (5 nm) 层之间引入 3 nm 厚的 C60 层后,S 形消失,FF 从 32.4% 显着增加到 56.3%。增加的 FF 源于减少的 R s,这意味着 C60 (3 nm)/LiF (5 nm) 双层比单个 LiF (5 nm) 层具有更好的导电性。随着 C60 厚度的增加,FF 先增加,在 8 nm 处达到最大值 67%,然后随着 C60 厚度的进一步增加而略有下降。由于 FF 的回收,基于 C60/LiF (5 nm) 的器件显示出 3.65% 的最大 PCE,这是仅基于 LiF (5 nm) 的器件 (1.79%) 的两倍。为了证明结果的可重复性,研究设备的平均光伏参数和标准偏差是从一批五个设备中计算出来的,如附加文件 1:表 S1 中所示。对于每个设备,包括J在内的所有参数 sc, V oc、FF 和 PCE 具有高度可重复性,几乎没有变化,这验证了表 1 中所示结果的可靠性。

<图片>

J -V 特性,记录在 100 mW/cm 2 光照(AM 1.5 G),在 P3HT:PCBM 和 5 nm 厚的 LiF 层之间插入有和没有不同厚度的 C60 的 PSCs

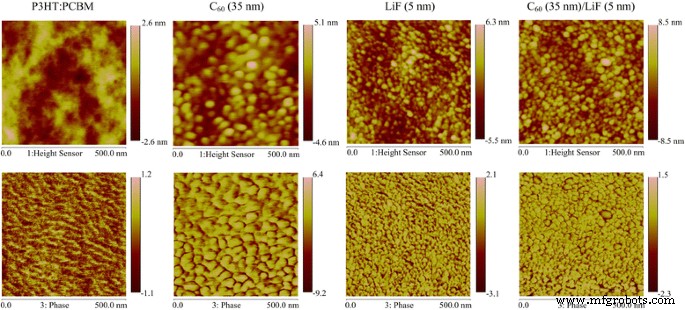

为了找出导致基于 C60/LiF (5 nm) 的 PSC 的高 FF 的原因,进行了 AFM 测量以检查 C60 表面上 LiF 层的形态。图 2 显示了没有和有 C60 (35 nm)、LiF (5 nm) 和 C60 (35 nm)/的 P3HT:PCBM 薄膜的高度(顶部)和相位(底部)图像,通过轻敲模式 AFM 记录LiF (5 nm) 层沉积在顶部(图像尺寸 500 nm × 500 nm)。原始 P3HT:PCBM 薄膜具有非常光滑的表面,均方根 (rms) 粗糙度低至 0.81 nm(高度图像),并显示 P3HT 的纤维状结晶域(相位图像)[29]。在顶部沉积 35 纳米厚的 C60 和 5 纳米厚的 LiF 后,均方根粗糙度分别增加到 1.36 和 1.67 纳米。尽管顶部 C60 和 LiF 层之间的 rms 粗糙度没有显着差异,但这两种薄膜的表面形貌却大不相同。与 5 nm 厚的 LiF 相比,35 nm 厚的 C60 显示出更大的聚集体(球形),这也可以在它们的相位图像中观察到。当在 P3HT:PCBM 薄膜上沉积 C60 (35 nm)/LiF (5 nm) 双层时,观察到 C60(大尺寸)和 LiF(小尺寸)聚集体,表明下面的 C60 层没有被完全覆盖5 纳米厚的 LiF。因此,C60/LiF 界面处发生了一些混合,考虑到 C60 分子形成的渗透路径,这导致 C60/LiF(5 nm)双层具有良好的导电性。

<图片>

P3HT:PCBM、P3HT:PCBM/C60 (35 nm)、P3HT:PCBM/LiF (5 nm) 和 P3HT:PCBM/C60 (35 nm)/LiF 的敲击模式 AFM 高度(顶部)和相位(底部)图像(5 nm) 薄膜。相应的均方根 (rms) 粗糙度分别为 0.81、1.36、1.67 和 2.18 nm

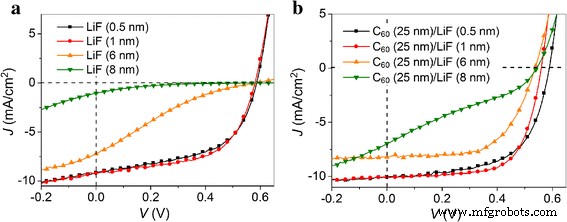

为了进一步研究 C60/LiF 双 CBL 对 PSC 器件性能的影响,我们将 C60 厚度固定在 25 nm 的最佳值,同时将 LiF 厚度从 0.5 更改为 8 nm。为了比较,还制造了具有 LiF 单 CBL 的器件。图 3 显示了 J -V 特性,记录在 100 mW/cm 2 使用不同厚度 LiF 的 LiF 单 CBL 和 C60/LiF 双 CBL 的 PSC 的照明(AM 1.5 G)。表 2 中总结了器件的相应光伏参数。具有 LiF 单 CBL 的器件在 1 nm 的最佳 LiF 厚度下的最大 PCE 为 3.06%。进一步增加厚度会导致 PCE 在 6 nm 处快速降低至 0.79%,在 8 nm 处快速降低至 0.06%。相比之下,具有 C60 (25 nm)/LiF 双 CBL 的器件在 LiF 厚度为 1 nm 时表现出更高的性能,峰值效率为 3.77%。更重要的是,随着厚度增加到 6 纳米和 8 纳米,PCE 分别达到 2.65% 和 1.10%,明显高于仅使用 LiF 的器件。应该提到的是,表 2 中显示的结果也是高度可重复的,正如设备特征参数的非常小的标准偏差所证明的那样(附加文件 1:表 S2)。例如,设备效率的标准偏差小于 0.2%(大多数设备为 0.1%),表明重现性高。此外,平均PCE显示出与表2中观察到的相同的趋势,这意味着不同组之间的效率比较是可靠的。

<图片>

J -V 特性,记录在 100 mW/cm 2 使用 a 的 PSC 的照明(AM 1.5 G) LiF单曲和b 具有不同 LiF 厚度的 C60 (25 nm)/LiF 双 CBL

如表 2 所示,基于 C60 (25 nm)/LiF 的 PSC 的 PCE 提高主要来自于 FF 和 J 的增加 sc 由于 R 减少 s。为了更好地理解 R s 还原,我们使用 photo-CELIV 技术研究 LiF 单层和 C60/LiF 双层的电荷传输特性 [30, 31]。附加文件 1:图 S1 显示了具有 LiF 单 CBL 和 C60/LiF 双 CBL 的 PSC 在不同电压上升速度下记录的 photo-CELIV 电流瞬变。在 photo-CELIV 中,提取电流最大的时间 (t max) 用于根据等式估计电荷载流子迁移率。 1 [27]。仅 LiF (6 nm) 器件的计算迁移率分别为 3.71、3.40 和 3.59 × 10 − 5 厘米 2 V − 1 s − 1 对于 10、20 和 30 kV/s 的电压斜率,分别表示迁移率与电压上升速度无关。相比之下,基于 C60 (25 nm)/LiF (6 nm) 的器件的估计迁移率分别为 3.81、3.56 和 3.09 × 10 − 4 厘米 2 V − 1 s − 1 电压斜率分别为 10、20 和 30 kV/s,比仅使用 LiF (6 nm) 的器件高一个数量级。引入 C60 层后迁移率的增加可归因于 C60/LiF 界面处发生的混合引起的导电性提高。此外,值得注意的是,仅基于 LiF (6 nm) 的器件的 photo-CELIV 峰比基于 C60 (25 nm)/LiF (6 nm) 的器件的光-CELIV 峰更宽,这表明电荷传输更加分散这是由于电子和空穴迁移率之间较大的不平衡造成的 [32, 33]。考虑到电子的提取被厚 LiF 层阻挡,这种不平衡归因于仅 LiF (6 nm) 的器件的电子迁移率极低。 P3HT:PCBM/LiF 界面处积累的电子屏蔽了施加的电场,从而降低了器件中的电荷提取率。相比之下,基于 C60 (25 nm)/LiF (6 nm) 的器件的窄峰意味着平衡的电子和空穴迁移率以及由于 C60 (25 nm)/LiF 的良好导电性而改善的电子提取(6 nm) 双层。

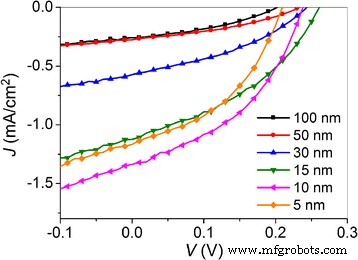

除了 FF 的显着改进外,J 加入 C60 (25 nm) 层后 sc 略有增强。考虑到旋涂的 P3HT:PCBM 共混膜由靠近顶面的富含 P3HT 的区域组成 [34, 35],我们推测在该区域产生的激子可以在 C60 的 P3HT/C60 界面处解离 (25 nm)/LiF 基器件,这导致 J sc 与没有 C60 夹层的器件相比。为了验证这一推测,我们制造了具有 ITO/PEDOT:PSS/P3HT/C60 (25 nm)/LiF/Al 器件结构的 PSC,其中 P3HT 的厚度从 5 到 100 nm 不等。图 4 显示了 J-V 这些设备在 100 mW/cm 2 下的特性 照明(AM 1.5 G),以及相应的光伏参数总结在附加文件 1:表 S3 中。发现J P3HT/C60 基太阳能电池的 sc 随 P3HT 厚度的减小而增加,这在 P3HT 中有限的激子扩散长度(~ 10 nm)方面是合理的。 J sc 达到最大值 1.34 mA/cm 2 P3HT 厚度为 10 nm,然后由于吸收不足而随着厚度进一步减小而下降到 5 nm。如上所述,这种 P3HT/C60 子电池很可能是在 P3HT:PCBM 活性层顶部沉积 25 纳米厚的 C60 后形成的,这导致 1.34 mA/cm 2 J 的增加 基于 C60/LiF 的设备在理想条件下的 sc [36]。通过比较 J 带有和不带有 C60 (25 nm) 中间层的器件的 sc 值,J 中的增强 sc 约为 1 mA/cm 2 (除了基于 LiF(8 纳米)的器件),这与我们的推测一致。

<图片>

J -V 具有ITO/PEDOT:PSS/P3HT(x nm)/C60 (25 nm)/LiF (1 nm)/Al 使用不同厚度的 P3HT

在 P3HT:PCBM 和 LiF 层之间引入 C60 层后,太阳能电池内的光场分布很可能发生改变,这将导致 J 的变化 sc [26, 37]。为了研究这种效应,我们首先模拟了带有和不带有 C60 夹层的器件的 P3HT:PCBM 活性层内的电场强度。如附加文件 1:图 S2a 所示,与没有 C60 夹层的器件相比,包含 C60 层的器件的积分场强度在短波长区域较弱,在长波长区域较强。这种趋势变得更加显着,同时,随着 C60 厚度的增加,观察到红移。附加文件 1:图 S2b 显示了原始 C60 薄膜和 P3HT:PCBM 薄膜的吸收光谱,上面沉积有和没有不同的 CBL。比较具有和不具有 8 纳米厚 LiF 的 P3HT:PCBM/C60 (25 nm) 薄膜的吸收光谱,两条曲线几乎完全重叠,表明 LiF 不吸收可见光。另一方面,与原始 P3HT:PCBM 薄膜相比,P3HT:PCBM/C60 薄膜在 400~510 nm 和 580~680 nm 的波长范围内具有更高的吸收。随着 C60 厚度的增加,这种吸收增强变得更加明显。直观地说,400~510 nm 波长范围内的吸收增强源于 C60 吸收(400~550 nm)。附加文件 1:图 S2c 显示了具有 LiF (5 nm) 单 CBL 和 C60 (25 nm)/LiF (5 nm) 双 CBL 的 PSC 的入射光子到电流转换效率 (IPCE) 光谱。与仅使用 LiF 的器件相比,由于 C60 膜中的寄生吸收,具有 C60/LiF 双 CBL 的器件在短波长处具有较低的 IPCE,而在长波长处由于光学间隔效应显示出较高的 IPCE,如以及P3HT/C60亚细胞的贡献。

从表 2 中可以看出,基于 C60 (25 nm)/LiF (8 nm) 的器件表现出 1.10% 的低 PCE,尽管该效率仍远高于 LiF (8 nm) 的 (0.06%) - 唯一的设备。低 PCE 是小 J 的结果 sc 和 FF,这是由大 R 引起的 s。如上所述,C60 (35 nm)/LiF (5 nm) 薄膜由于在 C60 和 LiF 层之间形成混合形态而具有良好的导电性(见图 2)。为了找出 C60 (25 nm)/LiF (8 nm) 薄膜电阻高的原因,在没有和有 C60 (25 nm)、LiF (8 nm) 和 C60 的 P3HT:PCBM 薄膜上进行了 AFM 测量(25 nm)/LiF (8 nm) 层沉积在顶部。如附加文件 1:图 S3 所示,在 C60 (25 nm) 膜中形成了较大的球形聚集体,而在 LiF (8 nm) 膜中形成了相对较小的聚集体,这与图 2 中的观察结果相似。在 C60(25 纳米)层的顶部沉积 8 纳米厚的 LiF,形态(小聚集体)与原始 LiF 膜的形态非常相似,表明底层 C60 聚集体完全被 8 纳米厚的覆盖利福。因此,我们推测厚的 LiF 在 C60 (25 nm)/LiF (8 nm) 双层膜的顶部积累,这阻碍了电子提取,从而导致了高 R s 的设备。

结论

总之,我们已经证明,通过在有源层和 LiF 层之间简单地引入 C60 层,厚的 LiF 可以用作 P3HT:PCBM 基 PSC 中的 CBL。具有 C60/LiF (5 nm) 双 CBL 的器件的峰值效率为 3.65%,而仅 LiF (5 nm) 的器件的 PCE 低两倍,为 1.79%。由于 C60/LiF 双层具有良好的导电性,因此提高了器件性能主要是由于高 FF。此外,J 在引入 C60 中间层后,sc 也得到了改善,这可以归因于 P3HT/C60 子电池的贡献以及 C60 的光学间隔效应。将 LiF 厚度进一步增加到 8 nm,C60/LiF 基器件和仅 LiF 器件的 PCE 分别迅速降低至 1.10% 和 0.06%。由于在 C60 (25 nm)/LiF (8 nm) 双层顶部积累的 LiF,电子传输受阻导致具有 C60/LiF (8 nm) 双 CBL 的器件的 PCE 下降。总之,这些结果表明,与 LiF 单层相比,C60/LiF 双层是一种更有前途的 CBL,用于制造高效和大规模的 PSC。

纳米材料

- 太阳能电池

- 用于染料敏化太阳能电池的纳米树

- 高效石墨烯太阳能电池

- 太阳能电池的纳米异质结

- 关于高效钙钛矿太阳能电池的简短进展报告

- 用于高性能硅/有机混合太阳能电池的具有溶剂处理的高导电 PEDOT:PSS 透明空穴传输层

- 在 FTO 上电沉积 SnO2 及其在平面异质结钙钛矿太阳能电池中作为电子传输层的应用

- ZnO 纳米晶体的合成及其在倒置聚合物太阳能电池中的应用

- 具有 CdSe QD/LiF 电子传输层的高效倒置钙钛矿太阳能电池

- 由金属纳米粒子组成的高效太阳能吸收器的数值研究

- 制备钙钛矿太阳能电池二氧化钛致密层的最佳钛前驱体

- 混合紫外线-臭氧处理的 rGO-PEDOT:PSS 作为倒平面钙钛矿太阳能电池中的高效空穴传输材料