用于先进 CMOS BEOL 工艺的等离子体感应充电效应的宽范围检测器

摘要

这项工作提出了一种改进的等离子体感应充电 (PID) 检测器,以扩大检测范围,用于在先进的 CMOS BEOL 工艺期间监测晶圆上可能的等离子体损坏。研究了具有扩展电容器的等离子体诱导损伤模式的新天线设计。通过采用新型PID检测器,提高了检测器的最大充电水平。

介绍

近年来,半导体工艺技术的发展不断缩小大规模集成电路的关键尺寸 [1,2,3]。为了在多功能和更强大的硅芯片中实现更紧密封装的晶体管,先进的 FinFET 逻辑工艺变得更加复杂。等离子体增强的反应离子蚀刻步骤 [4, 5] 在先进的纳米级工艺中变得不可避免,以实现对高封装密度电路 [6] 必不可少的高纵横比结构。对于 45 纳米以上的 CMOS 技术节点,晶体管栅极从带有二氧化硅的传统多晶硅栅极变为高 k 金属栅极堆叠 [7, 8]。这种变化使器件更容易受到等离子体引起的损坏,并可能导致对高 k 介电层的不可预见的潜在损坏。 [9]。在 FinFET 的最先进制造工艺中,许多 RF 等离子体步骤(例如蚀刻、沉积和清洁工艺)是不可避免的,这会产生更高频率的等离子体诱导充电事件 [10]。金属结构上可能会出现正电荷和负电荷。当这些电荷流过由预先存在的金属线、通孔和触点制成的导电路径时,通过电路的脆弱部分,尤其是通过晶体管栅极电介质的不希望的放电可能会导致严重的可靠性问题。例如,在干蚀刻步骤中,在反应表面散射撞击离子和溅射材料会在体鳍中造成更多缺陷 [11, 12]。为了避免等离子充电事件对电路造成不可逆转的损坏,给出了限制金属结构尺寸的设计规则。另一个减轻 PID 的例子包括使用保护二极管,它可以将等离子体充电电流分流远离敏感电路 [13]。原位蒸汽发生 (ISSG) 栅极氧化物的引入提高了其对等离子体损伤的耐受性 [14]。此外,还发现修整腔室和修改 PECVD-Ti 沉积工艺可以减轻等离子体引起的损坏 [15]。然而,这些方法中的大多数都会导致对电路设计灵活性或处理权衡的不利限制。

传统上,晶圆上测试模式已被用于监测等离子体诱导损伤 (PID) 水平 [16]。用于监视晶圆上 PID 的最常见和最广泛使用的参数是具有大型天线结构的晶体管门的击穿时间 (TDDB) 特性。通过在电压或电流应力测试下测量栅极介电层的退化,可以揭示栅极介电层的潜在损坏。因此,这些模式无法提供有关等离子体过程的实时反馈 [17]。在我们之前的工作中,在先进的 FinFET 技术中展示了晶圆上等离子体感应充电效应检测器。 PID 检测器使用电容耦合结构在浮栅上引起响应 [18,19,20]。因此,不会像传统的 PID 检测器那样损坏栅极介电层。在这些新探测器上,人们可以测量不断变化的 I-V 曲线,以找出天线门上电荷的强度、持续时间和极性。发现这些探测器可能会受到饱和效应的影响,因为某些记录位置的等离子体强度超过临界水平。为了扩展PID检测器的动态范围,本工作研究了新的天线门设计,成功地证明了感测范围的扩大。

方法

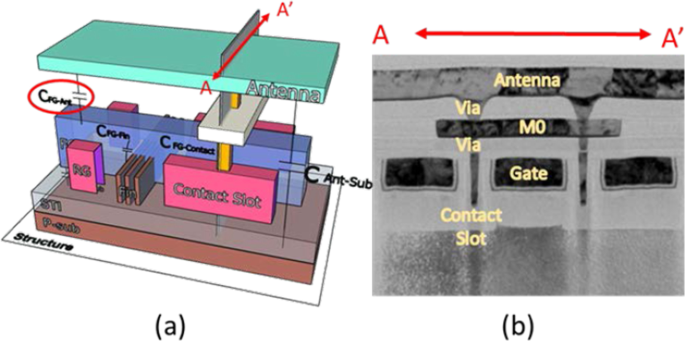

带有连接到天线节点的寄生电容器的等离子体诱导损伤 (PID) 检测器的 3D 示意图如图 1a 所示。与PID监控结构不同,该检测器利用长接触槽将天线电压耦合到浮栅上。横截面 TEM 照片如图 1b 所示。如图所示,收集电荷的接触槽与浮栅电容耦合。

<图片>

一 先前报道的原位 PID 检测器和天线电容器的 3D 插图在该结构中突出显示。 b PID检测器的TEM照片,其中该检测器的门长为140 nm

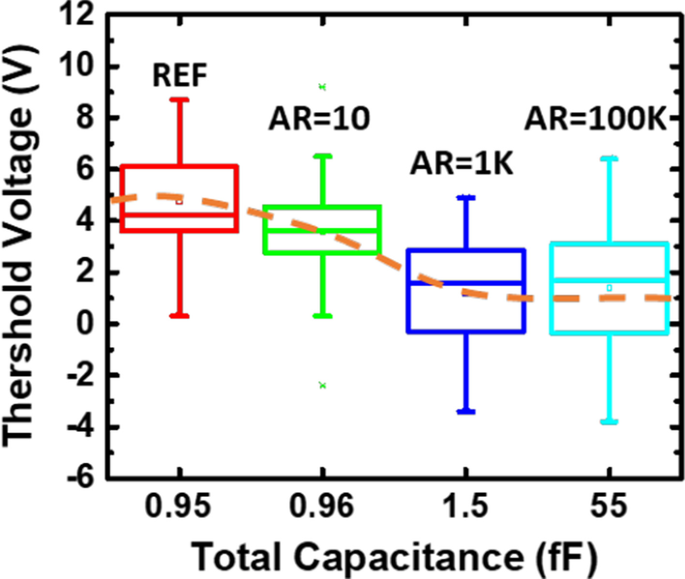

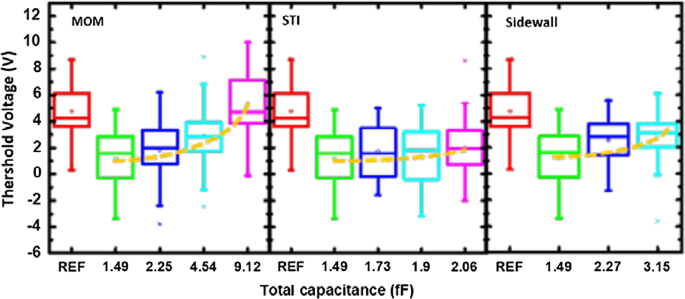

图 2 比较了这些探测器在 12 英寸晶圆上记录的阈值电压分布。负阈值电压偏移表明天线上收集了负电荷,将正电荷吸入浮栅,导致负阈值电压偏移。发现随着天线面积的增加,总电容的增加导致天线整体电压的降低,因此V的偏移更小

<图片>

不同尺寸天线样品的阈值电压范围,以及对应的天线总电容

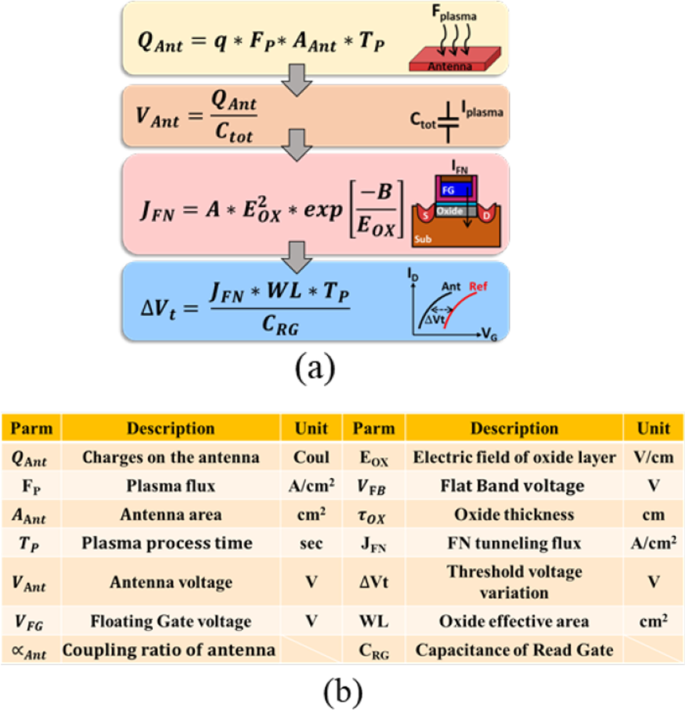

此处,在图 3a 中,概述了解释 PID 检测器基本操作原理的流程图。由于等离子电荷 (Q Ant) 被收集在天线上,天线门的电位,V 蚂蚁,因人而异。 V Ant 然后耦合到浮栅 (FG),促进电子进入或离开 FG 的隧穿。等离子处理后,V 根据 Q 的极性,这些检测器中的 t 可能变得更负或更正 蚂蚁。 V t 可由 FN 隧穿电流模型计算,参数列于图 3b。

<图片>

一 等离子电荷的流程图 (Q Ant) 收集在天线上以移动 V 吨。基于 FN 隧穿模型,ΔV t 可以计算。 b 参数列表及其定义

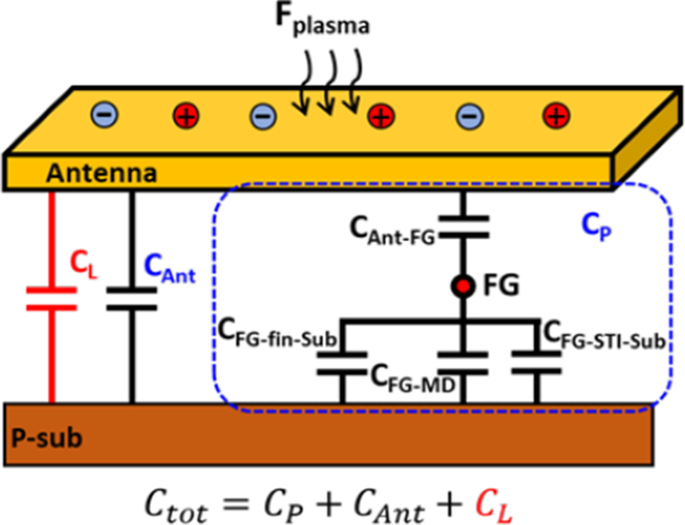

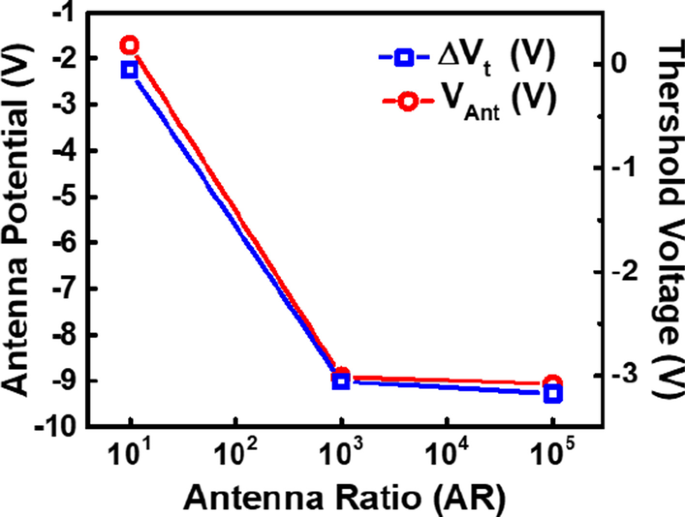

图 4 说明了基于 FG 的 PID 检测器上所有可能的电容。从图 5 可以看出,随着天线面积的增加,ΔV t 趋于饱和。作为 V 蚂蚁达到最高等级,Q 当电压水平过高时,蚂蚁开始泄漏。为避免等离子体通量水平超过探测器限制,有意增加天线电容,增加负载电容,降低天线电容占总电容的比例。

<图片>

天线结构上的电容与附加负载电容器的组成,旨在修改 PID 检测器的灵敏度。 C 在哪里 P是浮栅上的总寄生电容

<图片>

阈值电压电平和投影天线电压电平都在天线面积增加的方向图上饱和

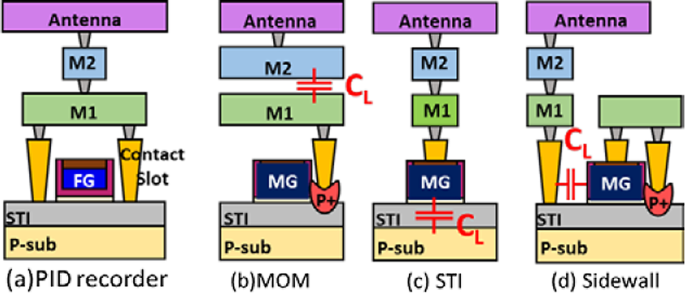

图 6a 显示了先前报道的原位 PID 检测器的 2D 结构,并呈现了实现附加电容器的三种结构。它们是 MOM 电容器,它使用金属层的较大重叠面积来增加图 6b 中的总电容,STI 电容器,它通过调整图 6c 中的金属栅极的长度来增加电容,以及侧壁电容器,它使用图 6d. 金属栅极和触点的重叠区域以形成额外的电容器。

<图片>

a 的横截面图 原位 PID 检测器,以及那些通过 b 实现的负载附加电容器 妈妈,c STI 和 d 侧壁,分别

实验结果与讨论

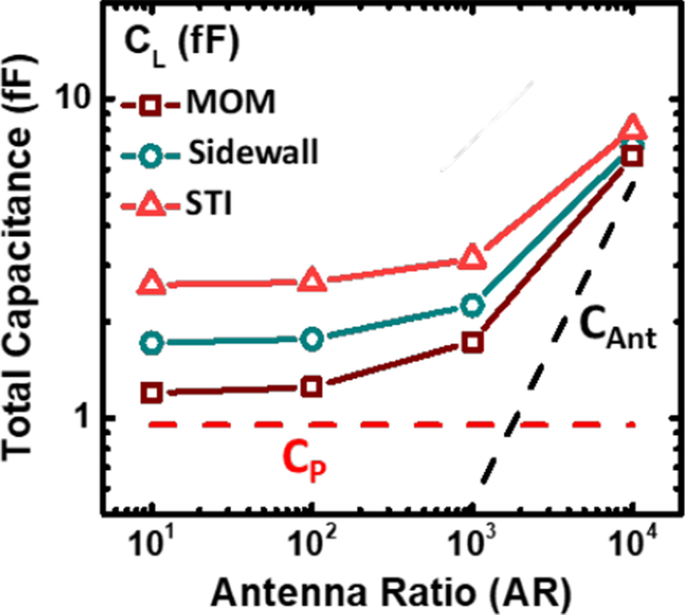

图 7 比较了添加不同类型负载电容器时的总电容与天线比。当天线比大于 1 K 时,总电容以天线电容为主。

<图片>

添加三种负载电容后总电容与天线比的比较

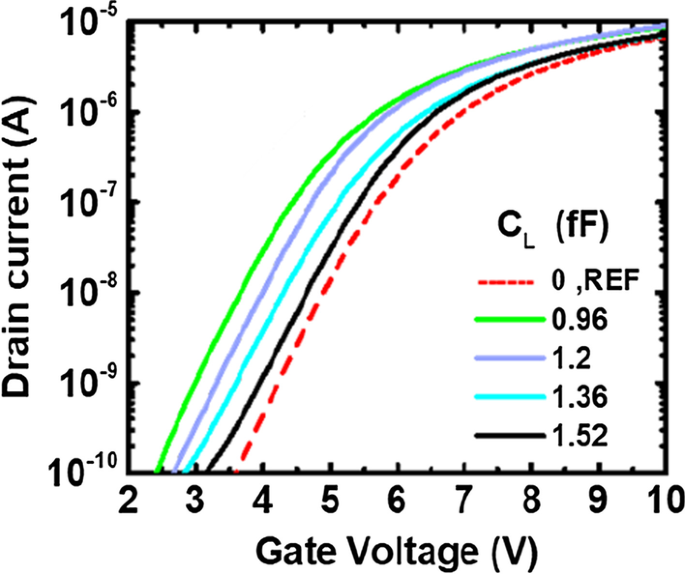

当增加的负载电容与天线电容相当时,总电容就会受到负载电容的影响。由于天线收集的最大电荷量是固定的;通过增加总电容,ΔV 预期下降,根据 ΔQ =C ΔV .因此,可以抑制检测范围的灵敏度,防止等离子体充电水平超过其原始极限时的饱和效应。 AR =10 器件的漏极电流特性与不同 STI 电容的比较如图 8 所示,当增加更大的负载电容时,天线电容占总电容的百分比降低。在相同的等离子充电通量下,一段时间后的总等离子电荷与天线面积成正比。因此,当总电容增加时,V Ant 预计会降低,从而可以检测到高等离子体通量水平。如图 8 所示,对于具有额外负载电容器的样品,在 I-V 曲线上发现较小的偏移。

<图片>

不同尺寸STI电容的I-V曲线,AR =10。当外部电容较大时,I-V曲线更接近参考单元的I-V曲线

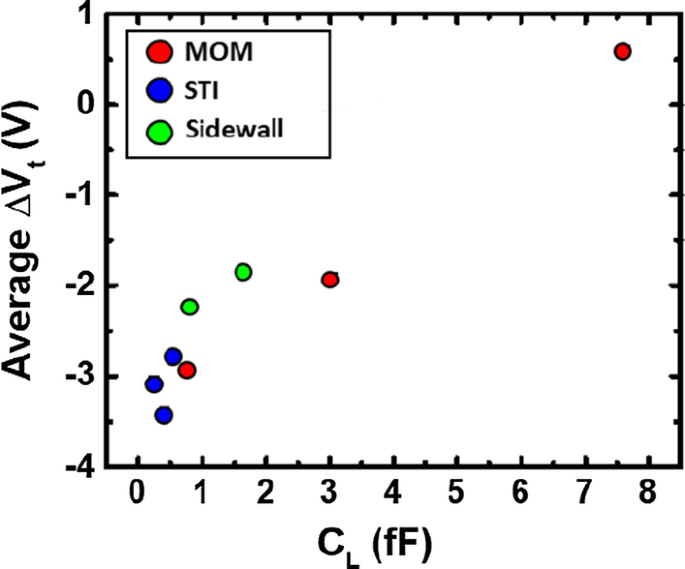

图 9 比较了从具有 AR =1 K 和不同尺寸 MOM、STI 和侧壁电容器的样本测量的阈值电压的箱形图。当负载电容增加时,平均观察到的阈值电压偏移较小。在实验设计中,C L by STI 结构太小,无法显示充电电平的影响。图 10 中的比较表明,增加负载电容器的三种方式也可以有效降低对等离子体充电的平均响应。额外的负载电容可以成功地扩大PID检测器的检测范围,同时降低检测器的灵敏度。为实现等离子体充电水平的大范围检测,一系列具有不同C水平的PID检测器 L 可以设计为一维阵列,用于检测高端和低端的等离子体充电水平。

<图片>

比较了在具有不同尺寸 MOM、STI 和侧壁电容器的样品上测量的阈值电压。所有设备的 AR 都相同,为 1 K

<图片>

平均ΔV的比较 t 与 C L 由三种电容器结构实现,其中 ΔV t 定义为 V t 检测器单元和参考单元之间的差异。数据表明,可以通过 C 获得降低的灵敏度 L增加

结论

本研究调查了一种新的天线门设计,以扩展 PID 监测检测器上等离子体感应充电水平的感应范围。通过添加负载电容器,可以防止因电荷泄漏而导致的高天线栅极电压,从而允许在 PID 检测器上记录更高水平的充电水平。这种新颖的设计有效地拓宽了先进CMOS BEOL工艺中等离子体充电水平的检测范围。

数据和材料的可用性

不适用。

缩写

- PID:

-

等离子损伤

- V :

-

阈值电压

- Q 蚂蚁:

-

天线上的电荷

- V 蚂蚁:

-

天线电压

- 妈妈:

-

金属氧化物金属

- AR:

-

天线比

- C :

-

负载电容

- C :

-

寄生电容

- C 蚂蚁:

-

天线电容

纳米材料

- CMOS 栅极电路

- Python for 循环

- IBM 研究人员获得半导体研究创新奖

- 用于 Micro-LED 和 VCSEL 的高级原子层沉积技术

- 以叶酸受体为靶点的生物类黄酮染料木素负载壳聚糖纳米颗粒可增强对宫颈癌的抗癌作用

- 接触非平衡等离子体对 Mn Х Fe3 − X О4 尖晶石结构和磁性能的影响

- 电荷分裂原位记录器 (CSIR),用于实时检查 FinFET BEOL 工艺中的等离子体充电效应

- BaTiO3/Nb:SrTiO3 外延异质结中铁电场效应引起的非对称电阻开关效应

- CuGeO3 纳米线作为高级钠离子电池负极材料的合成和研究

- FinFET Cu BEOL 工艺中等离子对金属间电介质的损伤的测试模式设计

- 深低温活化处理对用作锂离子电池阳极的大麻茎衍生碳的影响

- 镧改性钛酸铋陶瓷对能量收集铁电效应的粒度效应