通过理想原子层沉积的 Al2O3 隧道开关层改善掺杂 Mg 的 LiNbO3 薄膜的铁电性能

摘要

采用离子切片技术结合原子层沉积方法制备了由5% Mg掺杂的LiNbO3单晶薄膜和厚度为2至6 nm的超薄Al2O3层组成的双层结构。瞬态域开关电流测量结果表明,P-V 磁滞回线在 II 型模式下是对称的,每个周期只有一个电压脉冲,这可能是由于不对称电极形成的内置电场和内部压印场的补偿。此外,嵌入的Al2O3作为理想的隧道开关层,在铁电开关期间导通,但在施加脉冲电压的后开关或非开关期间关闭。 Al2O3 层阻止了副电极电荷注入等不利影响,提高了 Mg 掺杂 LiNbO3 铁电电容器的疲劳耐久性。该研究为提高铁电器件在非易失性存储器应用中的可靠性提供了可能的途径。

背景

铌酸锂 (LN) 单晶薄膜由于其优异的物理性能,[1,2,3,4,5,6] 已广泛应用于表面声波振荡器、电光调制器和基于域切换。最近,通过离子注入和晶圆键合技术制造了晶圆级铌酸锂绝缘体(LNOI),其在电光、声光和数据存储设备中的高密度集成电路方面具有巨大的应用潜力。 .该技术允许使用多种基板,例如 LN、硅,甚至 CMOS 电路 [3, 7,8,9]。然而,压印滞后回线源于 LN 薄膜的优选取向和较差的疲劳耐受性,由于副电极电荷注入,使极化反转的保持不稳定,这限制了它们在非易失性存储器件中的应用 [10,11,12 ,13]。与在铁电层和电极之间形成的界面无源层相关的优选取向,可以在相反的极化方向上感应强去极化场。它可以在去除施加的电压后或在后续脉冲应力的间歇时间期间驱除注入的电荷 [11, 12]。另一方面,由于界面钝化层的存在,LN薄膜的疲劳耐受性将通过在铁电开关后阻止来自副电极的电荷注入来提高。然而,如果施加脉冲周期的时间短于 0.5 s 以下,则疲劳过程会加速。这是由在某些频率下累积空间电荷的界面无源层贡献来描述的 [11]。据报道,嵌入的 Al2O3 介电薄膜可以在介电/铁电双层电容器中起到隧道开关的作用,例如在 Al2O3/Pb (Zr,Ti)O3 和 Al2O3/Mn 掺杂的 BiFeO3 双层结构中 [14,15 ,16]。 Al2O3 隧道开关在极化切换期间作为导体打开,但在完成极化切换或无切换操作后作为绝缘体关闭以阻止副电极电荷注入 [14]。因此,它可以防止不需要的注入电荷和极化反向切换,进而提高介质/铁电双层电容器的可靠性。

在本文中,我们制造了 200 nm 厚的 Z-cut 5% Mg 掺杂的全等 LN 单晶薄膜,然后在 LN 上沉积不同厚度(2-6 nm)的超薄 Al2O3 层以形成双层电容器结构。 Al2O3薄膜作为隧道开关层可以提高疲劳耐久性。非对称电极(Au/Pt 电极)旨在形成一个内置电场,以对抗由界面无源层引起的去极化场。电气结果显示了从域切换电流瞬变随时间转移的磁滞回线的对称性。同时,也证明了嵌入的Al2O3层起到了隧道开关层的作用,在铁电开关过程中可以打开,在极化开关完成或没有开关操作后关闭。

方法

Z-cut 5% Mg 掺杂的全等 LiNbO3 (LN) 单晶薄膜通过使用离子注入和晶片键合技术从它们的块状晶体上剥离,如别处所述 [10, 11, 17, 18]。具体而言,首先通过控制注入能量和注入离子的剂量,在所需深度的 LN 块状晶体表面注入 He 离子,然后通过 DC 沉积 5 nm Cr 粘附层和 100 nm Pt 底部电极层溅射(KJ Lesker PVD-75)。将表面层粘合到另一个覆盖有 1μm 厚 SiO2 缓冲层的 LN 衬底并切掉。通过化学机械抛光将LN薄膜的厚度控制在200 nm左右。随后,超薄 Al2O3 薄膜的厚度为 (d ) 的 2–6 nm 由 ALD (TFS-200, Beneq, Finland) 沉积。详细地说,前体气体是二乙基锌和去离子水。它们以 50 ms 的脉冲时间交替脉冲进入反应室,并通过在 200 °C 的反应温度下使用氩气吹扫 2 s 的步骤进行分离 [19]。最后,面积为1.0 × 10 −4 的顶部Au方形电极 厘米 2 通过金属浅掩模沉积。

通过光谱椭偏仪系统(GES-5E,SOPRA,Courbevoie,France)测量沉积在 Si 晶片上作为对比的 Al2O3 层的厚度。通过 X 射线衍射 (XRD) (Bruker D8 Advance) 在 θ-2θ 扫描模式下用 Cu K 分析薄膜结构 α 辐射以及横截面扫描电子显微镜(SEM、Sigma HD、Zeiss)。为了研究域切换动力学,使用单通道 Agilent 8114A 脉冲发生器将几个上升时间为 10 ns 的方波脉冲施加到顶部电极,底部电极接地。在电路中,域开关电流(I sw) 跨所有仪器的串联内部电阻器的总电阻使用 LeCroy HDO6054 示波器进行监测。脉冲发生器的两个输出电阻值R W和示波器的输入电阻R O 分别为 50 Ω。

结果与讨论

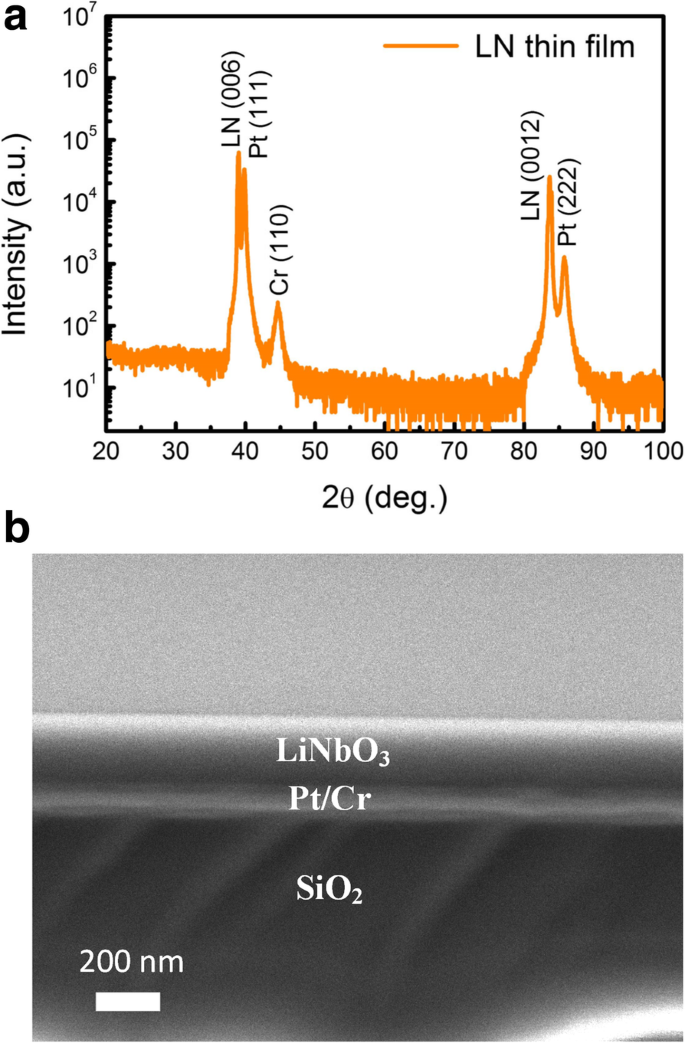

图 1a 显示了 Pt/Cr/SiO2/LN 衬底上的 LN 薄膜的 XRD 结果。薄膜具有很强的(00 l ) 在菱形相对称性中索引的反射。此外,还有一些 Pt 和 Cr 薄膜的衍射峰,如图 1a 所示。没有任何其他峰证实了没有相杂质的 LN 膜的高结晶度。图 1b 所示样品的横截面 SEM 图像展示了清晰的界面结构,具有 LN、Pt、Cr 和 SiO2 堆叠层。

<图片>

一 XRD图谱和b Z-cut 200 nm厚LN/Pt/Cr/SiO2/LN薄膜的横截面SEM图

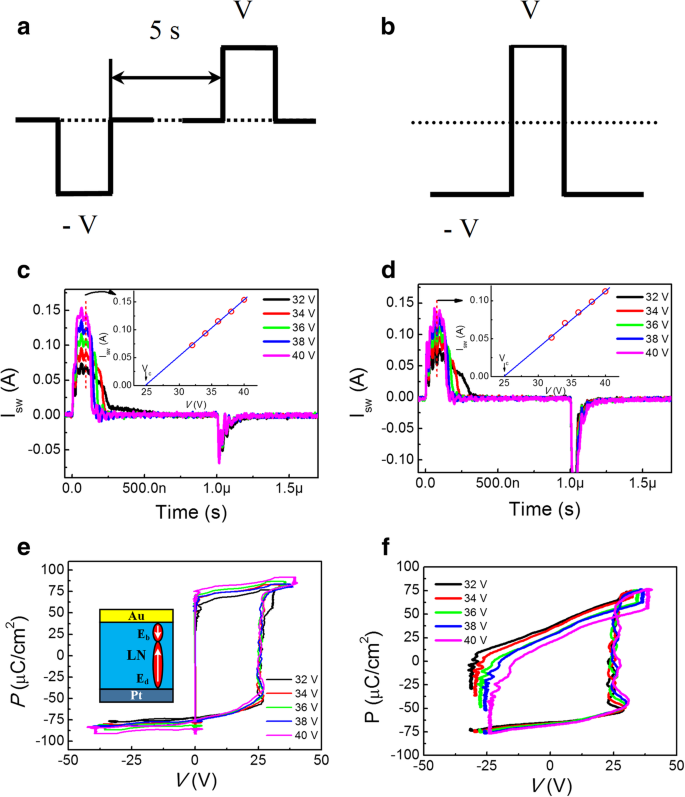

为了研究域切换动力学机制,设计了两种类型的脉冲电压模式,如图 2a 和 b [11] 所示。 I 型配置为极性相反的双脉冲,时间间隔为 5 s。施加第一个脉冲以切换指向顶部电极的向上极化状态,第二个脉冲可以切换向下极化。然而,受单通道脉冲生成的编程时间的限制,由于首选的畴取向,最小时间间隔太长而无法捕捉由第二个脉冲调用的畴切换电流瞬变。为了捕捉域切换电流瞬变,在类型 II 中提出了与负基线直流偏置重叠的单个脉冲,其中初始负直流偏置可以切换向上极化状态,正脉冲将域设置为向下。这里,两种类型脉冲的宽度设置为1μs。

<图片>

带有a的两种序列脉冲电压模式示意图 I型(两个相反极性的双脉冲)和b II 型(单个开关脉冲与负直流偏置重叠)。不同V下的域开关电流瞬变 应用于 c 中的原始样本 输入 I 和 d II 型模式,其中插图显示域切换电流平台对 V 的依赖性的线性拟合 . P -V 不同V下的磁滞回线 从 e 中的域切换电流瞬变转移 输入 I 和 f 类型二。 Au/LN/Pt结构示意图及内建电场方向E b 和去极化场 E d 在 e 的插图中

图 2c 和 d 显示了域开关电流瞬变与时间 (t ) Au/LN/Pt 结构样品在不同外加电压 (V ) 分别在 I 类和 II 类模式中。观察到域开关电流瞬变的平台宽度变窄但高度随着 V 的增加而增加 在 30 ns 的初始电容器充电电流后增加。两种模式的平台高度均随V的增加呈线性关系 结果通过数据的实线拟合总结在插图中 [11, 13]。矫顽电压 (V c) 两种模式中的值可以从与电压轴的线截距推导出约 24.7 V。开关脉冲终止后,电容放电电流在1 μs后出现,这表明优选畴取向是指向顶部电极的向上极化状态。

P -V 两种模式下不同施加电压下的磁滞回线可以直接从图 2c 和 d 中相应的域切换电流瞬变中转移,结果分别如图 2e 和 f 所示 [11, 20]。确定的正向矫顽电压约为 25 V,不随 V 而变化 是在两种类型的脉冲中获得的。矫顽电压接近V c 从线性 I 中提取 sw-V 绘制在图 2c 和 d 的插图中。与非掺杂 LN 薄膜不同,V c 是可变的,该值等于最大施加电压 [10]。对于 5% Mg 掺杂的 LN,定义的 V c 与 V 保持不变 ,如图 2e 和 f 所示。这是因为 Mg 掺杂可以产生 Li 位金属空位和与氧空位相关的缺陷,[21,22,23] 可以捕获空间电荷并有效缩短薄膜和顶部/底部之间的界面层的电阻退化时间电极 [11]。因此,域切换电流与电容器充电电流重叠以加速域切换速度并具有确定的 V c,如图 2c 和 d 所示。然而,受脉冲发生器的限制,当施加的脉冲电压增加超过 32 V 时,II 型模式下的输出基线电压不能对称偏移。与图 2e 中沿正电压轴的压印环相比,环的对称化是沿图 2f 中的电压轴实现,不同于 Pt/LiNbO3/Pt 结构中 P -V 类型 I 或类型 II 中的磁滞回线都印向正电压 [11]。对称P的原因 -V 图 2f 中的环路可能归因于设计的不对称电极(此处为 Au/Pt)。 Au电极的功函数为5.1 eV,略小于Pt(5.65 eV)[24]。会产生一个内置电场 (E b) 方向从顶部电极指向底部电极,如图 2e 的插图所示。去极化场 (E d) 由界面钝化层引起的与 E 方向相反 湾E d 可以在对称电极 (Pt/Pt) [11] 的类型 II 中的切换脉冲终止后很短的时间内切换回极化。在我们的实验中,E b 可以部分屏蔽 E d 并积累注入电荷以补偿内部压印场,[16] 这可以减慢反向切换时间。因此,切换域可以维持并且反向切换电流瞬变将被类型 II 脉冲捕获。然而,I型模式下两个极性相反的脉冲的时间间隔太长。在第一个脉冲之后,被 E 俘获的注入电荷 b 会逐渐被 E 赶出影片 d 在类型 I [11] 中的第二个脉冲到达之前。为了证明内置电场对环路对称性的归因,制备了 Pt/LiNbO3/Pt 对称结构样品,沿正电压轴的压印环路直接从附加的域开关电流瞬变中直接转移文件 1:图 S1a,电压/宽度为 30–40 V/500 ns 的正脉冲,如附加文件 1:图 S1b 所示。

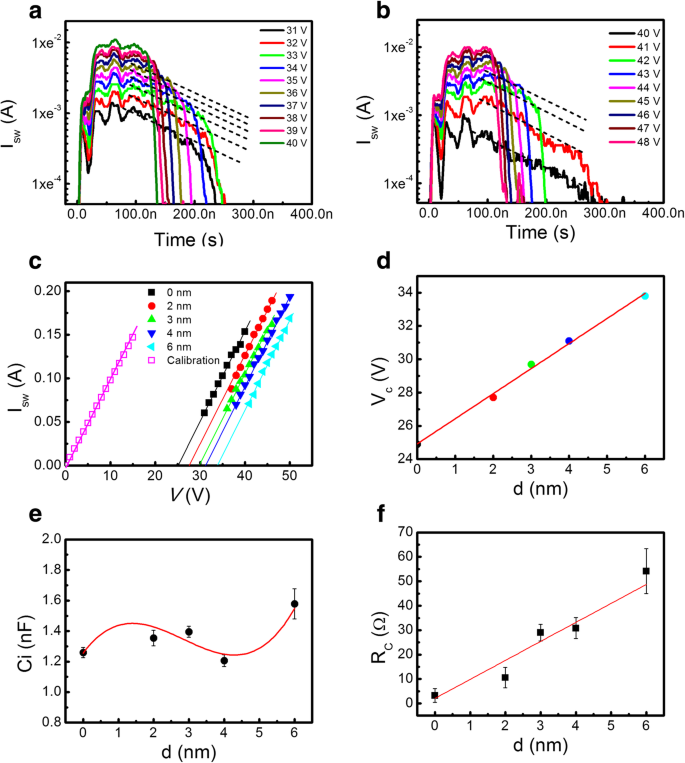

图 3a 和 b 显示了域切换电流 (I sw) 瞬态随时间变化 (t ) LN 和 Al2O3 (6 nm)/LN 样品在不同外加电压 (V ) 在类型 I 模式下。域切换平台期后,切换电流I sw 衰减并由下式给出:[13]

$$ {I}_{\mathrm{sw}}={I_{\mathrm{sw}}}^0\exp \left(-\frac{t-{t}_0}{R_{\mathrm{L} {C}_{\mathrm{i}}}\right)\\left({t}_0\le t\le {t}_{\mathrm{sw}}\right) $$ (1)其中 t 0, t sw, R L 和 C i 分别为域切换的开始时间、域切换的完成时间、电路中所有串联电阻的总电阻和界面非铁电电容。这描述了电荷俘获效应,可以将其建模为与理想铁电层串联的界面无源层。 我 sw 0 定义为开关电流,由下式给出:

$$ {I_{\mathrm{sw}}}^0=\frac{V-{V}_{\mathrm{fc}}}{R_{\mathrm{L}}} $$ (2) <图片>

一 , b 我 sw-t 不同V下的I型依赖 应用于 Al2O3/LN 双层,Al2O3 厚度 d =0 和 6 nm,分别由一系列平行虚线拟合到方程。 (1). c 在不同 Al2O3 层厚度下,作为外加电压的函数的域切换电流的平台,其中实线显示数据与方程的最佳拟合。 (2). d Al2O3 层厚度 d 矫顽电压的依赖性 (V c) 提取自 c . e , f 提取的界面电容C i 和接触电阻 R C 作为 Al2O3 层厚度的函数 d

在畴切换期间,施加在铁电层上的电压固定在矫顽电压V fc 和额外电压 (V -V fc) 应用于 R L.R L 还包括电路寄生电阻 (R P) 和接触电阻 (R c) 薄膜与电极之间;因此,R L =R O + R W + R P + R C. 开关电流瞬变随时间的衰减部分可以通过方程拟合。 (1).时间常数 R LC i 可以从拟合线的斜率估计。图 3c 显示了 I sw 0 -V 具有不同 Al2O3 厚度的绘图。 R L 和 V C 是从斜率和 X - 线性拟合线的轴截距。可以看出,V C随着Al2O3厚度的增加而线性增加d ,如图 3d 所示。在这里,C i 值被估计为每个 V 的误差界限 在图 3e [13] 中。结果表明,C 随着 Al2O3 层厚度从 0 增加到 6 nm,i 值几乎保持不变 (1.4 ± 0.2) nF。

为了计算 R C、上下电极短接,可得到R P (~ 2 Ω) 具有不同的施加电压,如图 3c 中空心符号所示的电路校准。因此,R C对应d 计算结果如图 3f 所示。 R C 在 d 处从 3 ± 2.5 Ω 线性增加 =0 至 55 ± 10 Ω 在 d =6 nm。几乎 d -独立的大C i 值表明 Al2O3 层在域切换期间用作串联电阻。这意味着在FE切换过程中Al2O3隧道开关处于开启状态。

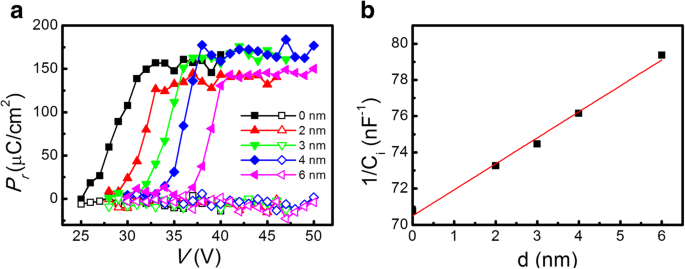

为了获得 FE 非开关期间双层的总电容,开关 (P sw) 和非切换 (P nsw) 极化与 V 与 d 测量在 I 型模式脉冲下从 0 增加到 6 nm,结果如图 4a 所示。选择I型脉冲的目的是为了得到P的曲线 nsw-V 当外加电压方向与极化方向一致时,总电容(C 双层的 tot) 可以从关系中计算出来,C 总 =S ·dP nsw/dV , 其中 S 是电极面积。在I型脉冲模式下可以完全排除FE开关的电荷效应,但使用II型模式无法通过负开关极化实现这种效果,可以将电荷注入所涉及的极化转回。 P 的区别 sw 和 P nsw 是 2Pr,如图 4a 所示。它与 d 的变化很小 从 0 到 6 nm,而 P nsw(空心符号)信号太弱,无法用示波器监测。为了证明 Al2O3 隧道开关层作为介质电容器工作,直接 C 使用低频阻抗分析仪在 100 kHz 下进行了没有额外直流偏置的 tot 测量,其结果如图 4b 所示,可以通过方程拟合。 (3):

$$ \frac{1}{C_{\mathrm{tot}}}=\frac{1}{C_{\mathrm{f}}}+\frac{d}{\varepsilon_0{\varepsilon}_{\mathrm {Al}}S} $$ (3)其中 ε Al 是 Al2O3 层的介电常数,ε 0 是自由空间的真空介电常数。 C f 和 S 分别代表铁电层和电极面积的电容。图 4b 显示了线性 1/C tot 与 d 绘图,这表明 Al2O3 层在非开关情况下或后开关情况下变成了高度绝缘的介电膜。可以推导出C f ≈ 14 pF 和 ε Al ≈ 7.9 从方程。 (3).因此,插入的薄 Al2O3 层被证明是一种介电电容器。在FE非开关期间以及FE开关之后,Al2O3隧道开关作为绝缘体闭合。

<图片>

一 切换 (P sw) 和非切换 (P nsw) 极化与 V 与 d 在 I 型模式的脉冲下,从 0 增加到 6 nm。 b Al2O3 层厚度 d 1/C 的依赖 由阻抗分析仪在 100 kHz 下测量的 tot

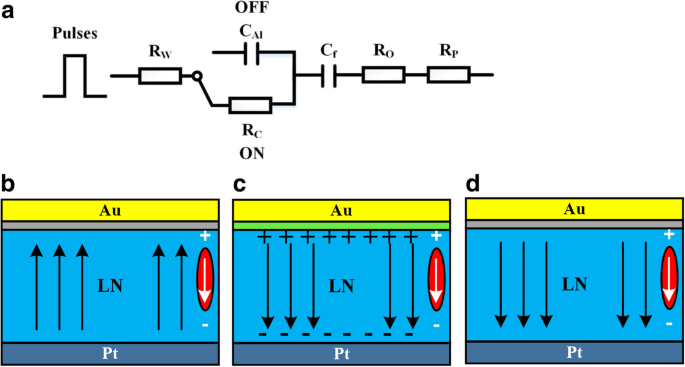

图 5 显示了在 I 型或 II 型模式下切换的 Al2O3/LN 双层结构的示意图。图 5a 描绘了 Al2O3 隧道开关串联电阻和电容的等效开关电路。在初始状态下,如图 5b 所示,首选极化方向是指向顶部电极的向上极化状态。由不对称电极引起的内置电场从 Au 电极指向 Pt 电极。施加极化电压时,会发生 FE 切换。可以理解,施加的电压与电路中的电容成反比。在 Al2O3/LN 双层结构中,在 FE 开关过程中,LN 层具有较大的电容。因此,大部分外加电压施加在 Al2O3 层上。通过电极电荷注入超薄 Al2O3 层。当施加的电压超过 Al2O3 隧道阈值时,它会作为电阻开启,如图 5c 所示。 FE开关完成后或在非开关情况下,LN层的电容非常小,Al2O3上的外加电压下降到低于隧道阈值电压。此时,Al2O3 层充当绝缘体并关闭,如图 5d 所示。

<图片>

转换为 I 型或 II 型的 Al2O3/LN 双层结构示意图。 一 Al2O3 隧道开关串联电阻和电容的等效通断电路示意图。 b 初始优选极化方向和内置电场; c Al2O3隧道开关开启和域切换; d Al2O3隧道开关关断和极化保持

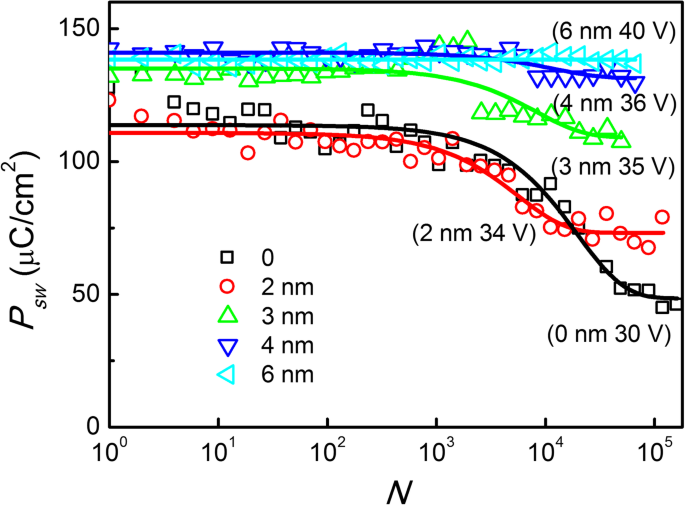

图 6 显示了 Al2O3/LN 双层结构中切换极化的循环次数依赖性,Al2O3 的厚度在 I 型模式下从 0 到 6 nm 不等。脉冲宽度为 1000 ns,周期为 0.5 s。可以清楚地看出,Al2O3/LN双层结构的疲劳耐久性随着Al2O3厚度的增加而逐渐提高,超过10 4 脉冲应力循环。 II 型模式下的疲劳特性与 I 型模式下的结果相似,如附加文件 1:支持信息图 S2 中所示。不幸的是,在II型模式下长时间施加接近10 4 的直流电压后,很容易发生电击穿。 脉冲应力循环。可以使用每个循环内畴壁钉扎和脱钉共存的模型拟合数据,如图 6 中的实线所示,其中疲劳物理归因于电极电荷注入 [13]。当Al2O3层插入Au电极和LN层之间时,可以阻断副电极注入电荷路径,提高疲劳耐久性。然而,在双层结构中,还应进一步考虑一些问题。例如,随着 Al2O3 的厚度从 0 增加到 6 nm,矫顽电压从接近 25V 增加到 34 V,这可以通过提高 Al2O3 层的质量来降低。实际上,少量高质量或缺陷较少的Al2O3原子层可以有效阻挡电极注入的电荷,这在其他地方通过优化原子层沉积工艺条件(如温度和时间)得到证实[25]。

<图片>

Al2O3/LN双层结构中Al2O3厚度在0到6 nm范围内的循环数依赖性在超过10 4 脉冲应力循环。脉冲宽度为1000 ns,周期为0.5 s

最近,我们在以下研究工作中提出了基于可擦除导电带电畴壁和非破坏性电读出极化状态的铁电畴壁存储器 [26, 27]。铌酸锂单晶中带电畴壁的大电导率是在畴切换后获得的 [28, 29]。因此,硅衬底上较薄的铌酸锂单晶薄膜是集成铁电畴壁存储器的有前景的材料,通过设计Al2O3/铌酸锂双层可以提高其保持力和疲劳耐久性。

结论

通过从块状 LN 单晶表面离子切片制备 200 纳米 5% Mg 掺杂的 LiNbO3 单晶薄膜,然后在 5 % Mg 掺杂的 LN 薄膜通过原子层沉积形成双层结构。对称的P-V 在 II 型模式下施加脉冲电压下观察到沿电压轴的磁滞回线,这可能归因于 Au/LiNbO3/Pt 中不对称电极引起的内置电场和内部压印场的补偿。域切换电流 (I sw) 瞬态及其传递的 P-V 磁滞回线显示超薄 Al2O3 层起到了理想的隧道开关的作用。它在 FE 开关期间导通,但在非开关期间或 FE 开关后关闭,最大限度地减少对 FE 开关的不利干扰。此外,随着隧道开关层厚度从 2nm 增加到 6 nm,FE 电容器的疲劳耐久性逐渐提高。 Al2O3/LN双层结构为设计坚固的铁电器件以缓解电极电荷注入疲劳问题铺平了道路。

缩写

- ALD:

-

原子层沉积

- CMOS:

-

互补金属氧化物半导体

- FE:

-

铁电体

- LN:

-

铌酸锂

- SEM:

-

扫描电镜

- XRD:

-

X射线衍射

纳米材料

- 用于 Micro-LED 和 VCSEL 的高级原子层沉积技术

- HfO2/TiO2/HfO2 三层结构 RRAM 器件在原子层沉积制备的 Pt 和 TiN 涂层衬底上的双极电阻开关特性

- 通过等离子体增强原子层沉积制备的 Co3O4 涂层 TiO2 粉末的光催化性能

- 通过界面层设计调整 ZnO 薄膜的表面形貌和特性

- 通过超循环原子层沉积调节 ZnO 薄膜的费米能级

- 制备分层 ZnO@NiO 核壳异质结构以提高光催化性能

- 在 c 面 GaN 上沉积的 AlN 原子层中界面和电特性的厚度依赖性

- 蚀刻变化对 Ge/Si 沟道形成和器件性能的影响

- T 形栅极双源隧道场效应晶体管的模拟/射频性能

- 增强 c 轴取向外延 Ba 掺杂 BiCuSeO 薄膜的热电性能

- 使用二氧化碳的低温等离子体增强原子层沉积 SiO2

- 通过微波退火增强原子层沉积的 Al2O3/ZrO2/Al2O3 MIM 电容器的介电增强