具有不同 MOS 电容的负电容场效应晶体管的比较研究

摘要

我们在实验中展示了基于 HfZrOx 的场效应晶体管 (FET) 的负电容 (NC) 效应。改进的I DS、SS 和 G 与控制金属氧化物半导体 (MOS) FET 相比,已经实现了 m 的 NCFET。在本实验中,不同钝化时间的底部 MIS 晶体管等效于具有不同 MOS 电容的 NC 器件。同时,由于C之间的良好匹配,钝化40分钟的NCFET的电学性能优于钝化60分钟的NCFET FE 和 C 摩斯。虽然没有达到sub-60 mV/decade的SS,但获得了有利于逻辑应用的非滞后传输特性。

介绍

随着晶体管的缩小,集成电路(IC)的集成度不断提高。随之而来的功耗问题亟待解决。为了规避这个问题,应该降低晶体管的工作电压[1]。 MOSFET的亚阈值摆幅(SS)在室温下不能低于60 mV/decade,限制了阈值电压V的降低 TH 和电源电压 V DD [2]。许多努力致力于研究和开发具有新颖传输和开关机制以克服玻尔兹曼极限的器件,包括负电容场效应晶体管 (NCEFT) [3, 4]、电阻栅极 FET [5]、纳米级机电 FET (NEMFET) [6, 7],碰撞电离金属氧化物半导体 (I-MOS) [8, 9] 和隧道 FET [10, 11]。其中,NCFET因其可以在不损失驱动电流的情况下实现陡峭的SS而备受关注[12,13,14,15]。掺杂的 HfO2(例如,HfZrOx (HZO) 和 HfSiOx ) 已广泛应用于 NCFET [4, 16, 17];它与 CMOS 工艺兼容 [18]。一项理论研究表明,由于不匹配的铁电电容 C 会出现不希望的滞后现象 FE 到底层 MOS 电容 C NCFET 中的 MOS [19]。但是C之间的匹配效果 FE 和 C MOS对NCFETs电特性的影响仍然是实验中的一个问题。

在这项工作中,基于C之间的不同匹配,研究了具有不同MOS电容的NC Ge FET的电气特性。 FE 和 C 摩斯。虽然没有出现小于 60 mV/decade 的 SS,但获得了无滞后传输特性和更好的电性能。 C 的表观峰 FE 与 V FE 曲线展示了基于 HZO 的 NCFET 的 NC 效应。 C的更好匹配 FE 和 C MOS有助于陡峭的SS和更高的电流,有利于逻辑应用。

方法

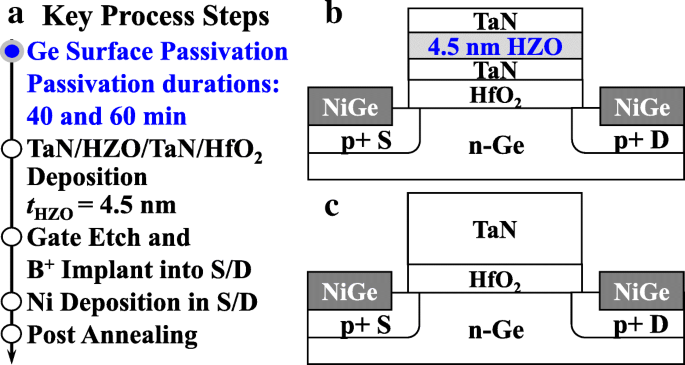

Ge NCFET 的关键制造工艺如图 1a 所示。电阻率为 0.088-0.14 Ω·cm 的四英寸 n-Ge(001) 晶片用作起始衬底。栅极前清洗后,将 Ge 晶片装入超高真空室,使用 Si2H6 进行表面钝化。使用了 40 和 60 min 两个钝化持续时间。然后,沉积 TaN/HZO/TaN/HfO2 叠层。 HfO2 介电层和 HZO FE 层的厚度分别为 4.35 和 4.5 nm。在栅极图案化和蚀刻之后,使用硼离子 (B + ) 在能量为 30 keV 和剂量为 1 × 10 15 cm −2 . S/D 金属镍是使用剥离工艺形成的。最后,在 450 °C 下进行 30 s 的快速热退火。还制造了具有 TaN/HfO2 堆栈的控制 MOSFET。图 1b 和 c 分别显示了制造的 NCFET 和控制 MOSFET 的示意图。制造的NCFET中的内部金属栅极抵消了沟道表面的电位,称为MFMIS结构。

<图片>

一 制造的 NC 设备的关键工艺步骤。制造的b的示意图 NCFET 和 c 控制MOSFET

结果与讨论

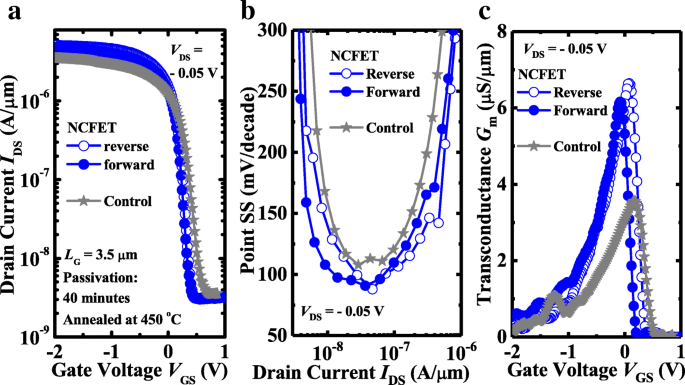

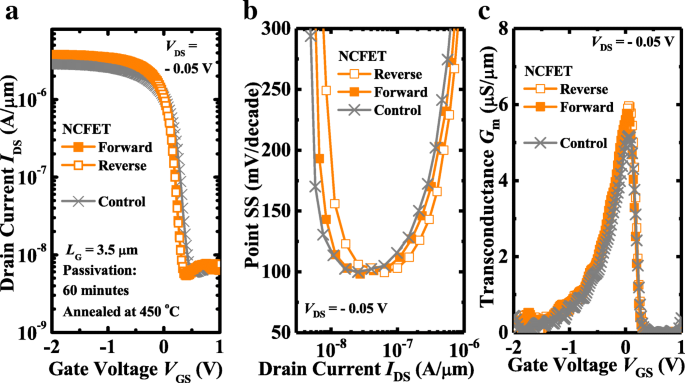

图 2a 绘制了测量的 I DS-V 表面钝化时间为 40 min 的一对 NCFET 和控制 MOSFET 的 GS 曲线。两个器件的栅极长度 L G 为 3.5 μm。钝化 40 min 的 NC 器件具有显着提高的 I DS 比控制 MOSFET。 NCFET 的传输曲线表现出非滞后特性。点 SS 与 I 图 2b 中的 DS 曲线表明,NC 晶体管比控制器件提高了 SS,尽管 SS 低于 60 mV/decade。图 2c 显示 NC 晶体管获得显着提升的线性跨导 G m 在 V 处的控制设备上 DS of − 0.05 V. 图 3 比较了 NCFET 和具有表面钝化 60 分钟的控制 MOSFET 的电气性能。同样,I DS,点 SS 和 G m NCFET优于控制MOSFET。

<图片>

一 测量的 I DS-V 钝化时间为 40 min 的 NCFET 和控制 MOSFET 的 GS 曲线。 b 的比较 点 SS 与 I DS 和 c G NC FET与控制MOSFET之间的m特性

<图片>

一 测量的 I DS-V 钝化时间为 60 min 的 NCFET 和控制 MOSFET 的 GS 曲线。 b 的比较 点 SS 与 I DS 和 c G NCFET与控制MOSFET之间的m特性

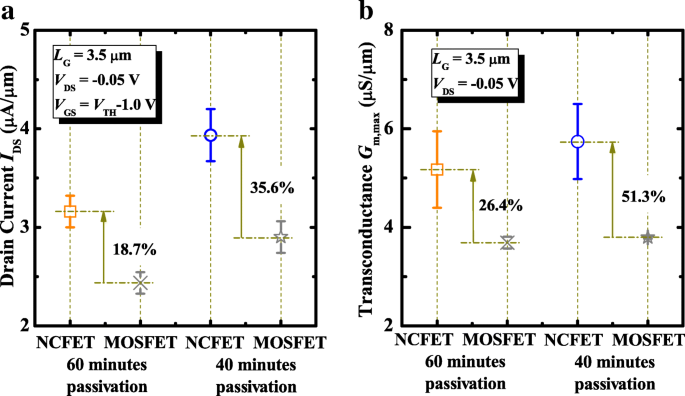

图 4a 显示了 V 下 NCFET 和控制 MOSFET 的驱动电流统计结果 DS of − 0.05 V 和 V GS-V TH =− 1.0 V. NCFET 在 I 方面表现出 18.7% 和 35.6% 的改进 与对照器件相比,DS 分别用于 60 min 和 40 min 表面钝化。据推测,钝化 40 min 的 NCFET 在 C 之间具有更好的匹配 MOS 和 C NC 设备上的 FE 为 60 min。图 4b 显示 NCFET 在最大跨导 G 方面获得了 26.4% 和 51.3% 的改进 与控制装置相比,分别在 60 min 和 40 min 表面钝化时的 m,max。可以看出,表面钝化 40 min 的控制 MOSFET 具有更高的 I DS 和 G m,max 比钝化 60 min 的器件大,这是由于 C MOS 由较小的等效氧化物厚度 (E OT)。内部金属栅极提供等电位面;该设备可以等效地建模为电容分压器。总电容C G 是一系列的 C FE 和 C 摩斯。由于 NC 效应,内部栅极电压被放大。内部电压放大系数β =∣ C FE ∣ / ∣ C FE ∣ − C MOS 当 |C 时获得最大值 MOS| =|C FE| [20, 21]。实现C的优化匹配 FE 和 C MOS是提高导通电流的前提。

<图片>

统计a 我 DS 和 b G 钝化持续时间为 40 和 60 分钟的 NCFET 和控制 MOSFET 的 m 结果

提取的 V int 与栅极电压 V GS 曲线如图 5a 所示。 V 由于 I 的假设,可以提取 NC 晶体管的 int DS-V NC 晶体管的 int 曲线与 I 完全相同 DS-V 控制装置的GS曲线。内部电压放大系数dV int/dV GS如图5b所示。 dV int/dV 在 V 的宽扫描范围内实现 GS> 1 具有 40 min 表面钝化的 NCFET 的 GS,在测量过程中导致比控制设备更陡峭的 SS,这是由于局部极化切换 [22]。这与图 2b 中的上述结果一致。对于钝化时间为 60 min 的 NCFET,内部电压放大系数 dV int/dV 在 V 范围内达到 GS> 1 GS <0 V 用于 V 的双扫描 GS,与图 3b 中升高的 SS 一致。

<图片>

一 提取的 V int 作为 V 的函数 GS 曲线。 b 内部电压放大系数 vs V GS曲线

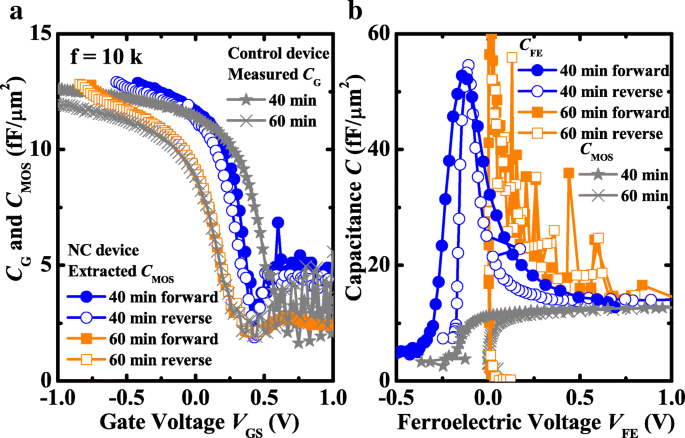

图 6a 显示了提取的 C MOS 与 V 依赖于 V 的 NC 晶体管的 GS 曲线 int-V 图 5a 中的 GS 和 C G-V 控制 MOSFET 的 GS 曲线。提取的 C MOS与实测C吻合良好 G. 因此,证明了计算方法的有效性。 C FE 和 C MOS 与 V FE 曲线如图 6b 所示。从NC效应开始,负C的绝对值 晶体管的FE超过C V双扫MOS GS 一直在图 6b 中。 |C FE|> C MOS 和 C FE <0 可导致无滞后特性,C 的匹配 MOS 和 C FE 有利于逻辑应用 [23, 24]。无滞后特性图。观察到图 2a 和 3a 归因于所有域匹配和抑制电荷捕获 [25]。稳定的极化切换是非滞后特性的原因 [26]。此外,大的内栅极增益 dV int/dV G> 1 归因于 |C 之间的微小差异 FE|和 C MOS 在亚阈值区域,导致 NC 器件的陡峭 SS。同时,C之间有更好的匹配 FE 和 C 钝化时间为 40 分钟的 NCFET 的 MOS 比钝化时间为 60 分钟的 NCFET。因此,这提供了直接证据,表明钝化时间为 40 min 的 NCFET 比钝化时间为 60 min 的 NCFET 具有更好的电气性能。 FE 极化改变了 V FE;因此,FE 的收费各不相同。总电荷倍增,除 V 增加外,还归因于 FE 极化 GS。换句话说,对于给定的 V GS,通道中的电荷增加,所以 I DS 改进。因此,实验中出现了陡峭的传递特性SS。

<图片>

一 测量的 C G 和提取 C MOS 作为 V 的函数 GS。 b C FE 和 C MOS 与 V 有限元曲线

结论

钝化时间为 40 和 60 分钟的 NCFET 获得了无滞后传输特性。在实验中,钝化时间为 40 min 的 NC Ge pFET 比钝化时间为 60 min 的 NC 器件具有更好的电气特性。我们还展示了基于 HZO 的 NCFET 的 NC 效应。对于 NCFET,陡峭的 SS 和 dV int/dV 获得 GS> 1。钝化时间为 40 min 的 NCFET 在 C 之间实现了良好的匹配 FE 和 C MOS,这有助于非滞后特性。不同的NC行为被认为与FE薄膜中的微观畴壁切换有关。

数据和材料的可用性

本文包含支持本文结论的数据集。

缩写

- B + :

-

硼离子

- E 加时:

-

等效氧化层厚度

- FET:

-

场效应晶体管

- HZO:

-

HfZrOx

- IC:

-

集成电路

- I-MOS:

-

碰撞电离金属氧化物半导体

- MOS:

-

金属氧化物半导体

- NC:

-

负电容

- NCFET:

-

负电容场效应晶体管

- NEMFET:

-

纳米机电场效应管

- 标准/日期:

-

源/漏

- SS:

-

亚阈值摆动

纳米材料