关于具有 2DEG 通道和新型 GaN 纳米柱垂直场效应晶体管 (FET) 的 Baliga 品质因数 (BFOM) 增强带图案的基材

摘要

一种具有 2DEG 的新型增强型垂直 GaN 场效应晶体管 (FET),用于降低导通电阻 (R 在这项工作中提出了用于提高击穿电压 (BV) 的 ON) 和衬底图案 (SP)。通过精心设计 SP 的宽度和高度,可以在不显着影响 R 的情况下分离 p-GaN 帽下的高集中电场(E-field) ON,得到增强的 Baliga 品质因数 (BFOM, BV 2 /R 在)。通过实验校准的 ATLAS 模拟验证,与没有图案化衬底的 FET 相比,具有 700 纳米长和 4.6 微米宽的 SP 的器件具有六倍高的 BFOM。此外,所提出的支柱器件和内部的SP仅占据纳米级区域,使得此类器件能够高密度集成,这使其在未来的电源应用中具有巨大潜力。

背景

如今,ZnO、In2O3、SiC 和氮化镓 (GaN) 等宽带隙半导体已引起人们的关注 [1,2,3,4,5]。然而,考虑到电子特性,横向 AlGaN/GaN 高电子迁移率晶体管 (HEMT) 被广泛认为是在功率或频率应用中替代 Si 基器件的潜在候选者,因为它具有更高的击穿电压 (BV) 以及热稳定性越强。很多努力,例如p型帽[6, 7],氟离子注入[8, 9],薄势垒[10, 11],双通道[5, 12]和场耦合栅极[13] , 实现了增强型HEMT,以简化驱动电路。

然而,这些技术面临着许多严峻的挑战,例如阈值电压的低均匀性、垂直芯片面积的浪费、电流崩溃、有限的 Baliga 品质因数 (BFOM) 等。特别是,漂移长度和 BV 之间的矛盾会对器件的缩小产生负面影响 [14, 15]。换句话说,更小的器件导致更低的 BV,其中更难采用通过优化电场分布来促进 BFOM 的结端子。为此,已经提出了背势垒 [16]、掩埋结 [17]、量子阱场板 [18] 和其他插入横向 HEMT 的结构,这些结构表现出电场板的特征,以通过利用来增强 BV芯片的垂直区域。

另一方面,凭借 GaN 的优越性质,体 GaN 垂直场效应晶体管 (VFET) 由于更容易实现增强型功能和垂直区域的充分利用而受到越来越多的关注 [19 ,20,21,22]。通过实验或模拟提出了许多新颖的结构来倾斜 BV 并同时降低导通电阻 (R ON) [23,24,25]。然而,更不用说在 GaN 中制造超级结 (SJ) 的困难,高迁移率二维电子气 (2DEG) 的缺乏导致了更高的 R ON [26],这阻碍了此类设备中BFOM的优化。

在这项工作中,一种具有 2DEG 的新型增强型垂直 GaN FET 用于降低 R 提出了用于增强 BV 的 ON 和基板图案 (SP),其中 2DEG 通道和 SP 的组合有效地平衡了低导通电阻和高 BV 之间的矛盾。此外,所提出的器件支柱和内部的 SP 仅占据纳米级区域,从而能够实现此类器件的高密度集成。通过在 ATLAS 中构建的数值模拟验证,与没有图案化衬底的相同场效应晶体管 (FET) 相比,所提出的器件具有更高的 BFOM,使其在未来的电源应用中具有很高的潜力。

方法

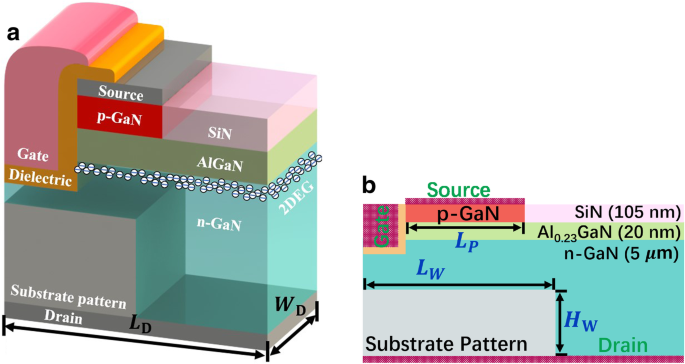

所提出的器件是在普通的 Al0.23GaN/GaN 晶片中生成的,具有高度集中的 n 型衬底作为漏电极,如图 1a 所示,其中氮化硅 (SiN)、AlGaN 和 GaN 层的厚度分别为 105 nm、20 nm 和 5 μm。具有 2 × 10 16 的 n 型 GaN 厘米 −3 兴奋剂n D 和具有 2 × 10 17 的 p 型 GaN 帽 厘米 −3 掺杂n A 分别设置为缓冲区和复合通道 [27, 28]。栅极旁边的沟道的另一个组件是薄的 AlGaN 层,它被引入用于诱导 2DEG,如图 1b 所示。以本文中的氧化铝(Al2O3)为例,在衬底上生长了一个SP。

<图片>

原理图a 3D 支柱结构和 b 带有所提出的 SP-VFET 的标记几何参数的横截面

因此整个器件可以通过标准工艺依次制造:(1)导电衬底和集成SP层的外延沉积,(2)SP图案的部分蚀刻,(3)n-的沉积和抛光。 GaN缓冲层,(4)AlGaN势垒和p-GaN帽层的沉积,以及(5)电极的制作和钝化。

植入的 ATLAS 模拟器通过来自具有 p-GaN 帽的增强型 HEMT 的实验数据进行校准 [29, 30]。设备的校准和其他规格如表 1 所示。其他配置可以在我们之前的工作中找到 [31]。位于 SP/GaN 界面的界面陷阱的类型和密度参考基于电容的实验测量 [32,33,34]。根据相应的简单二次拟合方程[35]确定AlGaN/GaN表面的极化电荷。

物理机制

在导通状态下,与没有 2-DEG 通道和 SP 的器件相比,所提出的具有衬底图案的垂直场效应晶体管 (SP-VFET) 由于 2-DEG 和更窄的垂直电流通道而具有高导电路径这会缩小电导,如图 2 所示。详细地说,由于高密度 2DEG 集中在 AlGaN/GaN 界面,可以维持电流的横向路径,这部分补偿了整个器件的电导。相比之下,没有2DEG通道的SP-VFET器件的电流传输能力将受到显着影响。

<图片>

a中正向电流的示意图 没有 SP 的设备,b 建议的具有短 SP 的 SP-VFET 和 c 长SP

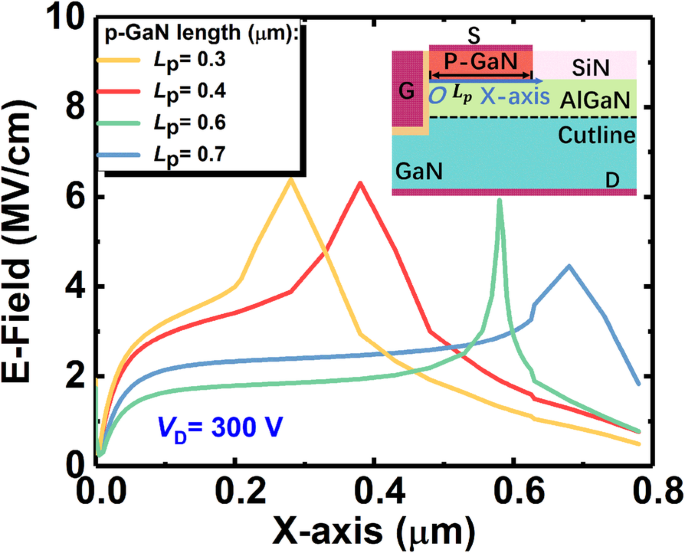

p-GaN 帽盖的长度不会显着影响电场(E 场)的浓度,直到长度超过 700 nm,p-GaN 几乎覆盖整个器件表面。如图 3 所示,沿 AlGaN/GaN 界面的电场分布在 p-GaN 的右角附近有一个峰值。峰的位置随着 p-GaN 长度的变化而变化,但保持相同的幅度。当 p-GaN 帽长于 600 nm 时,在图 3 中可以看到峰值的微小差异,因为长 p-GaN 帽使器件中的整个 E 场变平坦,从而扩大了器件的电阻2DEG 的耗尽。

<图片>

不同p-GaN长度下无SP器件沿AlGaN/GaN异质结的电场分布

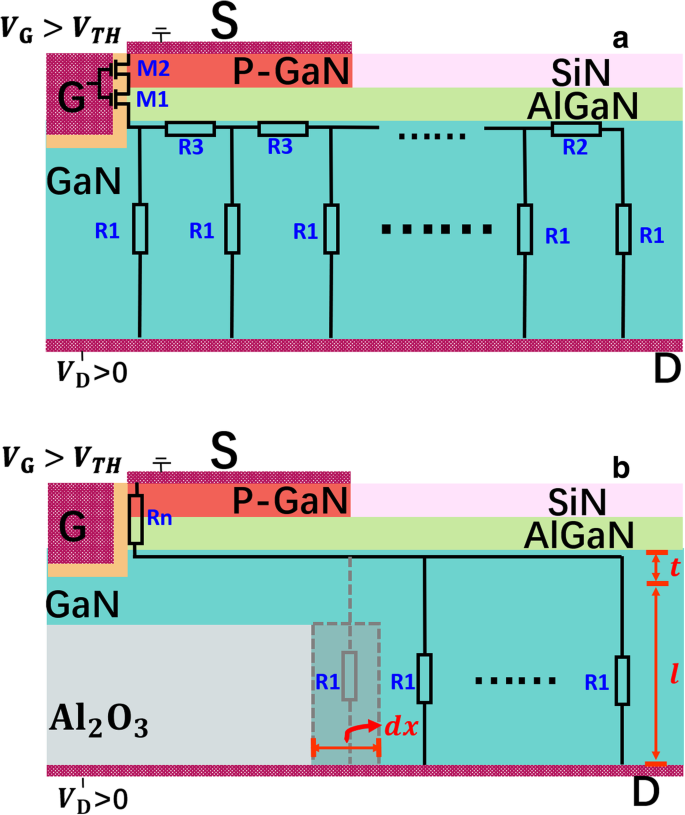

为了说明同时引入的 p-GaN、2-DEG 和 SP 的影响,可以构建导通状态传导模型,如图 4a 所示。 M 1 和 M 图2是具有分别在p-GaN和AlGaN中形成的导电沟道的类MIS晶体管。 R 图 1 表示体 GaN 中垂直电阻的无穷小部分。 R 2 和 R 图3分别表示部分耗尽和未部分耗尽的2-DEG通道的无穷小电阻部分。根据电阻定律,R 1、R 2、R 3 可以作为

$$ {R}_1=\frac{1}{n_1 q\mu}\bullet \frac{l}{dx\bullet {W}_D} $$$$ {R}_2=\frac{1}{n_2 q\mu}\bullet \frac{dx}{t\bullet {W}_D} $$$$ {R}_3=\frac{1}{n_3 q\mu}\bullet \frac{dx}{t\子弹{W}_D} $$其中 n 1、n 2 和 n 图3分别代表GaN、未耗尽2-DEG和耗尽2-DEG中的电浓度; q 是电子电荷,μ 是 GaN 中电子的迁移率; l 是垂直导电路径的长度,dx 是地平线上的无穷小长度; W D 是设备的宽度;和 t 是 2-DEG 的厚度。为方便起见,t 设置为 10 纳米 [7]。 p-GaN下耗尽的2-DEG的浓度n 3 等于未耗尽浓度 n 1 减去耗尽的 p-GaN [31] 中的总负电荷,其读数为

$$ {n}_3={n}_2-{n}_A{x}_D $$

a的示意图 不带 SP b 的状态模型 带SP的通态电阻网络模型

p-GaN 帽可被视为完全耗尽,因此 x D 等于 105 nm,即 p-GaN 的厚度。与 R 相比 1、R 2 和 R 3 远低于 R 1,因为它们的电子浓度更高,导电路径更短。因此,可以忽略 2-DEG 通道中的电阻。此外,当漏极电压较小且类 MIS 晶体管 M 1 和 M 2 工作在非饱和模型,导通电阻M 1 和 M 2 可视为可忽略的恒定电阻R n .为简化计算,垂直电流路径电导G的解析形式 v 的垂直电流路径的可得为

$$ {G}_v={\int}_0^{L_D}\frac{1}{R_1}={\int}_0^{L_D}{n}_1 q\mu \bullet \frac{dx\bullet { W}_D}{l} $$其中 L D是设备的长度。

因此,导通电阻R 开 可以获得,其内容为

$$ {R}_{on}=\frac{1}{G_v}+{R}_n=\frac{1}{n_1 q\mu}\bullet \frac{l}{L_D\bullet {W}_D }+{R}_n $$当 SP 存在时,如图 4b 所示,垂直导电路径已被部分阻断。因此,垂直电流路径的电导可以表示为

$$ {G}_v={\int}_{L_W}^{L_{\mathrm{D}}}\frac{1}{R_1}={\int}_{L_W}^{L_D}{n} _1 q\mu \bullet \frac{dx\bullet {W}_D}{l} $$其中 L W 是SP的长度。

因此,对应的R 开 可以表示为

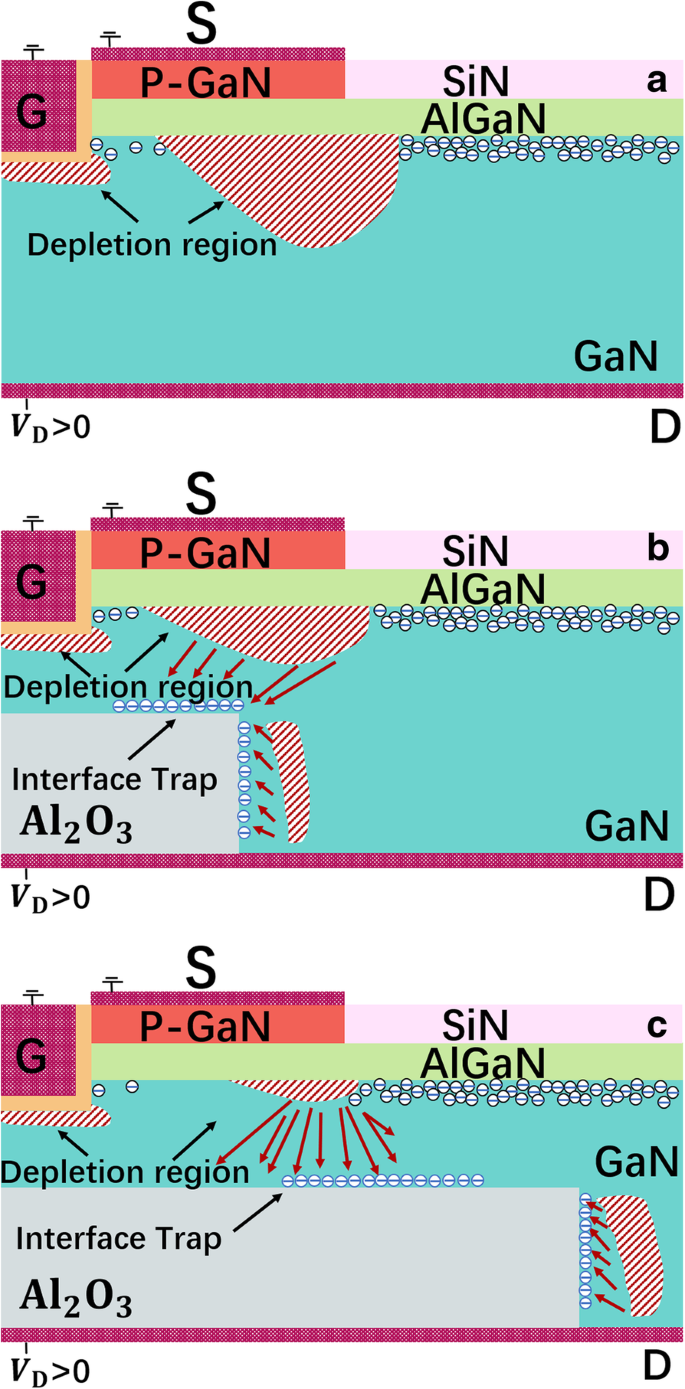

$$ {R}_{on}=\frac{1}{G_v}+{R}_n=\frac{1}{n_1 q\mu}\bullet \frac{l}{\left({L}_D -{L}_W\right)\bullet {W}_D}+{R}_n $$在关断状态下,由于类似电容器的功能和带负电荷的界面陷阱,SP 将有效地重新分配 p-GaN 帽下的电场,在 SP 周围产生具有更宽带隙的场集中,如图所示图 5. 这种电场重新分布缩小了 p-GaN 和栅极周围出现的耗尽区,从而缓解了 p-GaN 帽和栅极周围的高场集中,这将提高 SP-VFET 的 BV显着。另一方面,如上所述,SP会影响器件电导,使得SP引入的负电荷导致栅极附近势能的增加,这导致栅极附近2-DEG的减少。因此,可以通过改变SP的长度和高度来实现波动的BFOM。

<图片>

a中电场和耗尽区的分布示意图 没有 SP 的设备,b 建议的具有短 SP 的 SP-VFET 和 c 提出的具有长 SP 的 SP-VFET

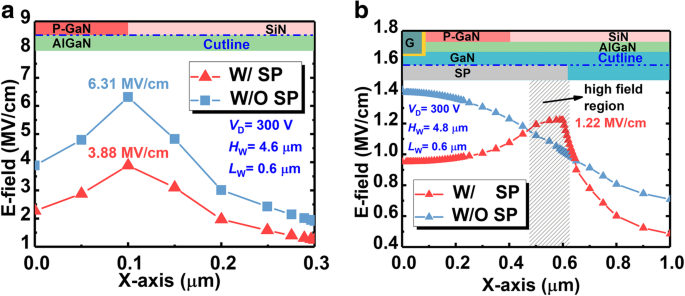

换句话说,SP 可以降低 p-GaN 角周围的 E 场峰值,同时吸引在 SP 上集中的 E 场,如图 6a、b 所示。然而,由于SP具有较高的临界电场,这种电场集中不会破坏器件,从而使SP-VFET表现出更高的BV。

<图片>

所提出的 SP-VFET 沿 a 界面的电场分布 p-GaN/AlGaN 和 b 氮化镓/SP

结果与讨论

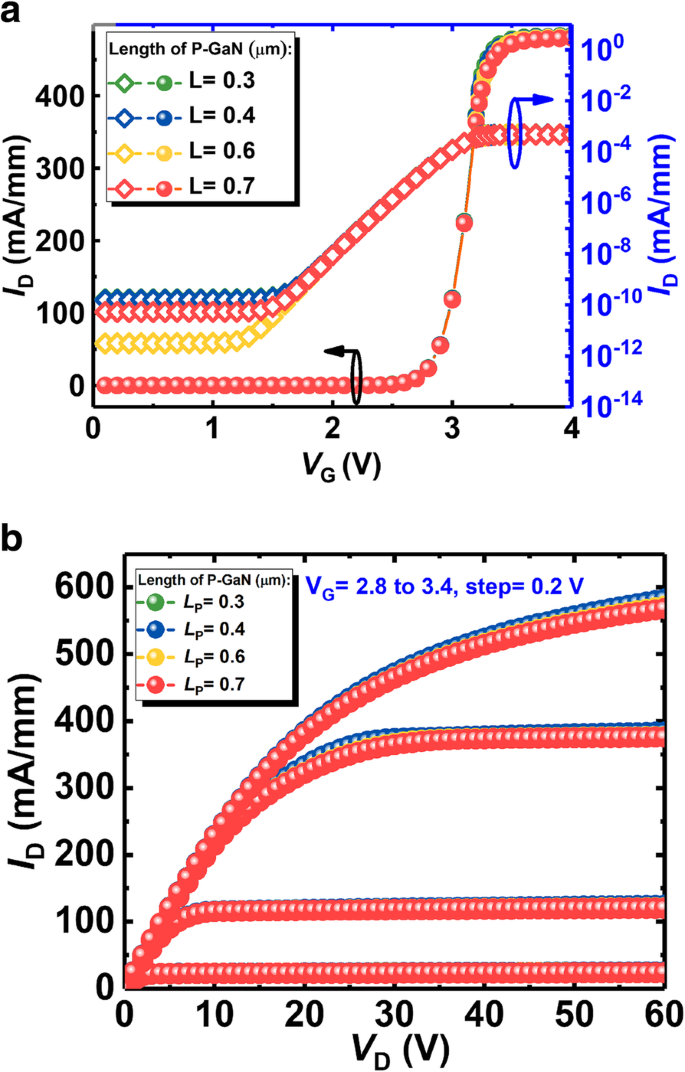

图 7a、b 分别显示了所提出的没有 SP 的设备的传输和输出曲线。由于 p-GaN 帽的长度不同,这些曲线在亚阈值和导通状态下相互重叠,表明 p-GaN 帽的长度不会影响没有 SP 的器件的电导。换句话说,虽然 p-GaN 帽会部分耗尽 2-DEG 从而影响 2-DEG 沟道的电阻,但剩余的 2-DEG 仍然具有较大的浓度 n 3 近似于未耗尽浓度 n 2,这是通过优化 p-GaN 帽中的 p 型浓度来实现的。此外,如前所述,与垂直路径中 n-GaN 的电阻相比,2-DEG 通道的电阻相当小。因此,转移曲线在图 7a、b 中相互重叠。然而,为了保护栅极免受高度集中的 E 场的影响,这种拥挤不应靠近栅极,这意味着 p-GaN 的长度不能太短。因此,除非另有说明,否则我们工作中 p-GaN 的最小长度为 400 nm。

<图片>

一 转移曲线和b 不带SP的器件在不同p-GaN帽长度下的输出曲线

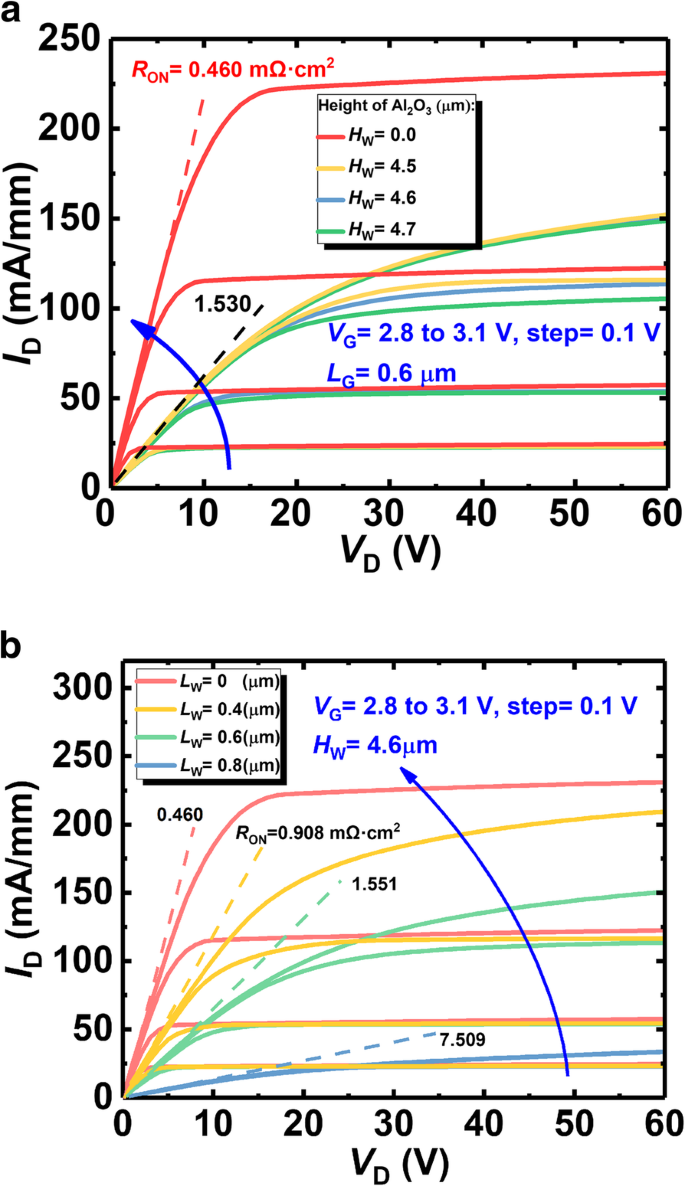

图 8 显示了建议的 SP-VFET 和没有 SP 的 VFET 的输出特性。可以看出,SP 确实通过缩小垂直传导通道来施加器件电阻。具体而言,当高度低于 4.7 μm 时,导通电阻与 SP 的高度无关,而显着取决于 SP 的长度,这与狭窄的垂直电流路径缩小电导的机制相匹配。前者的独立性是因为 2DEG 是主要的横向传导通道,在其中等高度内不会被 SP 削弱。但是,如果 SP 与 2-DEG 通道相邻,则在 SP 周围引入的负电荷将使能带变平,导致 2-DEG 浓度急剧下降。因此,2-DEG 的电阻增加,总导通电阻 R 开 相应增加。此外,后面的依赖性来自于前面提到的垂直通道中显着增加的阻力。此外,需要注意的是,高SP引起的2-DEG中的晶格缺陷限制了SP的高度。

<图片>

具有不同 a 的所提出的 SP-VFET 的输出曲线 SP 宽度和 b SP长度与无SP装置相比

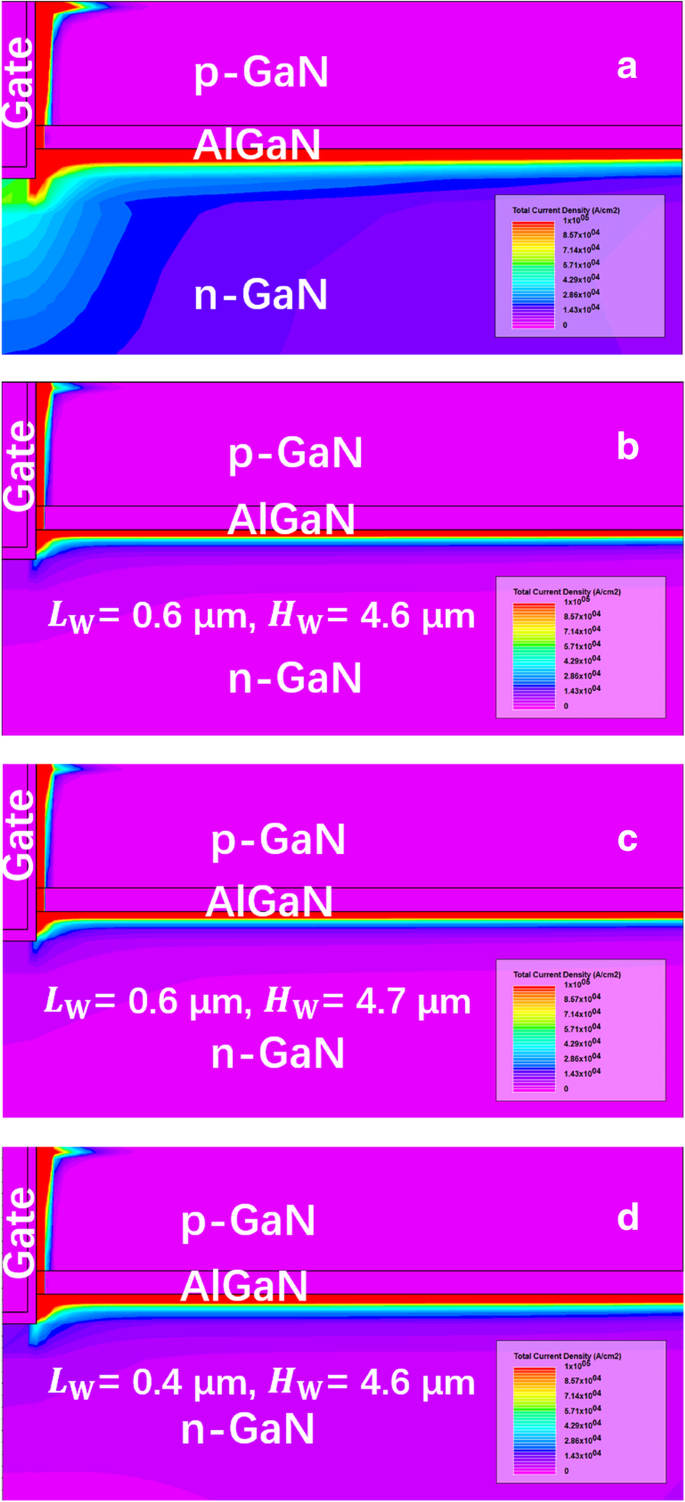

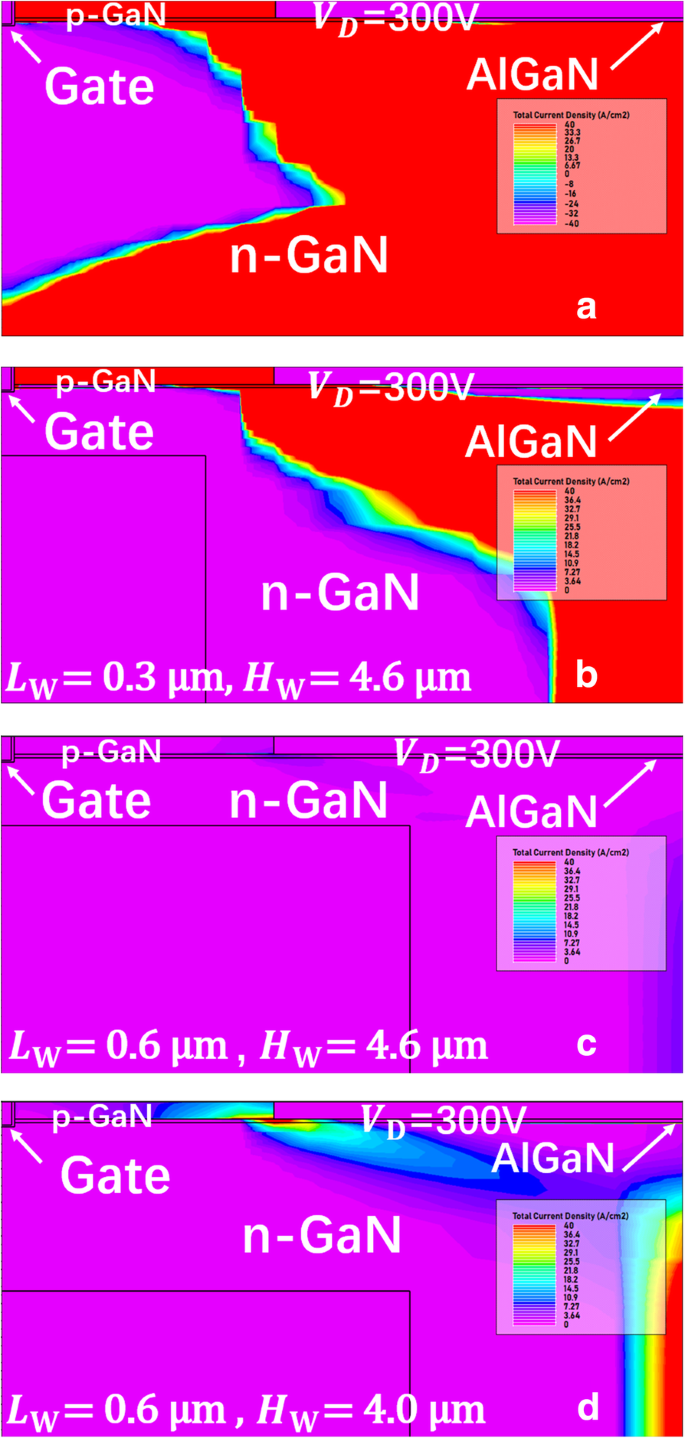

图 9 显示了有或没有 SP 的 VFET 器件的栅极周围电流密度分布的细节,其中没有 SP 的 VFET 具有更高的电流传输能力,这与图 8a 保持一致。相反,SP-VFET 通过缩小垂直沟道来缩小电流传导。同时,细节图清楚地表明,横向通道中的电流是由 2DEG 传输的,总电流密度随着 SP 高度的增加而略有变化,这也在机理部分得到了证明。结果表明,在中等高度范围内,侧向通道阻力不受SP的显着影响。

<图片>

a的电流密度 没有 SP 和 b 的设备 –d 提出的具有不同SP几何参数的SP-VFET

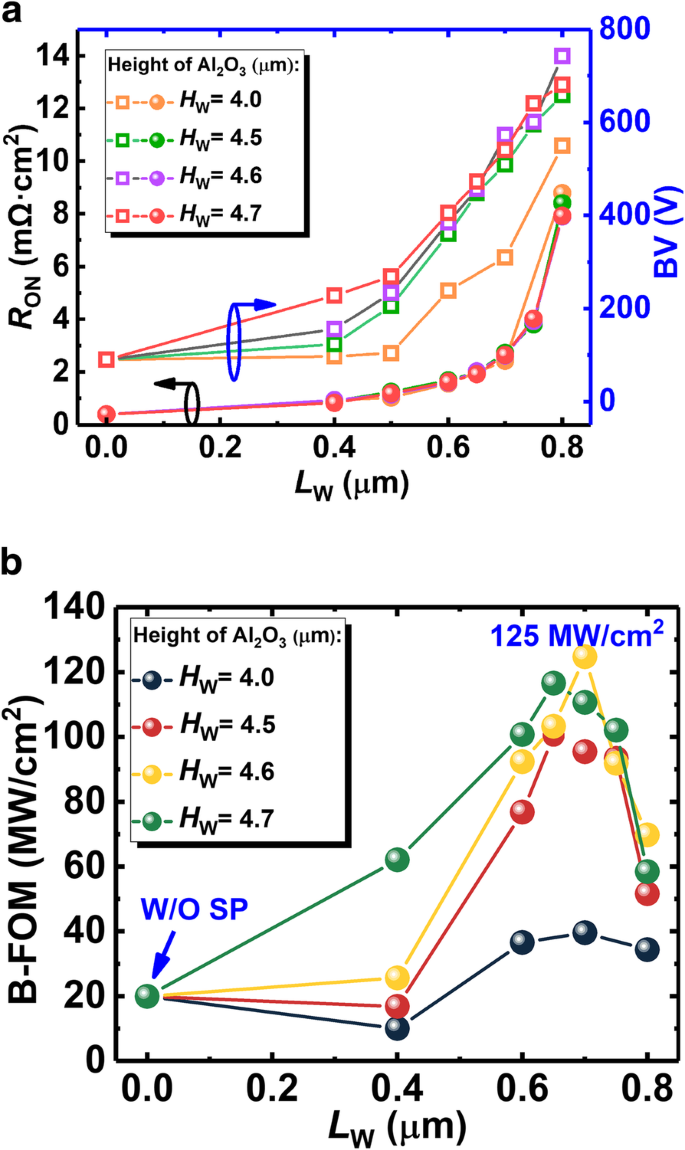

图 10a 显示了提取的通态电阻和相应的 BV。 SP-VFET 的电阻随着 SP 的延长而增加。尤其是电阻对SP长度的曲线呈现双曲线趋势,曲线的梯度随着SP长度的增加而增加。如前所述,R 开 随 SP 长度的不同而变化 L W 以双曲函数的形式,与仿真结果相匹配。此外,当高度低于 4.7 μm 时,不同 SP 高度的电阻曲线相互重叠,表明 2-DEG 通道是主要的横向导电路径,2-DEG 通道不受影响,如上所述。

<图片>

一 提取的导通电阻以及 BV 和 b 不同SP长度和宽度下所提出的SP-VFET的相应BFOM

图 10b 显示了 SP-VFET 的计算 BFOM。由于 BV 和导通电阻的增加率不同,所有器件的 BFOM 在 SP 长度超过 400 nm 后先增长后下降。峰值 BFOM 为 125 MW/cm 2 当长度达到 700 nm 和高度达到 4.6 μm 时实现。与没有 SP 的器件相比,所提出的 SP-VFET 在 BFOM 方面的性能提高了 6 倍以上。

由于 SP 周围带负电荷的界面陷阱抑制了 p-GaN 下的高电场,因此实现了这种改进。 SP 界面上被捕获的负电荷与 p-GaN 周围的耗尽区之间发生的相互作用形成了主要朝向被捕获电荷的新 E 场分布。根据高斯定律,电通量受所包围电荷的限制。因此,引入的电场将影响朝向其他地方的电通量。由于耗尽区的负电荷是 p-GaN 周围拥挤 E 场的主要来源,因此被俘获电荷引入的 E 场将起到抑制 p-GaN 周围 E 场拥挤的作用,因此, BV 增强。具体而言,当 SP 长度小于 400 nm 时,SP 引入的负电荷远离耗尽区。因此,耗尽区和捕获的负电荷之间形成的 E 场太小,无法影响 p-GaN 下的拥挤 E 场。因此,设备的 BV 略有增长。然而,由于 SP 长度大于 400 nm,由于 SP 界面上更多的被困负电荷以及耗尽区和被困负电荷之间的距离更短,耗尽区和被困负电荷之间的电场为增强,导致BV增长。

此外,由于 SP 引入的负电荷,SP 周围的区域被极大地耗尽。如图 11 所示,对于较长的 SP,由于耗尽区挤压到器件边缘,垂直漏电流路径的宽度变窄,这也阻止了漏电流,从而提高了 BV。因此,随着SP长度的增加,BV显着增加。

<图片>

a的漏电流密度 没有 SP 和 b 的设备 –d 提出的具有不同SP几何参数的SP-VFET

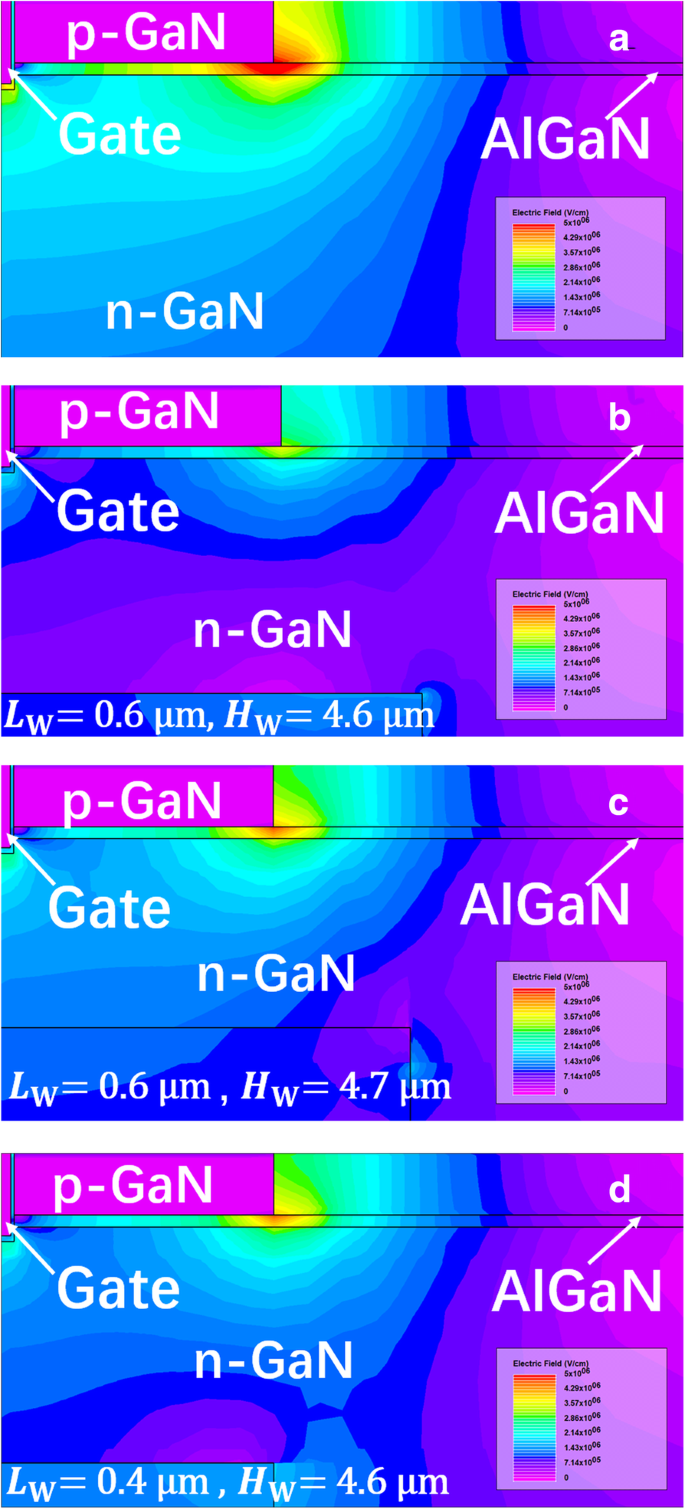

图 12 显示了当漏极电压为 300 V 时 SP-VFET 中的模拟 E 场分布,其中很明显 SP 诱导了其他新的 E 场集中点,这意味着 p-GaN 下的峰值 E 场区域被抑制.与不同SP高度器件中的电场分布相比,SP长度的增加抑制了电场的聚集,从而更有效地提高了BV。

<图片>

VFET 栅极周围的电场分布 a 与或 b –d 当漏极电压为 300 V 时,没有 SP

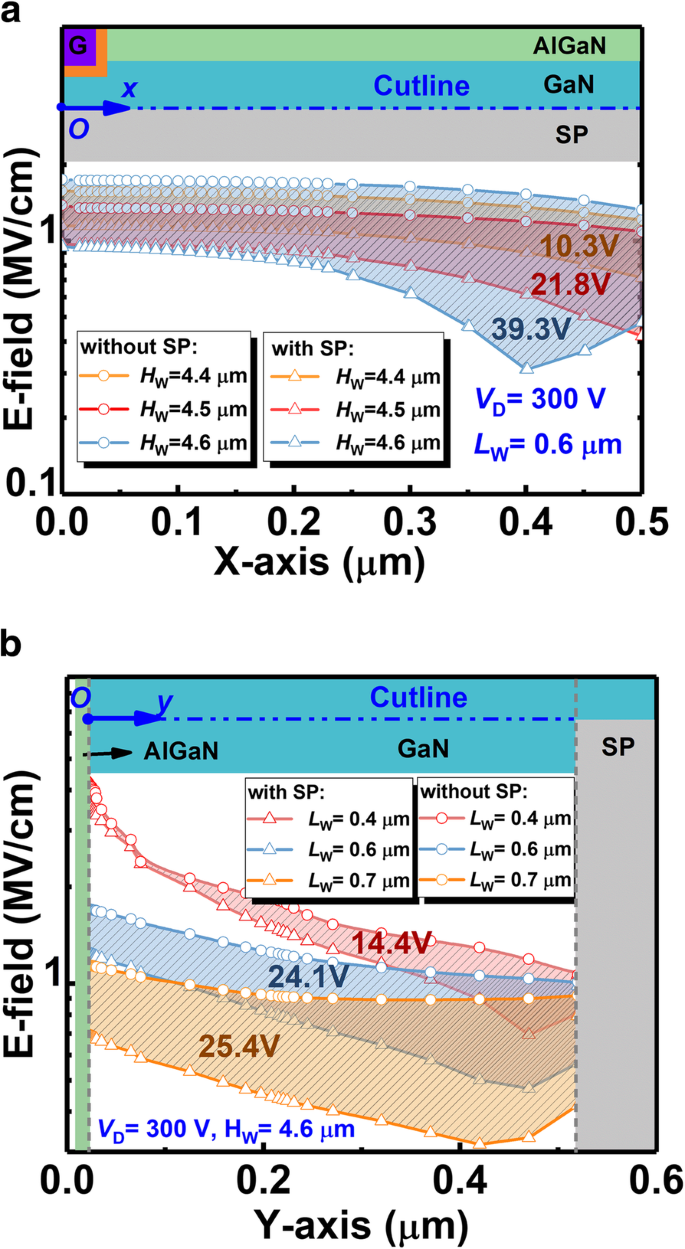

这种平坦的电场也可以在图 13 中明确观察到,其中绘制了沿 SP 的水平和垂直边缘的电场分布(参见切割线)。如多色图 12 所示,在图 13 中可以看出,更高和更长的 SP 在重建 p-GaN 下的 E 场方面起着越来越有效的作用,并且吸引 E 场集中在 SP 上边缘。这种重新分布抵消了易受攻击的 p-GaN 周围的电场。因此,提高了器件的 BV,提高了所提出的 SP-VFET 的 B-FOM。

<图片>

电场分布a 水平和 b 沿SP-VFET中SP边缘的切割线垂直提取

结论

在这项工作中,提出并研究了一种具有 2DEG 通道和衬底图案的新型增强型 GaN 垂直 FET (SP-VFET),以改善其 BFOM。通过使用 ATLAS 实施的实验校准模拟验证,SP 减轻了 p-GaN 下的 E 场峰值,同时,在具有更高临界 E 场的 SP 上吸引了新的 E 场浓度。因此,由于 2DEG 补偿,所提出的 SP-VFET 的 BV 得到提升,通态电阻适度增加。因此,当 SP 长度和高度分别为 700 nm 和 4.6 μm 时,SP-VFET 的 BFOM 比没有 SP 的器件的 BFOM 增强了六倍,这使得所提出的 SP-VFET 在高密度功率方面具有广阔的潜力整合。

缩写

- n 答:

-

p型GaN的掺杂浓度

- n :

-

n型GaN的掺杂浓度

- 2DEG:

-

二维电子气

- Al0.23GaN:

-

铝的摩尔分数为0.23的氮化铝镓

- Al2O3 :

-

氧化铝

- BFOM:

-

巴利加的品质因数

- D SP :

-

衬底图形的界面陷阱密度

- 电子字段:

-

电场

- E T :

-

导带与界面陷阱能级的差异

- FET:

-

场效应晶体管

- 氮化镓:

-

氮化镓

- HEMT:

-

高电子迁移率晶体管

- H :

-

闸门高度

- H :

-

基板图形高度

- L D :

-

设备长度

- L :

-

门的长度

- L P :

-

p-GaN帽的长度

- L W :

-

基板图形长度

- SiN:

-

氮化硅

- SP:

-

基板图案

- SP-VFET:

-

具有衬底图案的垂直场效应晶体管

- W D :

-

装置深度

- σ :

-

极化电荷

纳米材料

- 物联网之路

- 表面状态和铝摩尔分数对 AlGaN/GaN HEMT 中表面电位和 2DEG 的影响

- 垂直电场对 ML-GaS 的电子和光学各向异性特性的调制

- 接触非平衡等离子体对 Mn Х Fe3 − X О4 尖晶石结构和磁性能的影响

- 原位退火处理对基于 TIPS-并五苯的有机场效应晶体管的迁移率和形态的影响

- 控制合成不同形态的 BaYF5:Er3+、Yb3+ 以增强上转换发光

- 硅纳米线 FET 传感器中的光电导率、pH 灵敏度、噪声和通道长度效应

- 金属和金属氧化物纳米粒子的绿色合成及其对单细胞藻类莱茵衣藻的影响

- 形态和晶体结构对二氧化钛纳米管热导率的影响

- 采用后沉积蚀刻的浸渍法制备周期性聚苯乙烯纳米球阵列及其在提高 InGaN/GaN 光提取效率中的应用LED

- 基材对 LSP 耦合波长和强度的影响

- 表面活性剂对分层 SnO2 开花纳米花的微观结构及其气敏特性的影响