具有用于亚 10 nm 节点的新型夹层欧姆接触的高性能二维 InSe 场效应晶体管:理论研究

摘要

二维 (2D) InSe 基场效应晶体管 (FET) 在实验报告中显示出显着的载流子迁移率和高开关比。理论研究还预测,在弹道极限的亚 10 nm 节点处可以很好地保持高性能。然而,实验经验和理论计算都指出,实现高质量的欧姆已经成为高性能二维 FET 的主要限制因素。在这项工作中,我们为 InSe FET 提出了一种新的与铟的夹层欧姆接触,并基于 ab initio 方法从材料和器件的角度综合评估了其性能。材料特性表明,通过引入夹层结构,欧姆接触的所有基本问题,包括隧道势垒、肖特基势垒和有效掺杂都得到了很好的关注,并实现了出色的接触电阻。在器件性能水平上,研究了栅极长度为 7、5 和 3 nm 的器件。夹层接触器件的各项指标均远超《国际半导体技术路线图》(ITRS)的要求,与传统结构相比具有明显的提升。对于具有 7、5 和 3 nm 栅极长度的器件,分别实现了 69.4%、50% 和 49% 的最大电流提升。同时,实现了固有延迟的最大减少 20.4%、16.7% 和 18.9%。此外,还介绍了能量延迟积 (EDP) 与其他 2D FET 的基准测试。所有具有夹层欧姆接触的 InSe FET 均超过了 MoS2 FET 以及 ITRS 2024 的要求。最佳结果接近理想 BP FET 的上限,表明 InSe FET 夹层结构在下一代互补金属氧化物半导体中具有优越的优势( CMOS)技术。

介绍

二维 (2D) 半导体因其在下一代互补金属氧化物半导体 (CMOS) 技术中具有吸引力的应用而引起了电子设备的极大兴趣 [1, 2]。它们的超薄厚度和良好的介电性能可以提供出色的静电栅极控制,以抑制众所周知的短沟道效应 [3]。此外,由于很少有二维材料层通常具有光滑的表面且缺乏悬键,与传统半导体相比,二维材料的优越载流子迁移率可以在超薄体系统中得到很好的保持[4]。除了无间隙石墨烯,大多数合成的二维半导体,如过渡金属二硫属化物 (TMD)、黑磷 (BP) 和硒化铟 (InSe) 都具有非零带隙,并被证明适用于场效应晶体管 (FET)。 )。基于 TMD 的 FET 显示出高达 10 8 的高开关比 和短通道器件中的低漏电流,受益于大有效质量 [5]。由于~ 1000 cm 2 的高迁移率,基于 BP 的 FET 具有出色的电流和开关特性 [6] /V s 和各向异性输运特性 [7]。最近,InSe 被证明具有~ 2000 cm 2 的优越迁移率 /V s 在室温下 [8, 9] 和基于 InSe 的 FET 显示出 10 8 的高开关比 [10]。第一性原理计算还表明,InSe FET 可以很好地缩小到弹道极限 [11, 12] 中的亚 10 nm。然而,由于忽略了接触电阻和重掺杂的假设,在实际应用中接近理论极限仍然具有挑战性。事实上,由于仍然缺乏可靠的掺杂方法和高质量欧姆接触的途径,基于包括 InSe 在内的二维材料的 FET 通常是肖特基势垒 (SB) FET [13,14,15,16]。有源区的 SB 会产生很大的接触电阻,而低掺杂水平会进一步降低电流密度。以充分掺杂的有源区实现低接触电阻已成为二维材料基场效应管 (2D FET) 实现高性能的主要限制因素 [17,18,19]。

针对上述问题,我们提出了一种用于 InSe FET 的新型夹层欧姆接触。铟被选为电极金属,因为最近的实验和理论研究表明,铟可以成为 InSe FET 实现良好性能的有希望的候选者 [20,21,22]。我们根据 2013 年国际半导体技术路线图 (ITRS) [23] 的框架,从理论上评估了栅极长度为 7、5 和 3 nm 的器件的欧姆接触质量和性能。应该注意的是,尽管 ITRS 已被国际设备和系统路线图 (IRDS) [24] 所取代,但 ITRS2013 呈现出明显的晶体管缩放趋势,并且在最近的研究中仍被采用 [25, 26]。这份手稿安排如下:首先,研究夹层和常规(顶部)触点的电气特性。其次,评估导通电流和固有延迟等设备性能指标,并与 ITRS 的要求进行比较。最后,提出了功率延迟积与固有延迟的基准,以与其他基于二维材料的设备进行比较。

方法

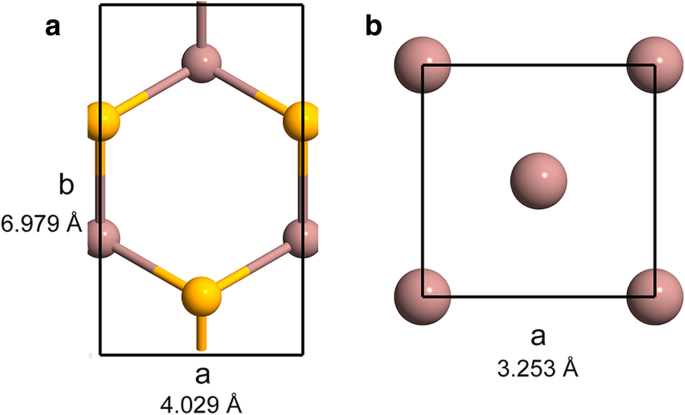

所有的原子结构都通过 VASP [27] 进行了优化;在所有计算过程中使用了 335 eV 的能量削减。 InSe 的晶胞在 SCAN 的 MetaGGA 框架下以 0.01 eV/Å 的应力标准松弛 [28]。金属铟的晶格参数是从化学和物理手册[29]中获得的。如图1所示,InSe的晶格常数为4.029 Å,与实验报告[30, 31]非常吻合。

<图片>

InSe 晶胞的顶视图 (a ) 和铟 (b ),分别

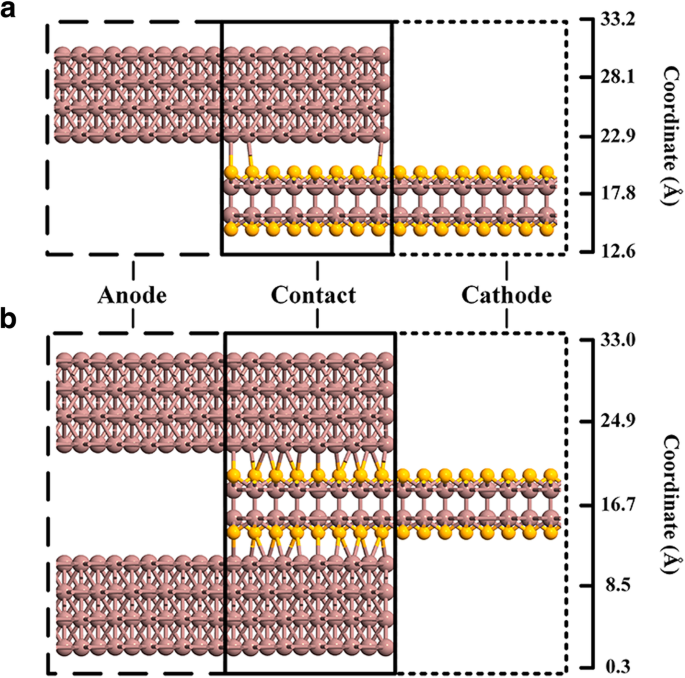

InSe 上的铟的初始结构分别由 InSe 和铟 (001) 表面的 4 × 1 × 1 和 5 × 2 × 1 晶胞构成。平均绝对应变为 1.32%,足以保留材料的固有特性。如图2a、b所示,夹层结构由铟/InSe/铟层构成,底面和顶面的铟与InSe中心呈镜像对称。两种混合结构都使用 optb88 的范德华 (vdW) 函数松弛,每个原子上的力标准低于 0.02 eV/Å [32, 33]。最终接触面积为 16.19 Å × 6.41 Å。然后通过如图 2a、b 所示的双探针装置评估欧姆接触的电阻。去除接触区外半导体不必要的电阻,阴极中的InSe重掺杂1×10 14 e/cm 2 适用于顶部和夹层触点。

<图片>

用于评估接触电阻的接触和相关双探针装置的原子结构。 一 , b 分别用于顶部和夹层触点。坐标表示原子在面外方向的位置

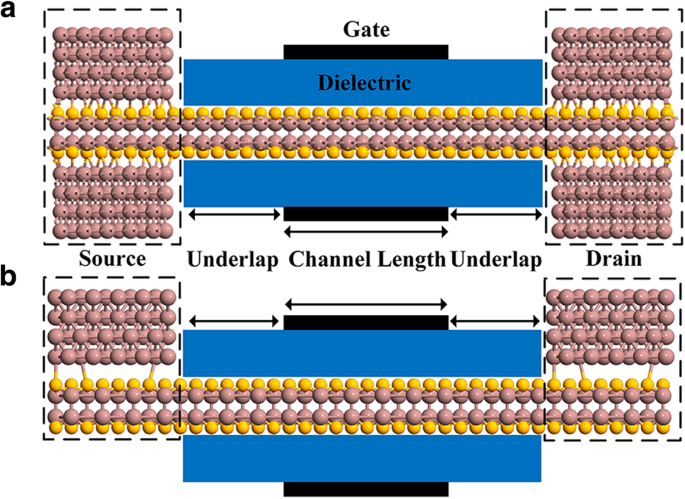

至于器件性能的评估,具有夹层和顶部欧姆接触的 InSe FET 的几何形状分别如图 3a、b 所示。所有设备和节点名称分别遵循 ITRS 和 IRDS 的要求。器件参数列于表 1 中。为了抑制带内隧道效应,在 3 nm 的栅极长度处应用了 1 nm 下重叠 (UL)。与欧姆接触建模相反,器件中没有任何部件是有意掺杂的。这些器件是通过沿传输方向合并源极、漏极和通道来构建的。沟道及其与有源区的两个界面用固定的源极和漏极额外松弛。所有模拟均基于非平衡格林函数 (NEGF) 理论,并由 QuantumATK 使用完全自洽计算 [34,35,36] 进行,该计算通常用于设计和研究亚 10 nm 节点的晶体管 [17 , 37,38,39]。采用双 zeta 极化基组,机械截止值为 90 Rydberg。 Monkhorst pack k点网格采样密度为8/Å −1 × 11/Å −1 × 180/Å −1 .为了效率,选择并行共轭梯度求解器作为泊松求解器。然后通过求解Landauer-Büttiker公式[40]可以得到所有器件的电流:

$$ I\left({V}_{\mathrm{Bias}}\right)=\frac{2e}{h}\int T\left(E,{V}_L,{V}_R\right)\ left[{f}_{\mathrm{R}}\left(E,{V}_R\right)-{f}_L\left(E,{V}_L\right)\right] dE $$ <图片>

InSe FET 的几何形状夹层 (a ) 和顶部 (b ) 联系人

其中,V 偏差是偏差,可以通过以下方式实现:V 偏差 =V R ‐ V L , T (E , V L , V R ) 是载波的传输系数,f R(E , V R ) 和 f L (E , V L )分别为阴极(漏极)和阳极(源极)的费米-狄拉克分布函数。

结果与讨论

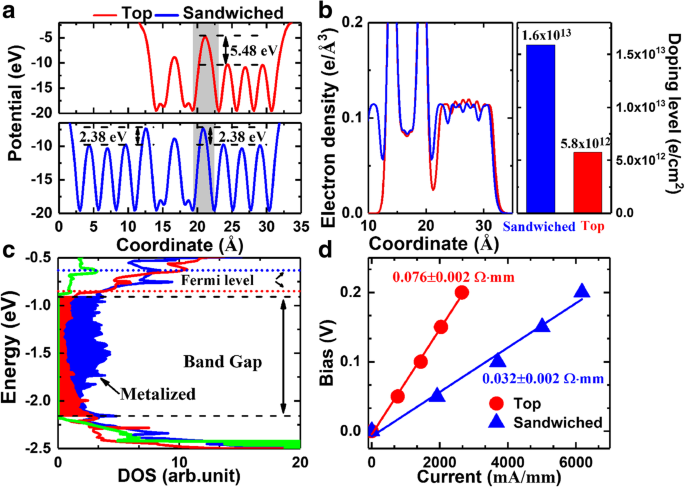

通常,与二维材料中的欧姆接触质量相关的三个关键因素 [18],即隧道势垒和源自 vdW 间隙的距离、电极和半导体之间的轨道重叠以及 SB 高度。首先,隧道势垒和距离由图 4a 中所示的有效电位描述。与顶部接触相比,夹层接触的引入不仅在底部提供了额外的传输路径,而且使隧道势垒从 5.48 eV 降低到 2.38 eV,导致降低了 56.6%。同时,界面距离也略有降低,为 0.66 Å,表明隧道势垒的宽度也有所减小。其次,可以从图 4b 中的价电荷分布评估轨道重叠。可以注意到,与顶部接触相比,夹层接触在界面区域拥有更多的价电子,表明铟和 InSe 之间的轨道重叠更强。该特性还有助于将掺杂效应引入 InSe 中,可以使用马利肯布居计算多余电子数。我们分别提取了夹层结构和顶部接触结构的 InSe 中的电子总数。然后可以通过将电子数除以接触区域的面积来获得掺杂水平,因为隔离的 InSe 的净电荷应始终为零。如图 4b 的右侧面板所示,夹层接触产生了 1.6 × 10 13 的非常高的掺杂水平 e/cm 2 ,比顶部接触高出近 2.8 倍。如此高的水平已经接近 2D 隧道 FET 模拟中的假设,该假设通常声称比金属氧化物半导体 FET 更重的掺杂水平。第三,InSe 在原始、夹层和顶部接触结构中的态密度(DOS)如图 4c 所示。界面区域的铟和 InSe 之间的轨道重叠使 InSe 的带隙金属化,并将其夹在中间导致更高的能级。由于带隙中的金属化状态提供了额外的隧道通道,因此该特征极大地增强了通过界面区域的 vdW 隧道势垒的载流子注入。此外,费米能级固定在导带最小值之上,导致顶部和夹层触点的能量简并分别为~ 0.07 和 0.27 eV。因此,完全消除了铟和 InSe 之间的 SB。第四,根据从双探针器件获得的偏置电流曲线计算欧姆接触电阻,所有结果如图 4d 所示。由于线性演化,我们可以注意到两个接触都是欧姆的。在理论层面,即忽略表面粗糙度、界面杂质等,夹层结构导致接触值非常低,为 0.032 ± 0.002 Ω mm,使顶部接触电阻降低了一半以上。基于上述讨论,有趣的是注意到双倍的接触区域总是会导致欧姆接触的两倍以上的改善。由于最近实验证实与铟的顶部接触可有效提高基于 InSe 的器件性能 [21, 22],因此夹层结构可以成为一种有吸引力的 InSe FET 欧姆接触解决方案。

<图片>

一 垂直于传输方向的有效电位。坐标对应于原子的位置,并在图 1 中定义。暗区对应于 vdW 间隙。 b 垂直于传输方向的平面平均电子分布。右侧面板是掺杂水平。坐标对应于原子的位置,并在图 1 中定义。c InSe 的 DOS。绿色对应于原始 InSe。 d 两个探针设备的电流相关偏置。所有红色和蓝色分别对应于顶部和夹层触点

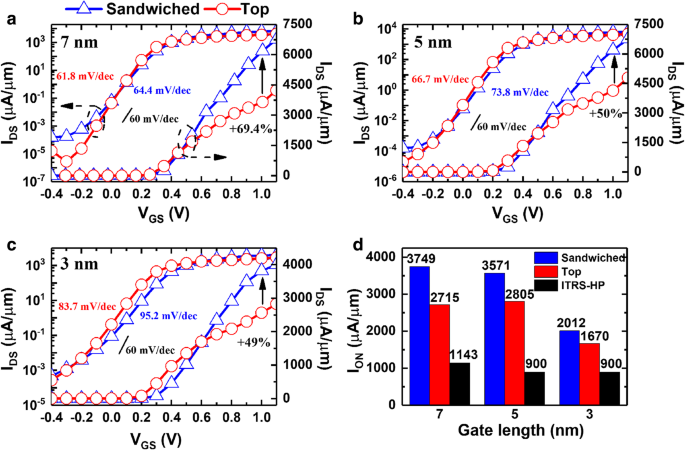

然后对器件性能进行评估,InSe FET在2019、2021和2024节点的传输特性如图5所示。可以观察到所有节点的亚阈值摆幅(SS)均低于100 mV/dec和 SS 在 2019 节点显示出接近理想的开关特性,顶部和夹层接触器件分别为 61.8 和 64.4 mV/dec,表明 InSe FET 具有出色的静电控制。此外,与顶级器件相比,夹层接触器件导致 IDS 的显着改善,分别在 2019、2021 和 2024 节点实现了 69.4%、50% 和 49% 的最大增长。此外,根据 ITRS 对高性能 (HP) 的要求,提取了 ION。如图 5d 所示,所有系统的 ION 都远高于 HP 要求。与顶级接触设备相比,夹心系统在 2019、2021 和 2024 节点仍分别呈现 38.2%、27.3% 和 20.5% 的提升。

<图片>

InSe FET 在节点处的传输特性。 一 2019,b 2021 和 c 分别为 2024 个节点。 d ION遵循ITRS HP要求的比较

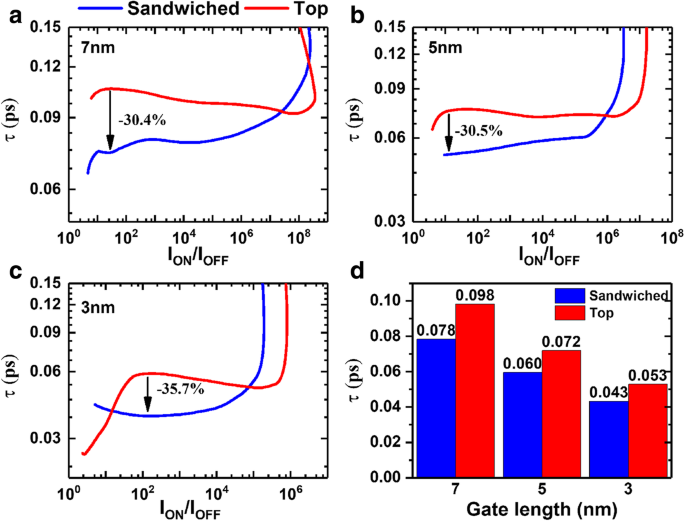

FET 的另一个基本指标是固有延迟 (τ),它表示逻辑电路中开关速度的上限。 τ 由 τ 获得 =(QON − QOFF)/ION,其中 QON 和 QOFF 分别是开和关状态下的电荷。对于 2019、2021 和 2024 节点,开和关状态分别限制在 |VDS|=0.68、0.64 和 0.64 V。作为开关比函数的本征延迟如图 6 所示。尽管在低栅极电压下的隧穿产生大延迟的非单调演化 [41],所有延迟都低于 0.15 ps,并且比ITRS 要求 0.44-0.46 ps。此外,夹层接触式器件在 ION/IOFF ≤ 10 7 区域的降低超过 30% , 10 6 , 10 5 分别用于 2019、2021 和 2024 节点。在图 6d 所示的 HP 要求的基础上,夹层接触器件仍然可以将 2019、2021 和 2024 节点的开关速度分别提高 20.4%、16.7% 和 18.9%。

<图片>

作为节点开关比函数的固有延迟。 一 2019,b 2021 和 c 分别为 2024 个节点。 d 遵循 ITRS 的 HP 要求的固有延迟比较

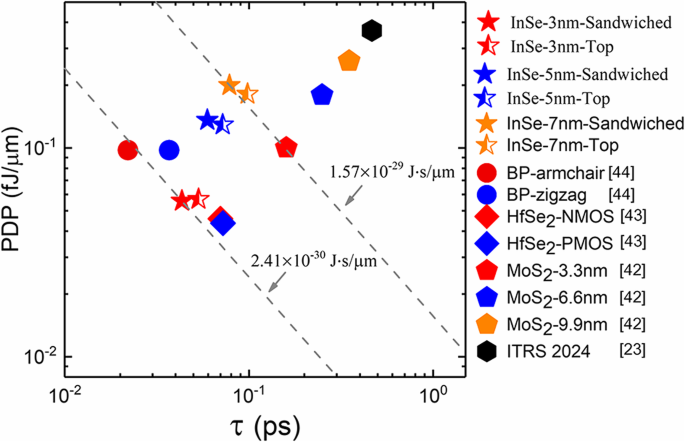

为了更直观地评估器件性能,提取了功率延迟乘积 (PDP) 与固有延迟的关系。 PDP 对应于单个开关事件中的功耗,由 PDP =(QON − QOFF)VDS 定义,所有参数均来自 ITRS 的 HP 要求。结果和与其他2D FET的比较如图7所示。首先,所有2D FET都是根据实验报告中已经初步验证为晶体管的规则来选择的,这对CMOS技术更进了一步。其次,除了 InSe 和 MoS2 [42],所有其他器件都在有源区进行了重掺杂并忽略了欧姆接触电阻 [43, 44],因此结果对应于性能的上限。可以看出,所有能量延迟产品 (EDP) 都低于 ITRS 2024 的要求,这表明 2D FET 具有吸引力的未来。 EDP 的最大值属于 9.9 nm 处的 MoS2 FET,最好的是来自 BP FET。对于 InSe FET,夹层接触式器件在所有节点上的性能始终优于顶部接触式器件。夹层接触器件的最高 EDP 位于 7 nm 的栅极长度(2019 节点)并且超过所有 MoS2 FET。最低的是 3 nm 的栅极长度(2024 节点),甚至在扶手椅方向上接近 BP FET 的上限,这是众所周知的出色传输特性。因此,InSe FET的EDP表明夹层接触器件在二维FET中表现出足够的竞争力。

<图片>

功率延迟乘积与由 InSe 和其他 2D FET 组成的固有延迟。灰色虚线指南对应于特定的 EDP

结论

在这项工作中,为 InSe FET 提出了一种新的与铟的夹层欧姆接触。夹层欧姆接触不仅使接触面积增加了一倍,而且还提高了两倍以上的接触质量,从而产生了极好的接触电阻。在栅极长度 7、5 和 3 nm 的器件性能水平上,与传统顶部接触器件相比,具有夹层欧姆接触的 InSe FET 具有普遍的性能提升。在ITRS的HP要求下,导通电流和固有延迟分别提高了38.2~20.5%和20.4~16.7%。 EDP 与其他 2D FET 的基准测试还表明,具有夹层欧姆接触的 InSe FET 比其他 2D FET 更具优势。我们的研究为高性能 InSe FET 提供了一条新途径。

数据和材料的可用性

当前研究中使用和/或分析的数据集可根据合理要求向相应作者索取。

缩写

- 二维:

-

二维

- CMOS:

-

互补金属氧化物半导体

- TMD:

-

过渡金属二硫属化物

- BP:

-

黑磷

- InSe:

-

硒化铟

- FET:

-

场效应晶体管

- SB:

-

肖特基势垒

- 二维 FET:

-

基于二维材料的场效应管

- ITRS:

-

国际半导体技术路线图

- vdW:

-

范德华

- UL:

-

重叠

- NEGF:

-

非平衡格林函数

- DOS:

-

态密度

- SS:

-

亚阈值摆动

- 惠普:

-

高性能

- τ:

-

固有延迟

- PDP:

-

功率延迟产品

- EDP:

-

能量延迟产品

纳米材料

- 10nm 芯片的空气隔离物

- Nexam 为戴铂提供性能增强的 Nexamite 用于高性能 PET 泡沫

- 来自废棉手套的具有分级纳米结构的活性炭纤维作为超级电容器的高性能电极

- 具有低电阻 Au 欧姆接触的多层 SnSe 纳米片场效应晶体管

- 新型纳米粒子增强蠕虫状胶束系统的研究

- 粗糙表面法向载荷下接触面积的演变:从原子尺度到宏观尺度

- 用于薄膜晶体管的氧化铟纳米膜的原子层沉积

- 用于高性能超级电容器的二维 VO2 介孔微阵列

- 具有 HfO2 缺陷控制层的单壁碳纳米管主导的微米宽条纹图案化铁电场效应晶体管

- 一种用于光伏器件的具有抗反射和超疏水特性的新型纳米锥簇微结构

- 一种用于高灵敏度检测阿特拉津的新型磁弹性纳米生物传感器

- 用碳纳米管和石墨烯改性的 FeF3·0.33H2O 高性能正极材料,用于锂离子电池