通过等离子体增强原子层沉积原位形成 SiO2 中间层的 HfO2/Ge 叠层的界面、电学和能带对准特性

摘要

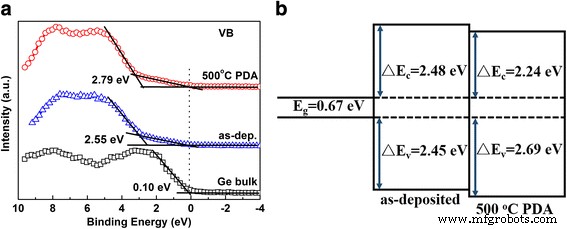

通过等离子体增强原子层沉积 (PEALD) 将原位形成的 SiO2 作为中间层引入 Ge 衬底上的 HfO2 栅极电介质中。已经很好地研究了 Ge 上 HfO2/SiO2 高 k 栅极电介质堆叠的界面、电学和能带对准特性。已经证明在原位 PEALD SiO2 沉积过程中在 Ge 表面形成 Si-O-Ge 中间层。该夹层在退火过程中表现出极好的热稳定性,而没有明显的 Hf 硅酸盐形成。此外,它还可以抑制GeO2的降解。电学测量表明,电容等效厚度为 1.53 nm,漏电流密度为 2.1 × 10 -3 A/cm 2 在栅极偏压 Vfb + 1 V 下,退火样品获得了。发现有和没有 PDA 的 HfO2/SiO2/Ge 界面的导(价)带偏移分别为 2.24 (2.69) 和 2.48 (2.45) eV。这些结果表明,原位 PEALD SiO2 可能是实现高质量 Ge 基晶体管器件的有前途的界面控制层。此外,可以证明PEALD是一种比MOCVD更强大的超薄界面控制层沉积技术。

背景

随着金属氧化物半导体场效应晶体管 (MOSFET) 的不断缩小,硅基 MOSFET 正在接近其物理和技术限制。诸如锗 (Ge) [1, 2] 和 III-V 族材料 [3-5] 等替代沟道材料最近引起了高性能逻辑器件应用的极大兴趣。其中,Ge因其固有的较高空穴载流子迁移率而具有取代硅作为MOSFET沟道材料的潜力[6]。然而,在 Ge 衬底上直接沉积高 k 栅极电介质通常会导致高界面陷阱密度 (Dit) 以及在 Ge 和高 k 电介质层之间形成不需要的界面层 [7]。因此,要实现高速、低功耗的Ge基MOSFET,实现高质量的高k是非常重要的。 /Ge 界面。幸运的是,已经报道了很多提高高k/Ge界面质量的方法[8],例如引入SiO2[9]、Si[10]、GeO2[11]、Al2O3[12、13] , GeOxNy [14, 15] 和稀土氧化物 [16, 17] 作为 Ge 衬底和高 k 之间的界面控制层 栅极电介质。特别是GeO2/Ge结构具有优异的界面特性,极低的界面态密度(Dit)小于1 × 10 11 cm −2 eV −1 可以实现[18]。但是,GeO2 会在 425°C 以上分解,并且可溶于水。因此,Ge-MOS 电容器 (MOSCAP) [6] 总是会出现不可接受的 Dit。幸运的是,Kita 等人。据报道,GeO2 上的覆盖层可以抑制 GeO2 的降解;然而,帽层材料的选择应该非常关键[19-21]。例如,Si 或 Y2O3 比 HfO2 更有效地阻止 Ge-O 解吸。这些结果表明高 k 材料或界面控制层选择对抑制 GeO2 降解的重要性。中岛等人。据报道,通过物理气相沉积 (PVD) 形成的非常薄的 SiO2/GeO2 双层是一种很有前途的 Ge 钝化夹层,Dit 为 4 × 10 11 厘米 -2 eV −1 是在中间差距附近实现的 [22, 23]。李等人。通过金属有机化学气相沉积 (MOCVD) 在 Ge 上引入 SiO2 夹层,SiO2 夹层可以有效抑制 HfO2 生长和随后的沉积后退火过程中的 Ge 外扩散 [9]。因此,SiO2 应该是 Ge 衬底的一个很好的界面控制层。但是,与 PVD 和 MOCVD 相比,PEALD 可以提供更均匀的钝化层,尤其是对于超薄厚度。因此,PEALD形成的SiO2可能是实现高性能Ge基晶体管器件的有前景的界面控制层。

在此,我们将原位 PEALD 形成的 SiO2 作为界面层引入 HfO2/Ge 堆栈中。已经仔细研究了 n 型 Ge 衬底上的 ALD HfO2 膜的界面、电学和能带对准特性。 SiO2首先通过PEALD沉积在Ge衬底上作为界面控制层。然后,通过热 ALD 模式原位沉积 HfO2 栅极电介质。对 Ge 上的 HfO2/SiO2 高 k 栅极电介质堆叠在 N2 中在 500°C 下进行 60 秒的沉积后退火 (PDA)。 X 射线光电子能谱分析表明,在 PEALD SiO2 沉积过程中,在 Ge 表面形成了 Si-O-Ge 夹层和 GeO2 层。这种 Si-O-Ge 夹层不仅表现出极好的热稳定性,而且可以抑制 GeO2 的热分解。因此,HfO2/Si-O-Ge/GeO2/Ge 叠层实现了良好的电学性能。与 MOCVD SiO2 夹层相比,原位 PEALD SiO2 表现出大大改善的电性能。因此,PEALD在MOSFET制造领域是比MOCVD强大得多的技术,尤其是在超薄界面控制层沉积方面。

方法

使用电阻率为 0.2-0.3 Ω∙cm 的 N 型 Sb 掺杂 Ge (100) 作为衬底。首先分别通过在丙酮、乙醇、异丙醇和去离子水中超声处理 5 分钟来清洁基材。然后,使用稀释的 HBr 溶液(H2O/HBr =3:1)蚀刻表面天然氧化物 5 分钟。湿法化学清洗后,用去离子水冲洗基板并在纯 N2 中吹干。随后,将底物立即转移到 PEALD (Picosun SUNALE TM R-200) 室。在高k之前 HfO2 膜沉积,10 次循环 SiO2 膜在 250°C 下通过 PEALD 作为中间层沉积,其中一个循环包括 1 秒 Si 源注入、10 秒 N2 吹扫、13.5 秒氧化剂注入和 4 秒 N2 吹扫。 Tris-(二甲氨基)-硅烷 (TDMAS) 和 O2 等离子体分别用作 Si 前驱体和氧化剂用于 SiO2 沉积。 TDMAS 保持在室温下。纯 O2 气体 (99.999%) 用作 O2 等离子体源。等离子体功率和 O2 气体流速分别为 2500 W 和 160 sccm。 PEALD SiO2 的生长速率通过非原位光谱椭偏法确定为 ~0.7 Å/循环。然后通过热 ALD 在 250°C 下原位沉积约 4 nm 厚的 HfO2 膜 40 个循环,其中一个循环包括 0.1 秒 Hf 源添加、4 秒 N2 吹扫、0.1 秒 H2O 给药和 4 秒 N2 吹扫。 Tetrakis-(乙基甲基氨基)-铪(TEMAH)和H2O分别用作Hf前体和氧化剂用于HfO2沉积。 TEMAH 在 150°C 下蒸发,H2O 保持在室温。纯 N2 (99.999%) 用作载气和吹扫气。 PDA 在 N2 环境中在 500°C 和大气压下使用快速热退火进行 60 秒。

通过使用标准 Al Kα (1486.7 eV) X 射线源的非原位 X 射线光电子能谱(XPS,Thermo Fisher K-Alpha)研究膜的界面结构和化学键合。 XPS 光谱以 90° 的起飞角收集。使用 29.4 eV 的 Ge 3d5/2 峰校准结合能标度。此外,XPS 光谱在智能型背景减法后拟合了高斯-洛伦兹 (G-L) 函数。面积1.55 × 10 −4 的Pt顶电极 厘米 2 使用荫罩通过溅射方法沉积在 HfO2 薄膜的表面上进行电测量。电容-电压(C-V)和漏电流密度-电压(J-V)特性由带探针平台的Keithley 4200半导体分析仪系统(Cascade Summit 12000B-M)测量。

结果与讨论

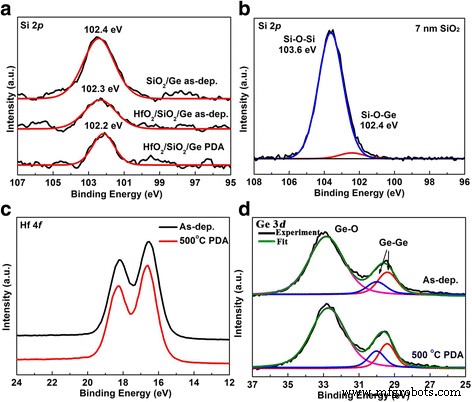

对于 Ge 上的薄 PEALD SiO2(~0.7 nm),Si 2p 在 102.4 eV 处表现出一个峰值,对应于 Si-O 键(图 1a),它小于理想 SiO2 的结合能 [24]。在 PEALD 工艺期间,低氧化硅 (SiOx) 沉积和 Ge 表面上的 Si-O-Ge 形成都会导致 Si 2p 转变为较低的能量。因此,还进行了 Ge 上厚 PEALD (~7 nm) 的 Si 2p 光谱。可以发现它在 103.6 eV 处显示出一个主峰,对应于理想的 SiO2 键合,如图 1b 所示。所以,这里PEALD沉积的氧化硅是理想的SiO2。然而,除了强的 Si-O-Si 峰外,还有一个位于 ~102.4 eV 的弱峰,这应该对应于 Ge 表面上的 Si-O-Ge 键合。因此,可以得出结论,在最初的 PEALD SiO2 生长中,在 Ge 表面形成了 Si-O-Ge。在原位 4 nm HfO2 沉积后,Si 2p 峰强度降低,没有明显的化学位移 (102.3 eV),如图 1a 所示。此外,Si 2p 在 N2 中 500°C PDA 后,峰也没有表现出明显的化学位移 (102.2 eV),表明 HfO2 沉积和 PDA 过程中 HfO2/SiO2 界面具有良好的热稳定性。在沉积的 HfO2/SiO2 栅叠层的 Hf 4f 光谱中(图 1c),16.5 和 18.2 eV 的双峰可以分配给 HfO2 的 Hf 4f7/2 和 Hf 4f5/2 峰,自旋轨道分裂能量为 1.7 eV,与 HfO2 的文献值一致 [25]。在 500 °C PDA 后,Hf 4f 光谱没有明显变化,只有 0.1 eV 向更高能量转移。这意味着在 PDA 过程中没有形成明显的 Hf-硅酸盐。在图 1d 中,沉积态样品的 Ge 3d 光谱在 29.4 和 30.0 eV 处显示了双峰,这可以归为 Ge 衬底的 Ge 3d5/2 和 Ge 3d3/2 峰,自旋轨道分裂能量为0.6 eV。除了 Ge 衬底的信号外,Ge-O 键合在 32.7 eV 处有一个巨大的峰值。 Ge-O 峰应该是由 Ge-O-Si 和 GeO2 的形成引起的。 GeO2 层是在 PEALD SiO2 沉积过程中通过表面氧等离子体氧化形成的。因此,这里真正制造的结构是 HfO2/Si-O-Ge/GeO2/Ge 叠层。此外,Ge 3d 光谱在 500°C PDA 处理后没有显示出明显的变化,表明 HfO2/Si-O-Ge/GeO2/Ge 叠层的热稳定性没有 GeO2 降解。 Kita 等人报道了这一点。 GeO2 上的一些覆盖层可以抑制 GeO2 分解,例如 Si 或 La2O3 [19]。因此,PEALD 在这里诱导 Si-O-Ge 中间层也可以抑制 GeO2 分解。基于以上 XPS 分析,可以得出结论,在 Ge 表面形成了超薄的 Si-O-Ge 中间层。此外,该夹层表现出极好的热稳定性,不会形成Hf-硅酸盐,还可以抑制GeO2的降解。

SiO2/Ge 和 HfO2/SiO2/Ge 结构的 XPS 光谱。 一 SiO2 的 Si 2p 光谱,在 Ge 上沉积和退火的 HfO2/SiO2。 b Ge 上厚 SiO2 (7 nm) 的 Si 2p 光谱。 c, d 沉积态和退火态 HfO2/SiO2/Ge 结构的 Hf 4f 和 Ge 3d 光谱

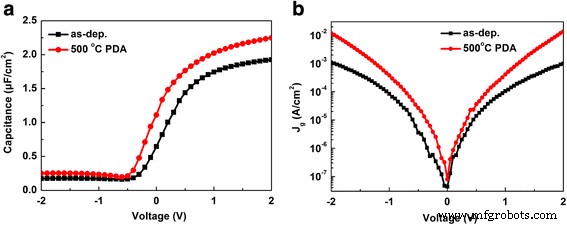

图 2a 绘制了 PDA 前后 HfO2/SiO2 栅极堆叠在 Ge 上的高频 (1 MHz) C-V 曲线。可以发现,平带电压 (V fb) PDA 前后 HfO2/SiO2/Ge 的值分别为 0.42 和 0.27 V。计算出的理想 V fb 值为 0.55 V。略为负的 V fb 位移表示正固定电荷,这可能是由电介质中的氧空位引起的 [26, 27]。在惰性气氛退火过程中,可能会引起更多的氧空位,导致V fb 转移。许多报道的文献已经证明,退火过程中GeO2的降解会导致正V fb 转移。 Ge-O 的解吸过程被认为会产生额外的负电荷 [28, 29]。因此,也可以得出结论,Ge-O-Si 夹层从 V 抑制了 GeO2 分解 fb 转移。累积电容明显从原来的 1.92 增加到 2.25 μF/cm 2 在PDA之后。可以使用 ε0εrA/Cacc [30] 从 C-V 曲线的累积电容计算 MOS 电容器的相应电容等效厚度 (CET) 值。因此,与 1.80 nm 的沉积样品相比,PDA 后获得的 CET 更小,为 1.53 nm。这可以归因于PDA工艺后可以获得更致密和更薄的高k层。图 2b 显示了 PDA 前后 Ge 上 HfO2/SiO2 薄膜的漏电流特性。在 V 的偏置电压下 fb + 1 V,漏电流密度为2.1 × 10 −3 A/cm 2 和 2.2 × 10 −4 A/cm 2 分别为PDA前后的样品。 PDA后漏电流密度的增加也可归因于栅介质厚度的减小。

Ge 衬底上 HfO2/SiO2 栅极堆叠在 500°C PDA 前后的电特性。 一 高频 (1 M Hz) C-V 曲线。 b J-V曲线

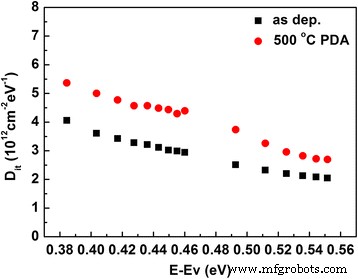

为了定量检测 HfO2/SiO2/Ge 的界面质量,界面态密度 (D 它)是由电导法测定的[31]。图 3 显示了 D 的分布 在室温下通过电导法提取的 Pt/HfO2/SiO2/Ge 在 500°C PDA 前后的带隙中它低于 Ec。 D 它可以从 D 粗略计算 it =2.5 × (G p/w )max/A q, 其中 (G p/w )max 是电导-电压特性的峰值,f (=w /2π) 是频率,A 是电极面积,q 是元素电荷。因此,D 没有和有PDA的Pt/HfO2/SiO2/Ge结构的it值确定为4.05 × 10 12 eV −1 厘米 -2 和 5.37 × 10 12 eV −1 cm −2 分别在 E-Ev =0.38 eV。较低的 D 它的值为 2.03 × 10 12 cm −2 eV −1 和 2.67 × 10 12 cm −2 eV -1 没有和有PDA的样品分别在导带底部附近观察到。

室温下 Pt/HfO2/SiO2/Ge 500 °C PDA 前后带隙中 Dit 低于 Ec 的分布

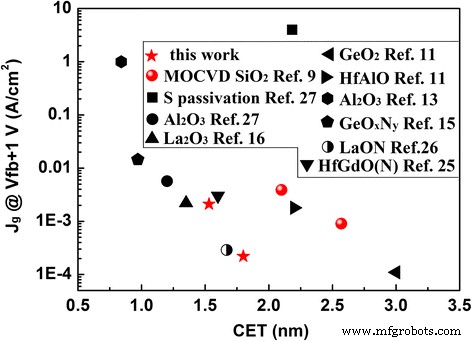

图 4 说明了漏电流密度 (J g)-具有不同界面控制层的Ge基MOS电容器的CET关系[32, 33]。与我们之前的工作 [34] 报道的无中间层的 S 钝化 Ge 相比,这项工作中的 HfO2/SiO2/Ge 表现出大大改善的性能,具有更小的 CET(1.53 对 2.18 nm)、漏电流密度(2.1 × 10 −3 与 3.1 A/cm 2 ) 和 D 它 (4.37 × 10 12 对比 8.61 × 10 12 eV −1 cm −2 )。这意味着原位 PEALD 形成的 SiO2 是一个很好的 Ge 钝化层。此外,与通过 MOCVD [9] 异位形成的 SiO2 夹层相比,本工作中具有原位 PEALD 形成的 SiO2 夹层的样品显示出更好的电性能,具有更小的 CET(1.53 对 1.75 nm)和漏电流密度(2.1与 3.9 mA/cm 2 )。这可以归因于PEALD沉积的SiO2比MOCVD更均匀,尤其是超薄厚度。

不同界面控制层Ge基MOS电容器漏电流密度(Jg)-CET关系

HfO2/SiO2/Ge 界面的能带排列也通过测量价带偏移量 ΔE v 确定 (VBO) 使用 XPS。 VBO 值可以基于以下假设获得,即衬底的核心能级和价带 (VB) 边缘之间的能量差在有/没有电介质膜沉积的情况下保持恒定 [35]。此处,选择 Ge 衬底作为参考以确定栅极电介质堆叠和 Ge 衬底之间的 VBO。图 5a 显示了干净的 Ge 衬底、沉积态和退火态 HfO2/SiO2/Ge 叠层的 VB 谱,分别通过线性外推法确定。干净的 Ge 衬底的 VB 边缘已确定为 0.10 eV。并且,发现沉积态和退火态 HfO2/SiO2 样品的 VB 边缘分别为 2.55 和 2.79 eV。可以注意到,HfO2/SiO2/Ge 叠层的 VB 光谱有一个小尾巴,它对应于 Ge 衬底信号 [36]。该弱尾部的前沿测量为 0.10 eV,与 Ge 衬底的 VB 边缘相同。因此,在有和没有 PDA 的情况下,HfO2/SiO2/Ge 界面处的 VBO 估计分别为 2.69 和 2.45 eV。导带偏移ΔE c (CBO) 可以用HfO2的带隙减去VBO和衬底的带隙得到:

Ge 上沉积和退火的 HfO2/SiO2 膜的能带排列。 一 Ge 衬底、沉积和退火的 HfO2/SiO2 薄膜的价带光谱。 b Ge上沉积和退火的HfO2/SiO2薄膜能带排列示意图

$$ \varDelta {E}_c={E}_g\left({\mathrm{HfO}}_2\right) - {E}_g\left(\mathrm{Ge}\right) - \varDelta {E}_v , $$其中 E g (HfO2) 和 E g (Ge) 分别是 HfO2 和 Ge 的带隙。 Ge 和 HfO2 的带隙分别为 0.67 和 5.6 eV。因此,在有和没有 PDA 的情况下,HfO2/SiO2/Ge 界面处的 CBO 值估计分别为 2.24 和 2.48 eV。 CBO 值与之前报告的 1.8-2.6 eV 数据一致 [37]。图 5b 说明了沉积和退火的 HfO2/SiO2/Ge 结构的相应能带排列。显然,Ge上的HfO2/SiO2高k栅介质堆叠表现出较大的VBO和CBO值,具有巨大的势垒高度来抑制漏电流。

结论

总之,通过原位 PEALD 成功地将 SiO2 中间层引入 n-Ge 衬底上的 HfO2 栅极电介质中。我们研究了 HfO2/SiO2/Ge MOS 的界面、电学特性和能带排列。已经证明在原位SiO2沉积过程中在Ge表面形成Ge-O-Si中间层和GeO2层。这种 Ge-O-Si 夹层在 PDA 过程中表现出极好的热稳定性,而不会形成 Hf-硅酸盐。此外,Ge-O-Si中间层还可以抑制退火过程中GeO2的降解。 PDA 后的 HfO2/SiO2/Ge 样品的 CET 值为 1.53 nm,漏电流密度低,为 2.1 × 10 -3 A/cm 2 在 Vfb + 1 V。在有和没有 PDA 的情况下,HfO2/SiO2/Ge 处的 VBO 值确定为 2.69 和 2.45 eV,CBO 值分别为 2.24 和 2.48 eV。与通过 MOCVD 异位形成的 SiO2 夹层相比,本工作中具有原位 PEALD 形成的 SiO2 夹层的样品显示出改善的电性能,这归因于通过 PEALD 沉积的 SiO2 比 MOCVD 更均匀的事实。因此,PEALD是一种比MOCVD更强大的超薄界面控制层沉积技术。

纳米材料

- 用于 Micro-LED 和 VCSEL 的高级原子层沉积技术

- 具有自整流开关特性的 TaO/HfO x 和 TaO/AlO x RRAM 的保持模型

- HfO2/TiO2/HfO2 三层结构 RRAM 器件在原子层沉积制备的 Pt 和 TiN 涂层衬底上的双极电阻开关特性

- 化学蚀刻制备的硅纳米线的光学和电学特性

- 通过原子层沉积和水热生长制备的抗菌聚酰胺 6-ZnO 分层纳米纤维

- 通过等离子体增强原子层沉积制备的 Co3O4 涂层 TiO2 粉末的光催化性能

- 具有电场辅助纳米碳填料排列的复合材料的电性能

- 通过界面层设计调整 ZnO 薄膜的表面形貌和特性

- 通过超循环原子层沉积调节 ZnO 薄膜的费米能级

- 在 c 面 GaN 上沉积的 AlN 原子层中界面和电特性的厚度依赖性

- 蚀刻变化对 Ge/Si 沟道形成和器件性能的影响

- Au/SiO2 三角形阵列在反射 Au 层上的光学特性和传感性能